Изобретение относится к вычислительной технике и может быть использовано в системах контроля работоспособности и поиска неисправностей логических блоков.

Цель изобретения - повышение достоверности контроля.

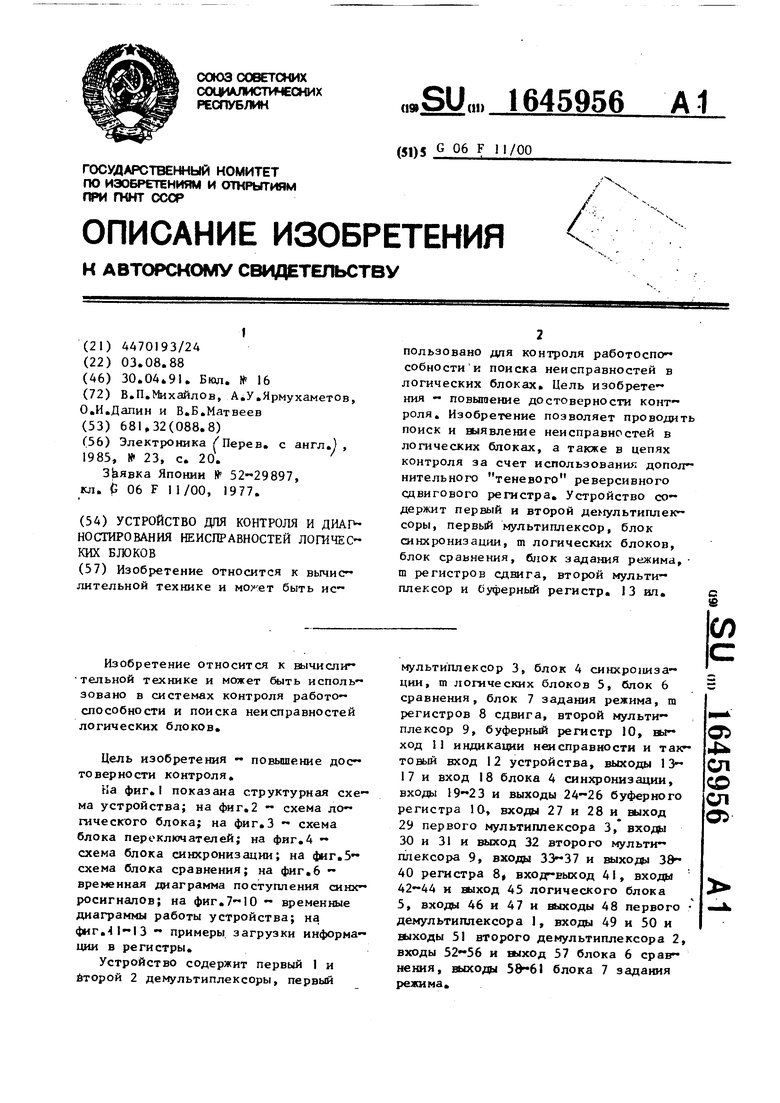

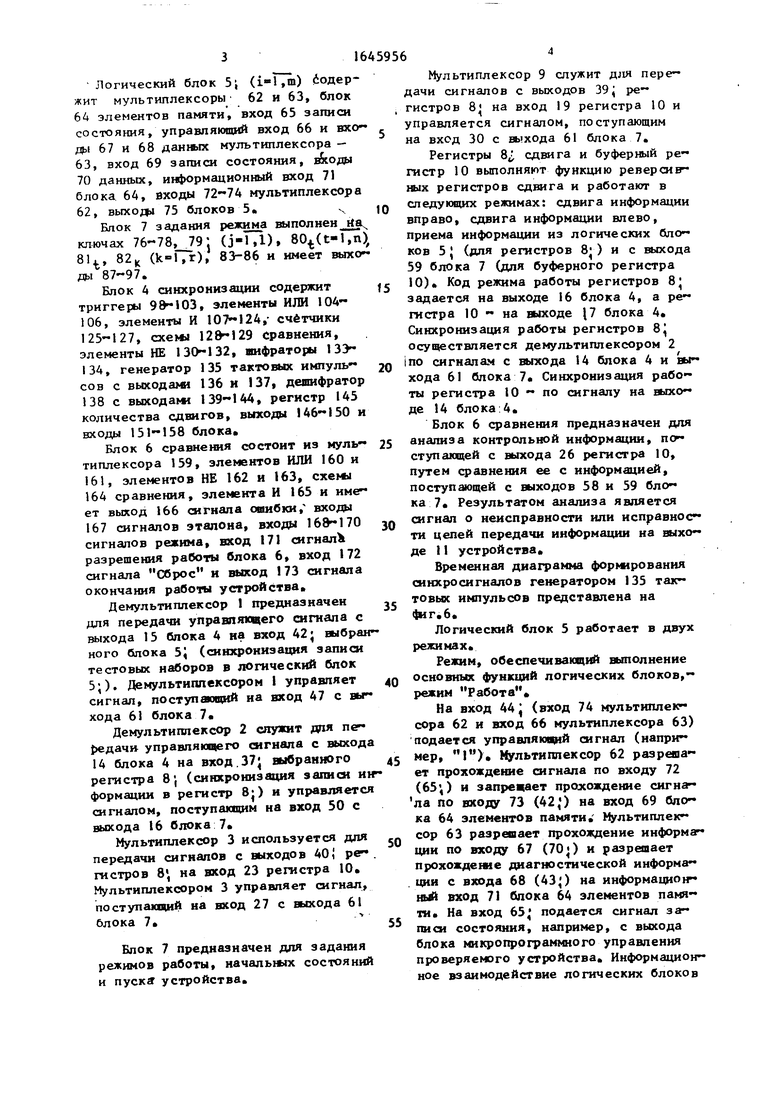

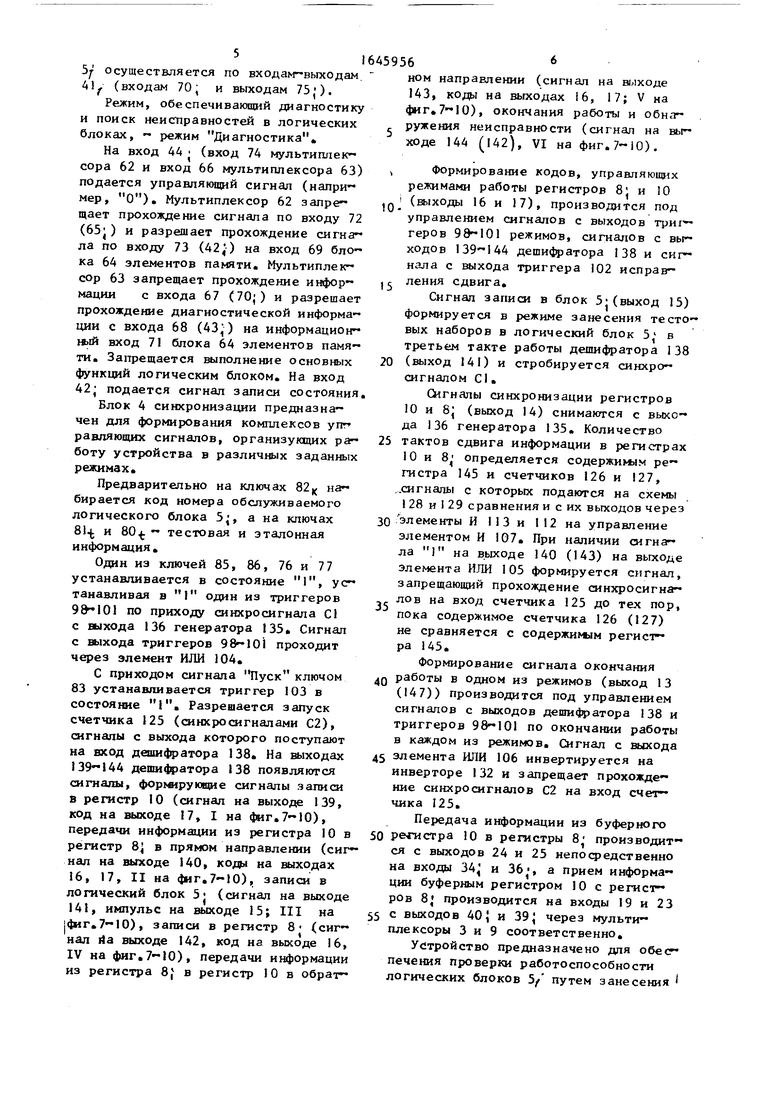

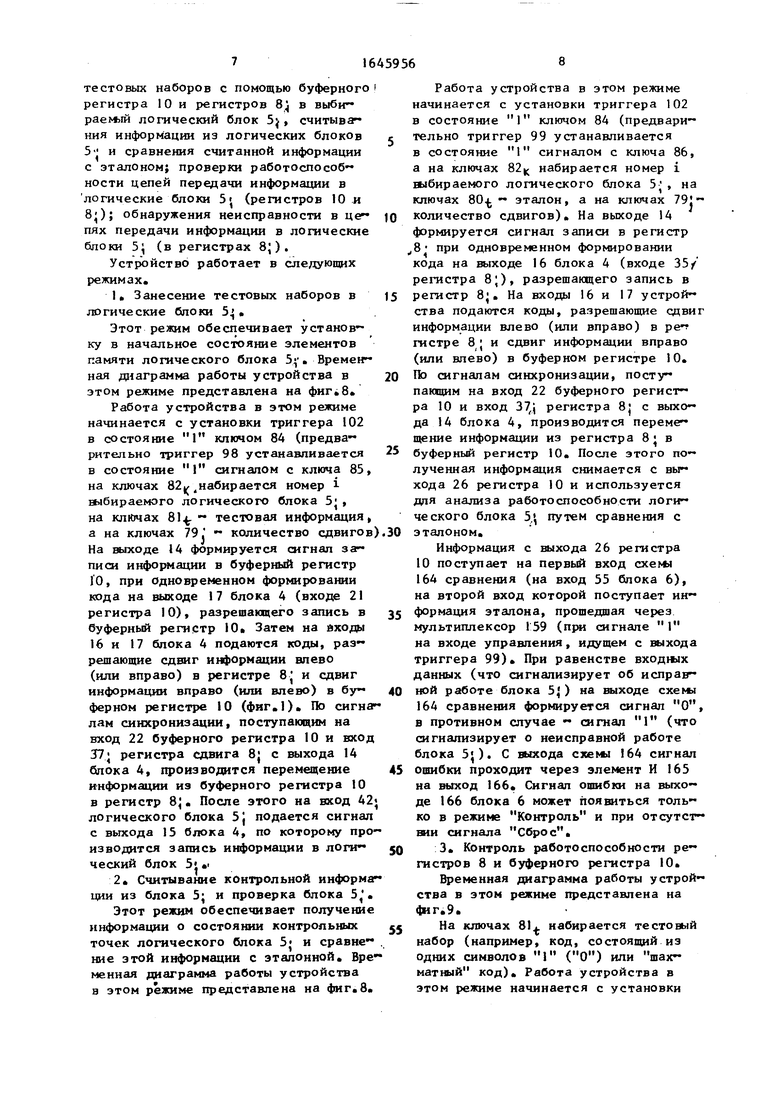

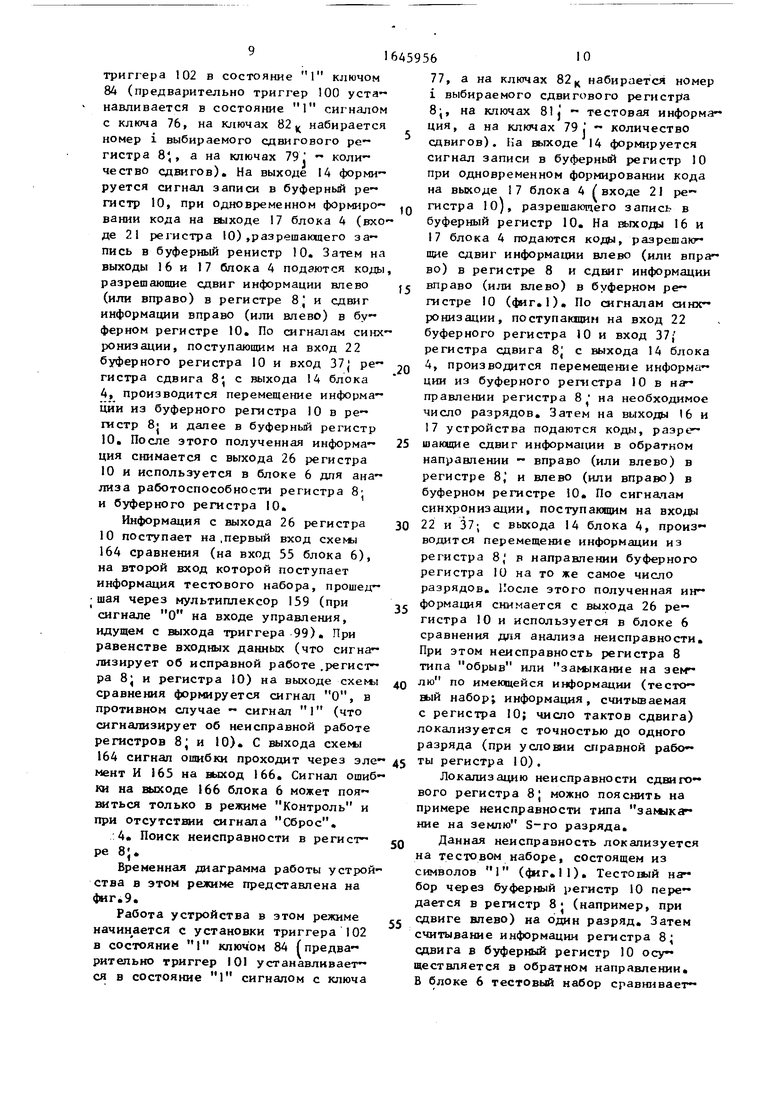

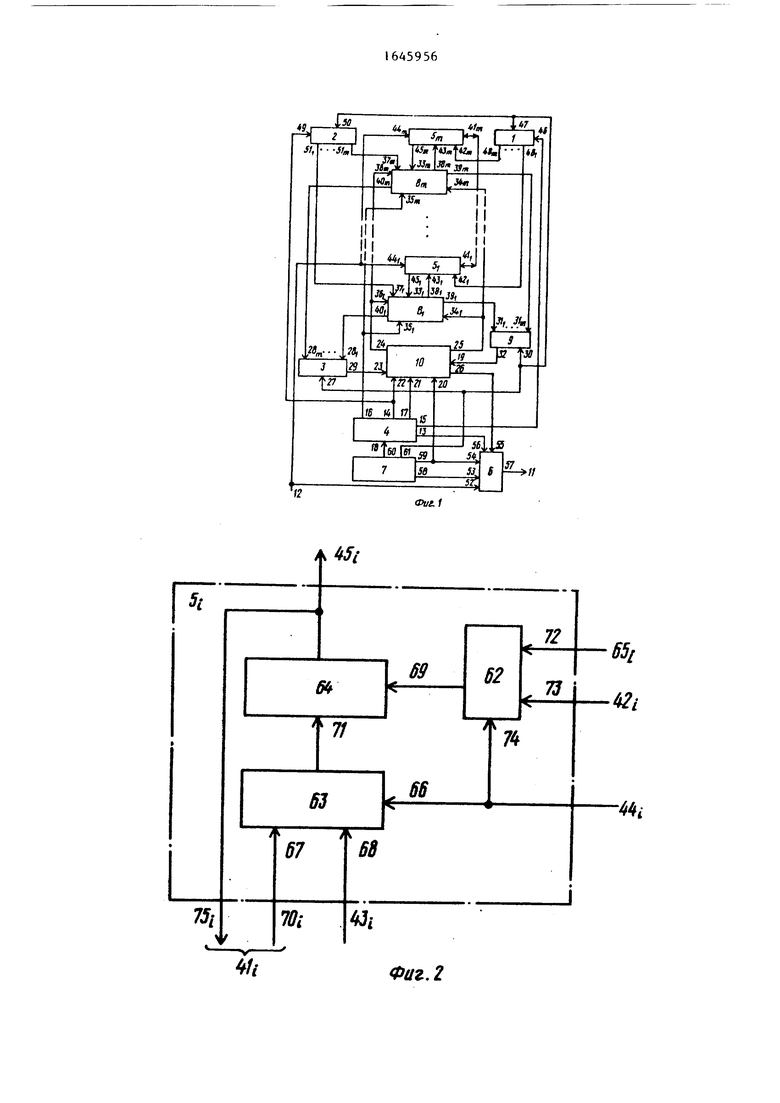

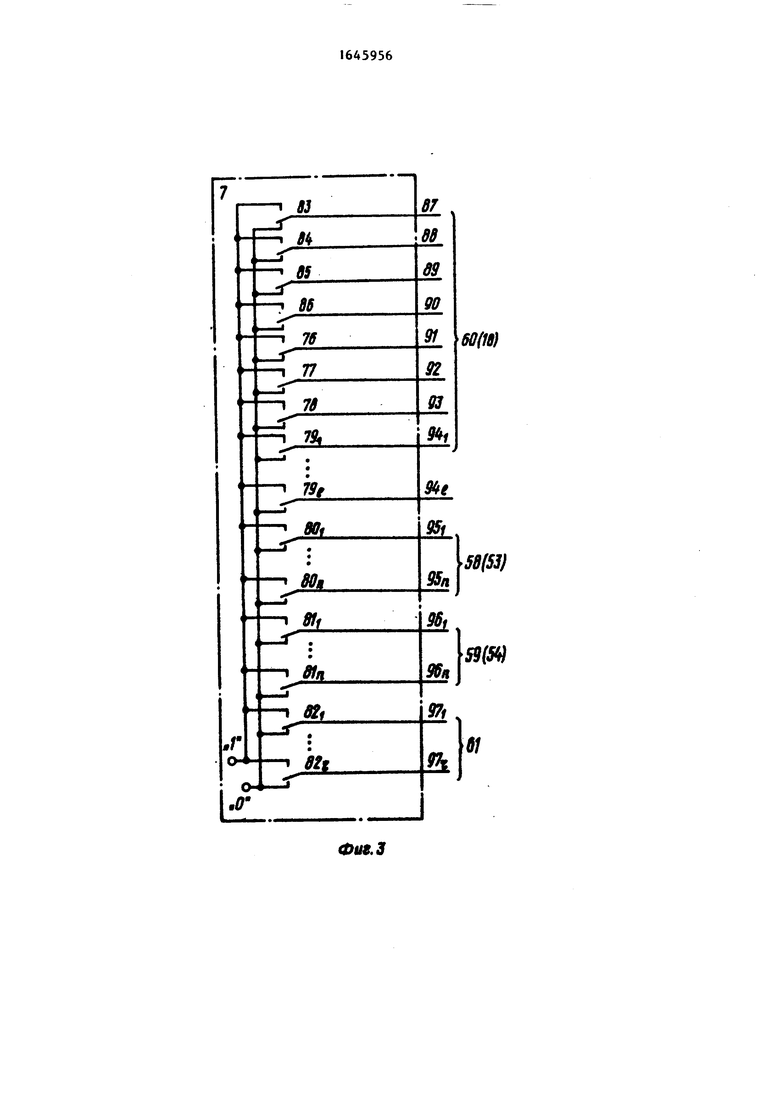

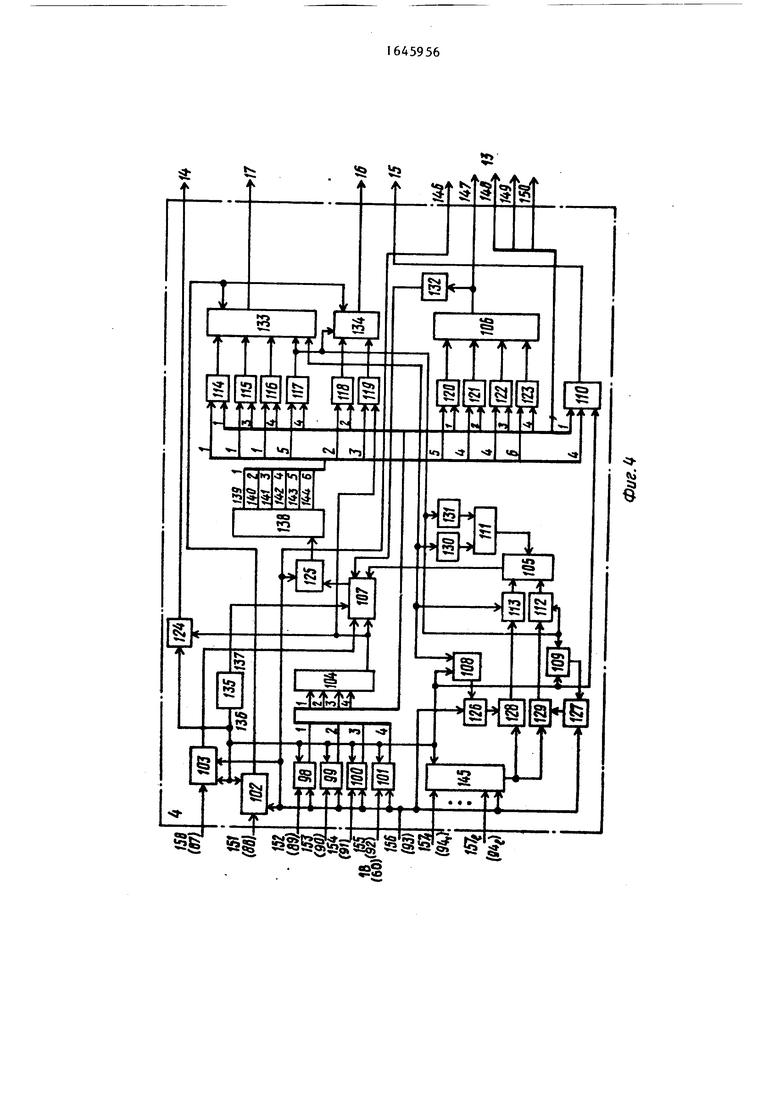

На фиг.I показана структурная схема устройства; на фиг.2 - схема логического блока; на фиг.З схема блока переключателей; на фиг.4 - схема блока синхронизации; на фиг. 5- схема блока сравнения; на фиг.6 - временная диаграмма поступления синхросигналов; на фиг.7-10 - временные диаграммы работы устройства; на фиг.41-13 - примеры загрузки информации в регистры.

Устройство содержит первый 1 и второй 2 демультиплексоры, первый

мультиплексор 3, блок 4 синхронизации, m логических блоков 5, блок 6 сравнения, блок 7 задания режима, m регистров 8 сдвига, второй мультиплексор 9, буферный регистр 10, выход 11 индикации неисправности и тактовый вход 12 устройства, выходы 13- 17 и вход 18 блока 4 синхронизации, входы 19-23 и выходы 24-26 буферного регистра 10, входы 27 и 28 и выход

29первого мультиплексора 3, входы

30и 31 и выход 32 второго мультиплексора 9, входы 33-37 и выходы 40 регистра 8 вход-выход 41, входы 42-44 и выход 45 логического блока

.

5, входы 46 и 47 и выходы 48 первого демультиплексора 1, входы 49 и 50 и выходы 51 второго демультиплексора 2, входы 52-56 и выход 57 блока 6 сравнения, выходы 58-61 блока 7 задания режима.

0 4ь

сл

со ел

О5

Логический блок 5i (iel,m) содер- жит мультиплексоры 62 и 63, блок 64 элементов памяти, вход 65 записи состояния, управляющий вход 66 и вхо- да 67 и 68 данных мультиплексора - 63, вход 69 записи состояния, входы 70 данных, информационный вход 71 блока 64, входы 72-74 мультиплексора 62, выхода 75 блоков 5.v

Елок 7 задания режима выполнен на, ключах ,79; (j-1,1), .n), 8Ц, 82К (,r), 83-86 и имеет выхода 87-97.

Блок 4 синхронизации содержит

триггеры 98-103, элементы ИЛИ 104- 106, элементы И 107-124,- счетчики 125-127, схемы 128-129 Сравнения, элементы НЕ 130-132, шифраторы 133- 134, генератор 135 тактовых импуль- сов с выходами 136 и 137, дешифратор 138 с выходами 139-144, регистр 145 количества сдвигов, выходы 146-150 и входы 151-158 блока,

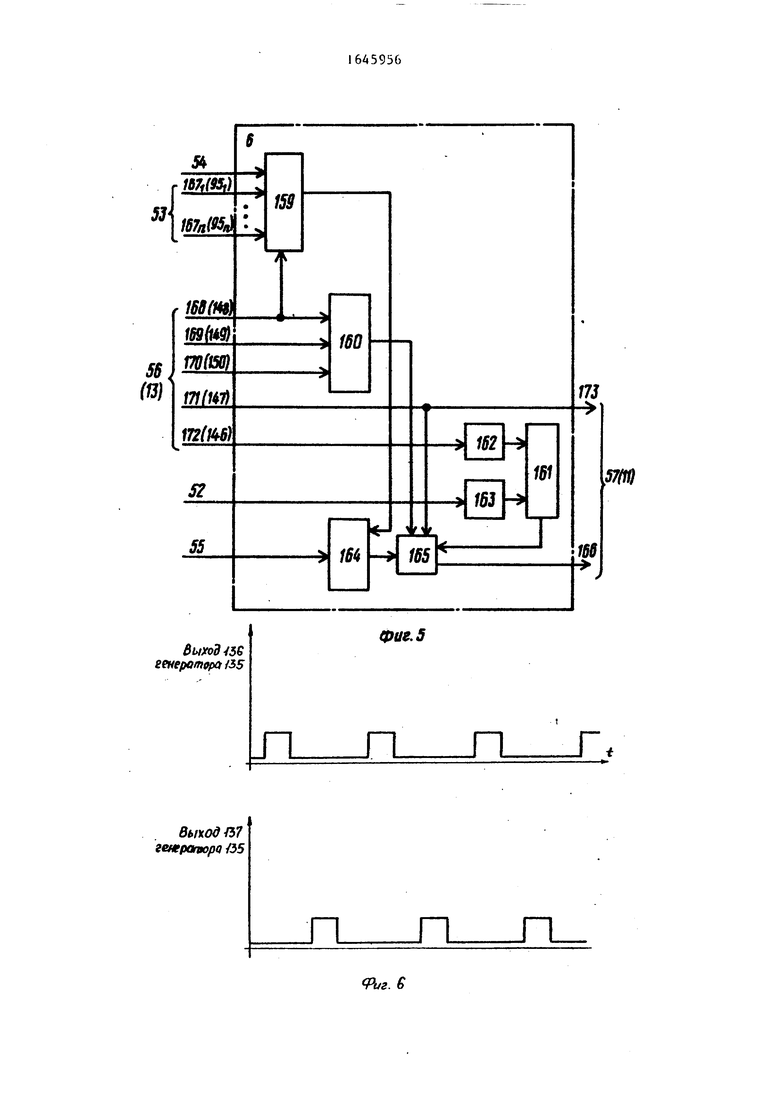

Блок 6 сравнения состоит из муль- типлексора 159, элементов ИЛИ 160 и 161, элементов НЕ 162 и 163, схемы 164 сравнения, элемента И 165 и имеет выход 166 сигнала ошибки/ входы 167 сигналов эталона, входы 168-170 сигналов режима, вход 171 сигнала разрешения работы блока 6, вход 172 сигнала Сброс и выход 173 сигнала окончания работы устройства.

Демультиплексор 1 предназначен

для передачи управляющего сигнала с выхода 15 блока 4 на вход 42; выбранного блока 5 (синхронизация записи тестовых наборов в логический блок 5;). Демультиплексором I управляет сигнал, поступающий на вход 47 с выхода 61 блока 7.

Демультиплексор 2 служит для передачи управляющего сигнала с выхода 14 блока 4 на вход.37; выбранного регистра 8, (синхронизация записи информации в регистр 8;) и управляется сигналом, поступающим на вход 50 с выхода 16 блока 7.

Мультиплексор 3 используется для передачи сигналов с выходов 40j ре-, гистров 8 на вход 23 регистра 10. Мультиплексором 3 управляет сигнал, поступающий на вход 27 с выхода 61 блока 7.

Блок 7 предназначен для задания режимов работы, начальных состояний и пуска устройства.

Мультиплексор 9 служит для передачи сигналов с выходов 39 ре- гистров 8« на вход 19 регистра 10 и управляется сигналом, поступающим на вход 30 с выхода 61 блока 7.

Регистры сдвига и буферный регистр 10 выполняют функцию реверсивных регистров сдвига и работают в следующих режимах: сдвига информации вправо, сдвига информации влево, приема информации из логических блоков 5 { (для регистров 8; ) и с выхода 59 блока 7 (для буферного регистра 10). Код режима работы регистров 8 задается на выходе 16 блока 4, а регистра 10 - на выходе {7 блока 4. Синхронизация работы регистров 8} осуществляется демультиплексором 2 о сигналам с выхода 14 блока 4 и выхода 61 блока 7. Синхронизация работы регистра 10 - по сигналу на выходе 14 блока 4.

Блок 6 сравнения предназначен для анализа контрольной информации, поступающей с выхода 26 регистра 10, путем сравнения ее с информацией, поступающей с выходов 58 и 59 блока 7. Результатом анализа является сигнал о неисправности или исправности цепей передачи информации на выходе 11 устройства.

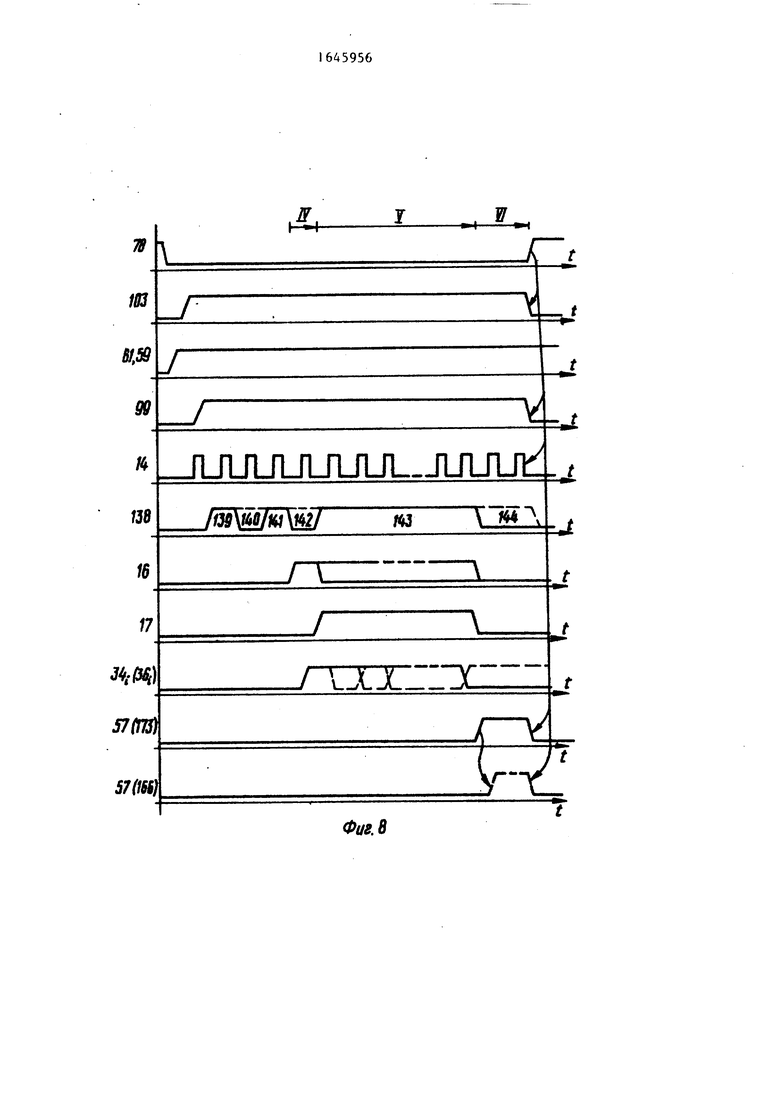

Временная диаграмма формирования синхросигналов генератором 135 тактовых импульсов представлена на фиг.6.

Логический блок 5 работает в двух режимах.

Режим, обеспечивающий выполнение основных функций логических блоков,- режим Работа.

На вход 44j (вход 74 мультиплексора 62 и вход 66 мультиплексора 63) подается управляющий сигнал (например, Iм). Мультиплексор 62 разрешает прохождение сигнала по входу 72 (65) и запрещает прохождение сигна- ла по входу 73 (42,) на вход 69 блока 64 элементов памяти. Мультиплексор 63 разрешает прохождение информации по входу 67 (70) и разрешает прохождение диагностической информации с входа 68 (43;) на информационный вход 71 блока 64 элементов памяти. На вход 65, подается сигнал записи состояния, например, с выхода блока микропрограммного управления проверяемого устройства. Информационное взаимодействие логических блоков

5f осуществляется по входам-выходам 41. (входам 70; и выходам 75j).

Режим, обеспечивающий диагностику и поиск неисправностей в логических блоках, - режим Диагностика

На вход 44 (вход 74 мультиплексора 62 и вход 66 мультиплексора 63) подается управляющий сигнал (напри- мер, О). Мультиплексор 62 запре- щает прохождение сигнала по входу 72 (651 ) и разрешает прохождение сигна- ла по входу 73 (42j) на вход 69 блока 64 элементов памяти. Мультиплексор 63 запрещает прохождение информации с входа 67 (70j) и разрешает прохождение диагностической информации с входа 68 (43) на информационный вход 71 блока 64 элементов памяти. Запрещается выполнение основных функций логическим блоком. На вход 42| подается сигнал записи состояния

Блок 4 синхронизации предназначен для формирования комплексов упг равляющих сигналов, организующих работу устройства в различных заданных режимах.

Предварительно на ключах 82 к набирается код номера обслуживаемого логического блока 5;, а на ключах 8Ц и 80 - тестовая и эталонная информация.

Один из ключей 85, 86, 76 и 77 устанавливается в состояние 1, устанавливал в 1 один из триггеров 98 101 по приходу синхросигнала С1 с выхода 136 генератора 135. Сигнал с выхода триггеров 98-101 проходит через элемент ИЛИ 104.

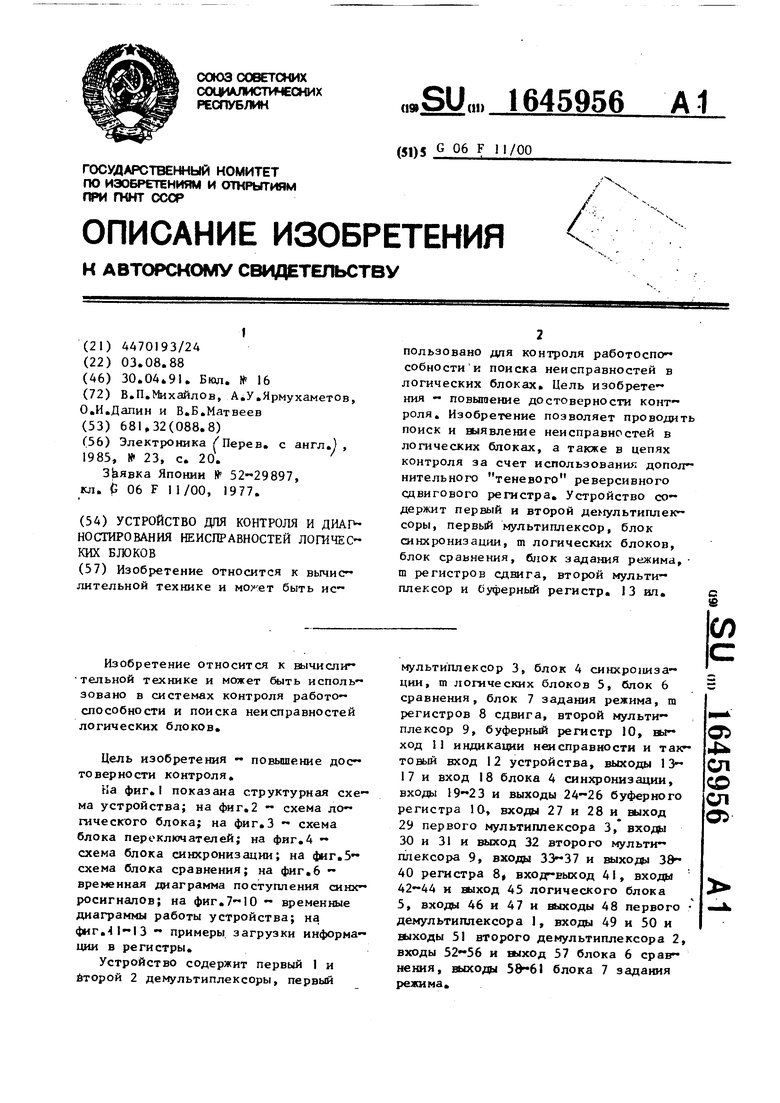

С приходом сигнала Пуск ключом 83 устанавливается триггер 103 в состояние I. Разрешается запуск счетчика 125 (синхросигналами С2), сигналы с выхода которого поступают на вход дешифратора 138. На выходах 139-144 дешифратора 138 появляются сигналы, формирующие сигналы записи в регистр 10 (сигнал на выходе 139, код на выходе 17, I на фиг.7-10), передачи информации из регистра 10 в регистр 8 в прямом направлении (сигнал на выходе 140, коды на выходах 16, 17, II на фиг.7-10), записи в логический блок 5- (сигнал на выходе 141, импульс на выходе 15; III на 1ФИГ.7-10), записи в регистр 8- (сигнал на выходе 142, код на выходе 16, IV на фиг.7-10), передачи информации из регистра 8f в регистр 10 в обрат-

0

5

0

ном направлении (сигнал на выходе 143, коды на выходах 16, 17; V на фиг.7-10), окончания работы и обнаружения неисправности (сигнал на выходе 144 (142), VI нафиг.7-10).

формирование кодов, управляющих режимами работы регистров 81 и 10 1 (выходы 16 и 17), производится под управлением сигналов с выходов триггеров 98-101 режимов, сигналов с выходов 139-144 дешифратора 138 и сигнала с выхода триггера 102 исправления сдвига.

Сигнал записи в блок 5-(выход 15) формируется в режиме занесения тестовых наборов в логический блок 5,1 в третьем такте работы дешифратора 138 (выход 141) и стробируется синхросигналом CI .

Сигналы синхронизации регистров 10 и 8j (выход 14) снимаются с выхода 136 генератора 135. Количество 5 тактов сдвига информации в регистрах 10 и определяется содержимым регистра 145 и счетчиков 126 и 127, .сигналы с которых подаются на схемы

1 28 и I 29 сравнения и с их выходов через 0 элементы И 113 и 112 на управление элементом И 107. При наличии сигнала 1 на выходе 140 (143) на выходе элемента ИЛИ 105 формируется сигнал, запрещающий прохождение синхросигналов на вход счетчика 125 до тех пор, пока содержимое счетчика 126 (127) не сравняется с содержимым регистра 145.

Формирование сигнала окончания 0 работы в одном из режимов (выход 13 (147)) производится под управлением сигналов с выходов дешифратора 138 и триггеров 98-101 по окончании работы в каждом из режимов. Сигнал с выхода 5 элемента ИЛИ 106 инвертируется на инверторе 132 и запрещает прохождение синхросигналов С2 на вход счетчика 125.

Передача информации из буферного 0 регистра 10 в регистры 8- производится с выходов 24 и 25 непосредственно на входы 34, и 36, а прием информации буферным регистром 10 с регистров 8, производится на входы 19 и 23 5 с выходов 40{ и 39{ через мультиплексоры 3 и 9 соответственно.

Устройство предназначено для обеспечения проверки работоспособности логических блоков 5/ путем занесения

5

тестовых наборов с помощью буферного регистра 10 и регистров 8} в выбираемый логический блок 5}, считывания информации из логических блоков 5- и сравнения считанной информации с эталоном; проверки работоспособности цепей передачи информации в логические блоки 5 (регистров 10 и 8,|); обнаружения неисправности в це- гшх передачи информации в логические блоки 5; (в регистрах 8;).

Устройство работает в следующих режимах.

1 Занесение тестовых наборов в логические блоки 5.J

Этот режим обеспечивает установку в начальное состояние элементов памяти логического блока 5у. Временная диаграмма работы устройства в этом режиме представлена на фиг.8. Работа устройства в этом режиме начинается с установки триггера 102 в состояние 1 ключом 84 (предварительно триггер 98 устанавливается в состояние 1 сигналом с ключа 85, на ключах 82 tнабирается номер i выбираемого логического блока 5j, на ключах 81.- тестовая информация, а на ключах 79. - количество сдвигов На выходе 14 формируется сигнал записи информации в буферный регистр 10, при одновременном формировании кода на выходе 17 блока 4 (входе 21 регистра 10), разрешающего запись в буферный регистр 10. Затем на входы 16 и 17 блока 4 подаются коды, разрешающие сдвиг информации влево (или вправо) в регистре 8| и сдвиг информации вправо (или влево) в бу- ферном регистре 10 (фиг.1). По сигналам синхронизации, поступающим на вход 22 буферного регистра 10 и вход 37; регистра сдвига 8j с выхода 14 блока 4, производится перемещение

информации из буферного регистра 10 в регистр 8{ После этого на вход 42 логического блока 5J подается сигнал с выхода 15 блока 4, по которому производится запись информации в логи- ческий блок 5.

2. Считывание контрольной информации из блока 5; и проверка блока 5,. Этот режим обеспечивает получение информации о состоянии контрольных точек логического блока 5j и сравне- ние этой информации с эталонной. Временная диаграмма работы устройства в этом режиме представлена на фиг.8.

Работа устройства в этом режиме начинается с установки триггера 102 в состояние 1 ключом 84 (предварительно триггер 99 устанавливается в состояние 1 сигналом с ключа 86, а на ключах 82К набирается номер i выбираемого логического блока 5 , на ключах 80.J. - эталон, а на ключах 79 количество сдвигов). На выходе 14 формируется сигнал записи в регистр 8 при одновременном формировании кода на выходе 16 блока 4 (входе 35/ регистра 8|), разрешающего запись в регистр 8j. На входы 16 и 17 устройства подаются коды, разрешающие сдви информации влево (или вправо) в per гистре 8; и сдвиг информации вправо (или влево) в буферном регистре 10. По сигналам синхронизации, поступающим на вход 22 буферного регистра 10 и вход 37,j регистра 8j с выхода 14 блока 4, производится перемещение информации из регистра 8 в буферный регистр 10. После этого полученная информация снимается с выхода 26 регистра 10 и используется для анализа работоспособности логического блока 5,1, путем сравнения с эталоном.

Информация с выхода 26 регистра 10 поступает на первый вход схемы 164 сравнения (на вход 55 блока 6), на второй вход которой поступает информация эталона, прошедшая через мультиплексор 159 (при сигнале 1 на входе управления, идущем с выхода триггера 99). При равенстве входных данных (что сигнализирует об исправной работе блока 5{ ) на выходе схемы 164 сравнения формируется сигнал О в противном случае - сигнал 1 (что сигнализирует о неисправной работе блока 5{). С выхода схемы 164 сигнал ошибки проходит через элемент И 165 на выход 166. Сигнал ошибки на выходе 166 блока 6 может появиться только в режиме Контроль и при отсутствии сигнала Сброс.

3. Контроль работоспособности регистров 8 и буферного регистра 10.

Временная диаграмма работы устройства в этом режиме представлена на фиг.9.

На ключах 81. набирается тестовый набор (например, код, состоящий из одних символов 1 (О) или шахматный код). Работа устройства в этом режиме начинается с установки

триггера 102 в состояние 1 ключом 84 (предварительно триггер 100 уста- навливается в состояние 1 сигналом с ключа 76, на ключах 82 набирается номер i выбираемого сдвигового ре- гистра 8;, а на ключах 79j - коли- чество сдвигов). На выходе 14 форми- руется сигнал записи в буферный регистр 10, при одновременном формиро- вании кода на выходе 17 блока 4 (вхо1 де 21 регистра 10) .разрешающего за- пись в буферный ренистр 10. Затем на выходы 16 и 17 блока 4 подаются коды разрешающие сдвиг информации влево (или вправо) в регистре 8 и сдвиг информации вправо (или влево) в буферном регистре 10. По сигналам синхс ронизации, поступающим на вход 22 буферного регистра 10 и вход 37 j регистра сдвига 8, с выхода 14 блока 4, производится перемещение информации из буферного регистра 10 в регистр 8j и далее в буферный регистр 10. После этого полученная информация снимается с выхода 26 регистра 10 и используется в блоке 6 для анализа работоспособности регистра 8 и буферного регистра 10.

Информация с выхода 26 регистра 10 поступает на .первый вход схемы 164 сравнения (на вход 55 блока 6), на второй вход которой поступает информация тестового набора, прошедшая через мультиплексор 159 (при сигнале О на входе управления, идущем с выхода триггера 99). При равенстве входных данных (что сигнализирует об исправной работе .регистра 8j и регистра 10) на выходе схемы сравнения формируется сигнал О, в противном случае - сигнал 1 (что сигнализирует об неисправной работе регистров 8; и 10). С выхода схемы 164 сигнал ошибки проходит через элемент И 165 на выход 166. Сигнал ошибки на выходе 166 блока 6 может появиться только в режиме Контроль и при отсутствии сигнала Сброс,

4. Поиск неисправности в регистре 8;.

Временная диаграмма работы устройства в этом режиме представлена на фиг.9.

Работа устройства в этом режиме начинается с установки триггера 102 в состояние 1 ключом 84 (предварительно триггер 101 устанавливается в состояние 1 сигналом с ключа

45956|0

77, а на ключах 82к набирается номер i выбираемого сдвигового регистра 8, на ключах 81 j - тестовая информация, а на ключах 79. - количество сдвигов). На выходе 14 формируется сигнал записи в буферный регистр 10 при одновременном формировании кода на выходе 17 блока 4 (входе 21 ре.Q гистра 10), разрешающего запись в буферный регистр 10. На выходы 16 и 17 блока 4 подаются коды, разрешающие сдвиг информации влево (или впра- во) в регистре 8 и сдвиг информации

jc вправо (или влево) в буферном регистре 10 (фиг.1). По сигналам синхронизации, поступающим на вход 22 буферного регистра 10 и вход 37; регистра сдвига 8j с выхода 14 блока

20 4 производится перемещение информации из буферного регистра 10 в направлении регистра 8 на необходимое число разрядов. Затем на выходы 16 и 17 устройства подаются коды, раэре-

25 шающие сдвиг информации в обратном направлении - вправо (или влево) в регистре 8, и влево (или вправо) в буферном регистре 10. По сигнапам синхронизации, поступающим на входы

30 22 и 37; с выхода 14 блока 4, производится перемещение информации из регистра 8, в направлении буферного регистра 10 на то же самое число разрядов. После этого полученная ин-

,, формация снимается с выхода 26 регистра 10 и используется в блоке 6 сравнения для анализа неисправности. При этом неисправность регистра 8 типа обрыв или замыкание на зем-

4Q лк по имеющейся информации (тестовый набор; информация, считываемая с регистра 10; число тактов сдвига) локализуется с точностью до одного разряда (при условии справной рабо- 45 ты регистра 10).

Локализацию неисправности сдвиго вого регистра 8| можно пояснить на примере неисправности типа замыкание на землю S-ro разряда.

JQДанная неисправность локализуется

на тестовом наборе, состоящем из символов 1 (фиг.11). Тестовый набор через буферный регистр 10 передается в регистр 8« (например, при

ее сдвиге влево) на один разряд. Затем считывание информации регистра 8; сдвига в буферный регистр 10 осу- ществляется в обратном направлении. В блоке 6 тестовый набор сравнивает-

ся со снятой информацией. Сигнал неисправности не вырабатывается (не исправность в S-M разряде).

Работа в данном режиме повторяет ся еще несколько раз. Количество сдви. гов информации каждый раз увеличивается на единицу. После передачи информации в регистр 8{ из регистра 10 (при количестве сдвигов, равном S) значение разрядов регистра 8, изображено на фиг.12. После считывания информации из регистра 8 в регистр 10 значение разрядов регистра 10 изображено на фиг.13. В блоке 6 тестовый набор сравнивается с полученной информацией. Так как тестовый-набор v полученная информация не совпадают, то вырабатывается сигнал неисправности, сигнализирующий о неисправности 1-го разряда регистра 8; .

При более сложной реализации блока 6 сравнения возможно выявление неисправностей также и в регистре 10.

Формула изобретения

Устройство для контроля и диагнос тирования неисправностей логических блоков, содержащее первый и второй демультиплексоры, первый мультиплексор, блок синхронизации, блок зада- ния режима и блок сравнения, выход которого является выходом индикации устройства, а первый и второй информационные входы блока сравнения соединены соответственно с первым и вторым выходами блока задания режима, третий и четвертый выходы которого подключены соответственно к входу запуска блока синхронизации и управляющим входам первого и второго демультиплексоров и первого мультиплексора, с первого по третий выходы блока синхронизации соединены с первым синхровходом блока сравнения и информационными входами первого и второго демультиплексоров соответственно, информационные выходы первого демультиплексора являются выходами устройства для подключения к входам режима одноименных контро-

Q 0

5

30

35

40

45

50

лируемых логических блоков, а второй синхровход блока сравнения подключен к синхровходу устройства и является синхровходом контролируемых логических блоков, отличающее ся тем, что, с целью повышения достоверности контроля, оно содержит m регистров сдвига по числу проверяемых логических блоков, буферный регистр и второй мультиплексор, управляющий вход которого соединен с четвертым выходом блока задания режима, аыход второго мультиплексора подклкг чен к первому информационному входу буферного регистра, информационные входы второго мультиплексора соединены с первыми информационными выходами одноименных регистров сдвига, первые информационные входы которых подключены к первому информационному выходу буферного регистра, вторые информационные входы регистров сдвига соединены с вторым информационным выходом буферного регистра, вторые информационные выходы регистров сдвига подключены к одноименным информационным входам первого мультиплексора, выход которого соединен с вторым информационным входом буферного регистра, информационные выходы второго демультиплексора подключены к синхровходам Одноименных регистров сдвига, третьи информационные входы и выходы регистров сдвига являются соответственно входами и выходами устройства для подключения к информационным выходам и входам одноименных контролируемых логических блоков, синхровход буферного регистра соединен с третьим выходом блока синхронизации, второй выход блока задания режима подключен к входу начальной установки буферного регистра, четвертый и пятый выходы блока синхронизации соединены соответственно с входами режима регистров сдвига и входом режима буферного регистра, третий информационный выход которого подключен к третьему информационному входу блока сравнения

3

Я

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

Изобретение относится к вычислительной технике и мо)ет быть использовано для контроля работоспособности и поиска неисправностей в логических блоках. Цель изобретения - повышение достоверности контроля. Изобретение позволяет проводить поиск и выявление неисправностей в логических блоках, а также в цепях контроля за счет использования дополнительного теневого реверсивного сдвигового регистра. Устройство содержит первый и второй демультиплек- соры, первый мультиплексор, блок синхронизации, m логических блоков, блок сравнения, блок задания режима, m регистров сдвига, второй мультиплексор и буферный регистр. 13 ил. в

3

S3

§5

I

Na

§

t:

& & 01

VO

ьл (T

J

&J Na

$

Г

.0

Фиг.З

61

о ю а

iTl

t

vO

№

ЯГ

f

5) /

Выход Ш генератора /35

п п п г.

Выход У37 генграпюро #5

п п п

Фаг. 5

Я/г. В

-t

t

JUUUUL JUUUULJ1 r

/W Wf Л

/

/miiijoc:

П

/7

#

-t

t

/W Wf Л

П

Фиг. 7

s.

Фаг. В

I

V

I . S

направлен ив сдбигв 8 регистре 10 при загрузке регистров

Фиг. 11

Ш1

И И

1

n-f

S-1 S

направление сддиеа в регистре 8 при ко загрузке

Фаг. 12

01s-f $ 1я-1 я

- напрадление сдбига в регистре ю при считывании регистра 8

Фиг. 13

MiJ

n-f п

| Электроника ( Перев | |||

| с англ.) , 1985, 23, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-30—Публикация

1988-08-03—Подача