1

(21)4722057/24

(22)24.07.89

(46) 30.04.91. Бюл. И- 16 (72) А.Л.Альбов и А.И.Грибков

(53)681.327.6(088.8)

(56)Авторское свидетельство СССР f 905858, кл. G 11 С 17/00, 1981.

Авторское свидетельство СССР 746730, кл. G 11 С 17/00, 1978

(54)ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57)Изобретение относится к автоматике и вычислительной технике и

предназначено для построения постоянных запоминающих устройств с малой потребляемой мощностью. Целью изобретения является уменьшение потребляемой мощности и повышение быстродействия постоянного запоминающего устройства. Поставленная цель достигается тем, что устройство содержит селектор 8 адреса, блок 9 управления, формирователь 10 разрядного тока, блоки 11 согласования нагрузки с соответс-, вующими связями. Введение селектора 8 адреса и блока 9 управления позволяет значительно

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746730A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU970462A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746731A1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

2

СЛ

со

уменьшить потребляемую постоянмнм запоминающим устройством мощность за счет того, что напряжение питания подается только на тот запоминающий модуль 4, из которого считывается информация, и только на то время, которое необходимо для выборк из него данных. Ьведние формирователя 10 разрядного тока позволяет дополнительно уменьшить длительность импульса напряжения, питания на запоминающем модуле А за счет ускореИзобретение относится к автоматике и вычислительной технике и предназначено для построения постоянных запоминающих устройств с малой потребляемой мощностью.

Целью изобретения является уменьшение потребляемой мощности и повышение быстродействия постоянного запоминающего устройства.

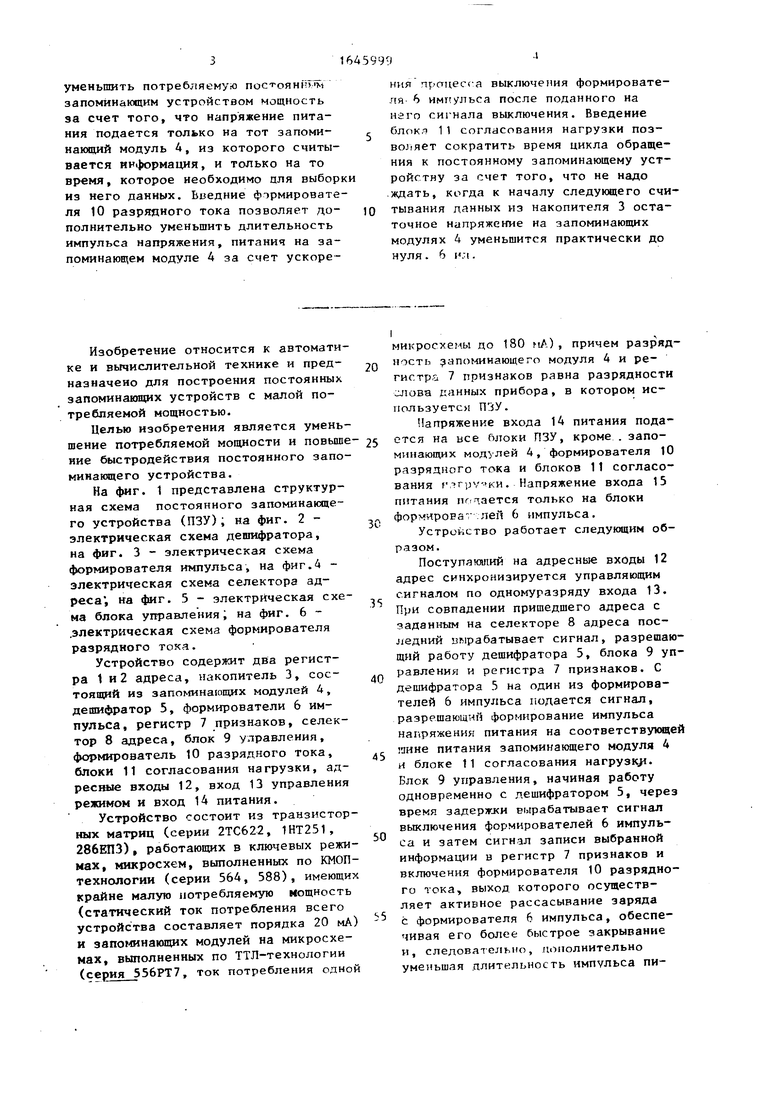

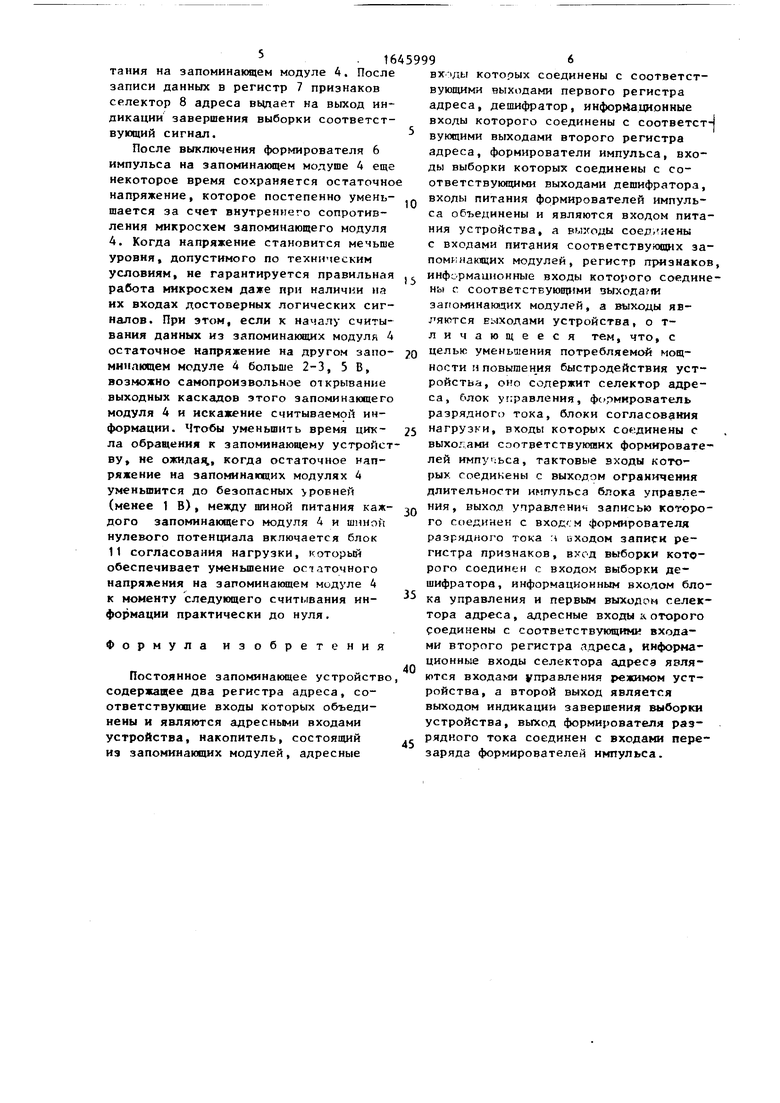

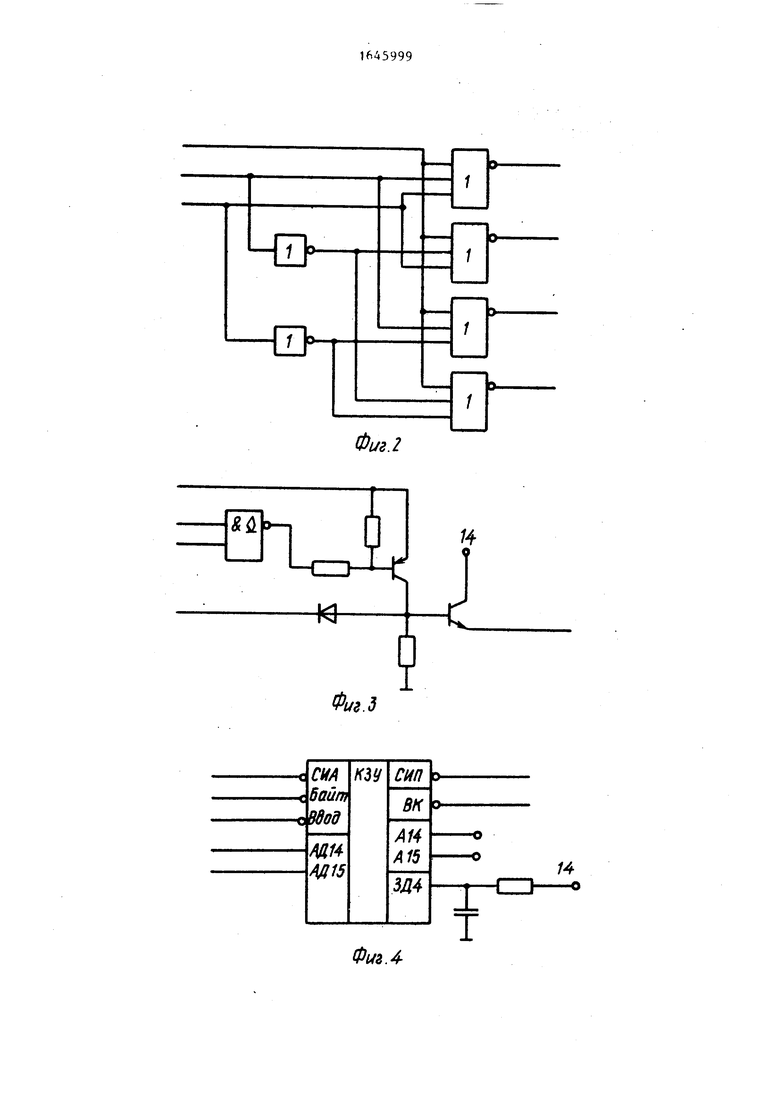

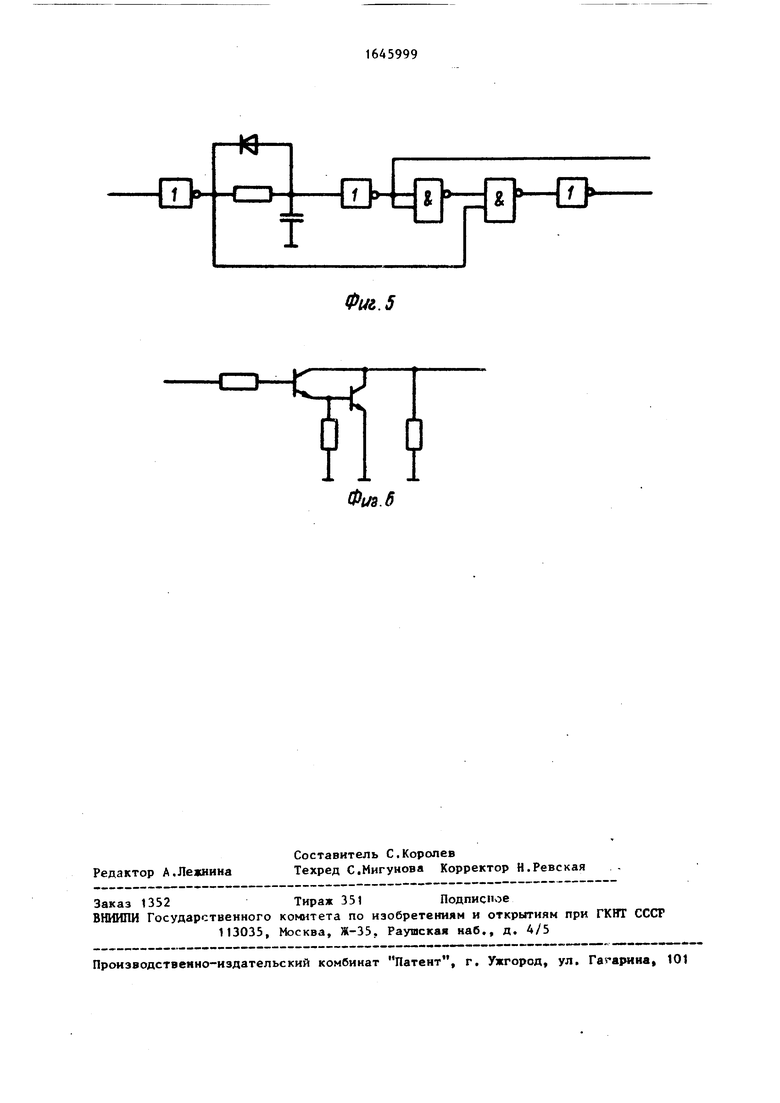

На фиг. 1 представлена структурная схема постоянного запоминающего устройства (ПЗУ); на фиг. 2 - электрическая схема дешифратора, на фиг. 3 - электрическая схема формирователя импульса, на фиг.4 - электрическая схема селектора адреса , на фиг. 5 - электрическая схема блока управления; на фиг. 6 - .электрическая схема формирователя разрядного тока.

Устройство содержит два регистра 1 и 2 адреса, накопитель 3, состоящий из запоминающих модулей 4, дешифратор 5, формирователи 6 импульса, регистр 7 признаков, селектор 8 адреса, блок 9 управления, формирователь 10 разрядного тока, блоки 11 согласования нагрузки, адресные входы 12, вход 13 управления режимом и вход 14 питания.

Устройство состоит из транзисторных матриц (серии 2ТС622, 1НТ251, 286ЕПЗ), работающих в ключевых режимах, микросхем, выполненных по КМОП- технологии (серии 564, 588), имеющих крайне малую потребляемую мощность (статический ток потребления всего устройства составляет порядка 20 мА) и запоминающих модулей на микросхемах, выполненных по ТТЛ-технологии (серия 556РТ.7, ток потребления одной

ния тг-ацесса выключения формирователя 6 импульса после поданного на наго сигнала выключения. Введение блок,- 1 1 согласования нагрузки позволяет сократить время цикла обращения к постоянному запоминающему устройству за счет того, что не надо ждать, когда к началу следующего считывания данных из накопителя 3 остаточное напряжение на запоминающих модулях 4 уменьшится практически до нуля. 6 ил.

0

5

0

5

0

5

0

5

микросхемы до 180 м/), причем разрядность запоминающего модуля 4 и регистра 7 признаков равна разрядности -лыва данных прибора, в котором используется ПЗУ.

Напряжение входа 14 питания подается на все блоки ПЗУ, кроме . запоминающих моделей 4, формирователя 10 разрядного тока и блоков 11 согласования г-труки. Напряжение входа 15 питания пг лается только на блоки формирова лен 6 импульса.

Устройство работает следующим образом.

Поступающий на адресные входы 12 адрес синхронизируется управляющим сигналом по одномуразряду входа 13. При совпадении пришедшего адреса с заданным на селекторе 8 адреса последний вырабатывает сигнал, разрешающий работу дешифратора 5, блока 9 управления и регистра 7 признаков. С дешифратора 5 на один из формирователей 6 импульса подается сигнал, разрешающий формирование импульса напряжения питания на соответствующей лине питания запоминающего модуля 4 и блоке 11 согласования нагрузки. Блок 9 управления, начиная работу одновременно с дешифратором 5, через время задержки вырабатывает сигнал выключения формирователей 6 импульса и затем сигнал записи выбранной информации в регистр 7 признаков и включения формирователя Ю разрядного тока, выход которого осуществляет активное рассасывание заряда с формирователя 6 импульса, обеспечивая его более быстрое закрывание и, следовательно, пополнительно уменьшая плительность импульса питания на запоминающем модуле 4. После записи данных в регистр 7 признаков селектор 8 адреса выдает на выход индикации завершения выборки соответствующий сигнал.

После выключения формирователя 6 импульса на запоминающем модуше 4 еще некоторое время сохраняется остаточно напряжение, которое постепенно уменьшается за счет внутреннего сопротивления микросхем запоминающего модуля 4. Когда напряжение становится меньше уровня, допустимого по техническим условиям, не гарантируется правильная работа микросхем даже при наличии на их входах достоверных логических сигналов. При этом, если к началу считывания данных из запоминающих модуля 4 остаточное напряжение на другом запоминающем модуле 4 больше 2-3, 5 В, возможно самопроизвольное открывание выходных каскадов этого запоминающего модуля 4 и искажение считываемой информации. Чтобы уменьшить время цикла обращения к запоминающему устройству, не ожида когда остаточное напряжение на запоминающих модулях 4 уменьшится до безопасных ровней (менее 1 В), между шиной питания каждого запоминающего модуля 4 и шиной нулевого потенциала включается блок 11 согласования нагрузки, который обеспечивает уменьшение остаточного напряжения на запоминающем модуле 4 к моменту следующего считывания информации практически до нуля.

Формула изобретения

Постоянное запоминающее устройство содержащее два регистра адреса, соответствующие входы которых объединены и являются адресными входами устройства, накопитель, состоящий из запоминающих модулей, адресные

1645999

0

5

0

5

0

5

вхчды которых соединены с соответствующими выходами первого регистра адреса, дешифратор, информационные входы которого соединены с соответст-j вующими выходами второго регистра адреса, формирователи импульса, входы выборки которых соединены с соответствующими выходами дешифратора, входы питания формирователей импульса объединены и являются входом питания устройства, я выводы соединены с входами питания соответствующих запоминающих модулей, регистр признаков, информационные входы которого соединены г соответствующими зыхода да запоминающих модулей, а выходы являются выходами устройства, о т- личающееся тем, что, с целью уменьшения потребляемой мощности и повышения быстродействия устройства, оно содержит селектор адреса, блок управления, формирователь разрядного тока, блоки согласования нагрузки, входы которых соединены с выходами соответствующих формирователей импучьса, тактовые входы которых соединены с выходом ограничения длительности импульса блока управления, выход управления записью которого соединен с вход м формирователя разрядного тока ч ьходом записи регистра признаков, вход выборки которого соединен с входом выборки дешифратора, информационным входом блока управления и первым выходом селектора адреса, адресные входы которого Соединены с соответствующими входами второго регистра адреса, информационные входы селектора адреса являются входами управления режимом устройства, а второй выход является выходом индикации завершения выборки устройства, выход формирователя разрядного тока соединен с входами перезаряда формирователей импульса.

2Мф

666g« 9t

Фм.5

Физ.б

Авторы

Даты

1991-04-30—Публикация

1989-07-24—Подача