со

Од

о

4 О5

Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства в вычислительных машинах

Цель изобретения - упрощение и повышение разрешающей способности устройства при локализации неисправностей.

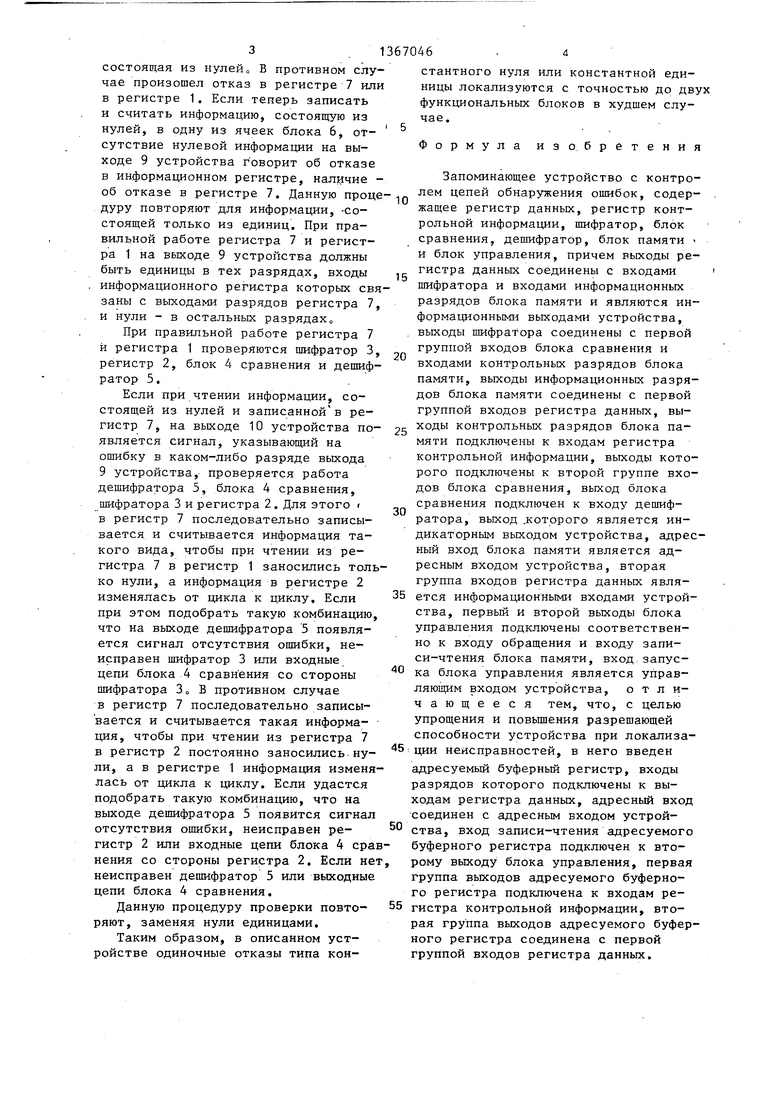

На чертеже изображена структурная схема запоминающего устройства с обнаружением ошибок.

Устройство содержит регистр 1 данных, регистр 2 контрольной информации, шифратор 3, блок 4 сравнения, дешифратор 5, блок 6 памяти, адресуемый буферный регистр 7, блок 8 управления, индикаторный выход 9, информационный выход 10, адресный вход 11, информационный вход 12, управляющий вход 13.

Шифратор 3 вырабатывает контрольные разряды корректирующего кода, например кода Хемминга.

В качестве адресуемого буферного регистра 7 может быть использована микросхема К 589ИР12. .

Устройство работает следующим образом.

При.записи в одну из ячеек блока 6 памяти по адресному входу 11 устройства поступает адрес выбранной ячейки. Блок 8 управления вырабатывает необходимую последовательность сигналов записи о Поступаюш 1е по информационному входу 12 сигналы записываются в регистр 1, а с его выхода переписываются в адресную . ячейку блока 6 памяти, а также поступают на вход шифратора 3. На выходе шифратора 3 появляются контрольные разряды кода, которые также записываются в адресуемую ячейку блока 6 памяти.

При записи информации в регистр 7 на адресном входе 11 устройства появляется адрес регистра 7. Информация из регистра 1 записывается в регистр 7. Контрольные разряды кода, выработанные шифратором 3, никуда не записываются и пропадают.

При считывании информации из какой-либо ячейки блока 6 на его адресный вход поступает адрес выбранной ячейки. Блок В упра вления вырабатывает последовательность сигналов считывания, которые управляют работой блока 6. Записанная в выбранной ячейке 6 информация считывается в регистры 1 и 2, причем в регистр 1

0

5

0

5

0

5

0

5

0

5

поступает информация, ранее записанная в ячейку блока 6 из регистра 1, а в регистр 2 - ранее записанная в ячейку с выхода шифратора 3. Из записанной в регистр 1 информации шифратор 3 вновь формирует пpoвepqчныe разряды, которые поступают на вход блока 4 сравнения При совпадении их с проверочными разрядами, находящимися в регистре 2, блок -4 сравнения, а за ним дешифратор 5 вырабатывают сигналы, соответствующие наличию безошибочной информации на выходе 9 устройства.

Йри несовпадении проверочных разрядов дешифратор 5 выдает на выход 10 устройства сигнал, по которому определяется информационньш разряд или разряды) на выходе 9 устройства, содержащий ошибочную информацию.

8частности, в классическом коде Хемминга двоичная запись информации на выходе дешифратора 5 соответствует номеру ошибочного разряда.

Эта ошибка может быть вызвана как сбоями и отказами элементов блока 6, так и отказами цепей обнарз ения ошибок. После описания особенностей считывания информации из регистра 7 будет показано, как производится ло- . кализация отказао

. При чтении информации из регистра 7 на адресном-входе 11 устройства генерируется его адрес.. Информация из. регистра 7 переписывае тся в- регистр 1 и в регистр 2. Так как регистр 7 содержит меньше разрядов, чем ячейки блока 6, информация с его выходов полностью заполняет регистр 2 и лишь частично регистр 1. Остальные разряды регистра 1 заполняются нулями Далее процесс идет аналогично процессу, считывания информации из ячейки блока 6.

Ошибки блока 6 достаточно просто отделяются . от ошибок цепей коррекции. Для этого достаточно последовательно записать и считать одинаковую информацию в различные ячейки блог ка 6. Неизменность ошибки говорит о неисправности цепей коррекции, в противном случае имеет место отказ в ячейках блока 6..

Для локализации отказа в цепях коррекции в регистр 7 записывается нулевая информация. При чтении этой информации из регистра 7 на выходе

9устройства должна быть информация.

состоящая из нулей о В противном случае произошел отказ в регистре 7 или в регистре 1. Если теперь записать и считать информацию, состоящую из нулей, в одну из ячеек блока 6, от- сутствие нулевой информации на выходе 9 устройства г оворит об отказе в информационном регистре, наличие - об отказе в регистре 7. Данную процедуру повторяют для информации, -состоящей только из единиц. При правильной работе регистра 7 и регистра 1 на выходе 9 устройства должны быть единицы в тех разрядах, входы информационного регистра которых связаны с выходами разрядов регистра 7, и нули - в остальных разрядах

При правильной работе регистра 7 и регистра 1 проверяются шифратор 3, регистр 2, блок 4 сравнения и дешифратор 5,

Если при чтении информации, состоящей из нулей и записанной в регистр 7, на выходе 10 устройства появляется сигнал, указывающий на ошибку в каком-либо разряде выхода 9 устройства, проверяется работа дешифратора 5, блока 4 сравнения, шифратора 3 и регистра 2. Для этого в регистр 7 последовательно записывается и считывается информация такого вида, чтобы при чтении из регистра 7 в регистр 1 заносились только нули, а информация в регистре 2 изменялась от цикла к циклу. Если при этом подобрать такую комбинацию, что на выходе дешифратора 5 появляется сигнал отсутствия ошибки, неисправен шифратор 3 или входные, цепи блока 4 сравнения со стороны шифратора 3 Б противном случае в регистр 7 последовательно записывается и считывается такая информация, чтобы при чтении из регистра 7 в регистр 2 постоянно заносились нули, а в регистре 1 информация изменялась от цикла к циклу. Если удастся подобрать такую комбинацию, что на выходе дешифратора 5 появится сигнал отсутствия ошибки, неисправен регистр 2 или входные цепи блока 4 сранения со стороны регистра 2, Если не неисправен дешифратор 5 или выходные цепи блока 4 сравнения.

Данную процедуру проверки повторяют, заменяя нули единицами.

Таким образом, в описанном устройстве одиночные отказы типа кон 1367046 . 4

стантного нуля или константной единицы локализуются с точностью до двух функциональных блоков в худшем случае.

0

5

0

5

0

5

0

Формула изобретения

Запоминающее устройство с контролем цепей обнаружения ошибок, содержащее регистр данных, регистр контрольной информации, шифратор, блок сравнения, дешифратор, блок памяти - и блок управления, причем вькоды регистра данных соединены с входами шифратора и входами информационных разрядов блока памяти и являются информационными вькодами устройства, выходы пшфратора соединены с первой группой входов блока сравнения и входами контрольных разрядов блока памяти, выходы информационных разрядов блока памяти соединены с первой группой входов регистра данных, выходы контрольных разрядов блока памяти подключены к входам регистра контрольной информации, выходы которого подключены к второй группе входов блока сравнения, выход блока сравнения подключен к входу дешифратора, выход .которого является индикаторным выходом устройства, адресный вход блока памяти является адресным входом устройства, вторая группа входов регистра данных является информационными входами устройства, первый и второй выходы блока управления подключены соответственно к входу обращения и входу записи-чтения блока памяти, вход запуска блока управления является управляющим входом устройства, о т л и

упрощения и повьш1ения разрешающей способности устройства при локализации неисправностей, в него введен адресуемый буферный регистр, входы разрядов которого подключены к выходам регистра данных, адресный вход соединен с адресным входом устройства, вход записи-чтения адресуемого буферного регистра подключен к второму выходу блока управления, первая группа выходов адресуемого буферного регистра подключена к входам регистра контрольной информации, вторая группа выходов адресуемого буферного регистра соединена с первой группой входов регистра данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1974 |

|

SU528614A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1355997A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам. Цель изобретения - упрощение и повьшение разрешающей способности устройства при локализации неисправностей. Устройство содержит регистр 1 данных, регистр 2 контрольной информации, шифратор 3, блок 4 сравнения, дешифратор 5, блок 6 памяти, адресуемый буферный регистр 7 и блок 8 управления. 1 Ш1.

| Запоминающее устройство с самоконтролем | 1978 |

|

SU767845A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с контролем цепей коррекции ошибок | 1981 |

|

SU982099A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-15—Публикация

1985-12-09—Подача