Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и диагностики неисправностей.

Цель изобретения - повышение достоверности контроля путем идентификации вида помехи

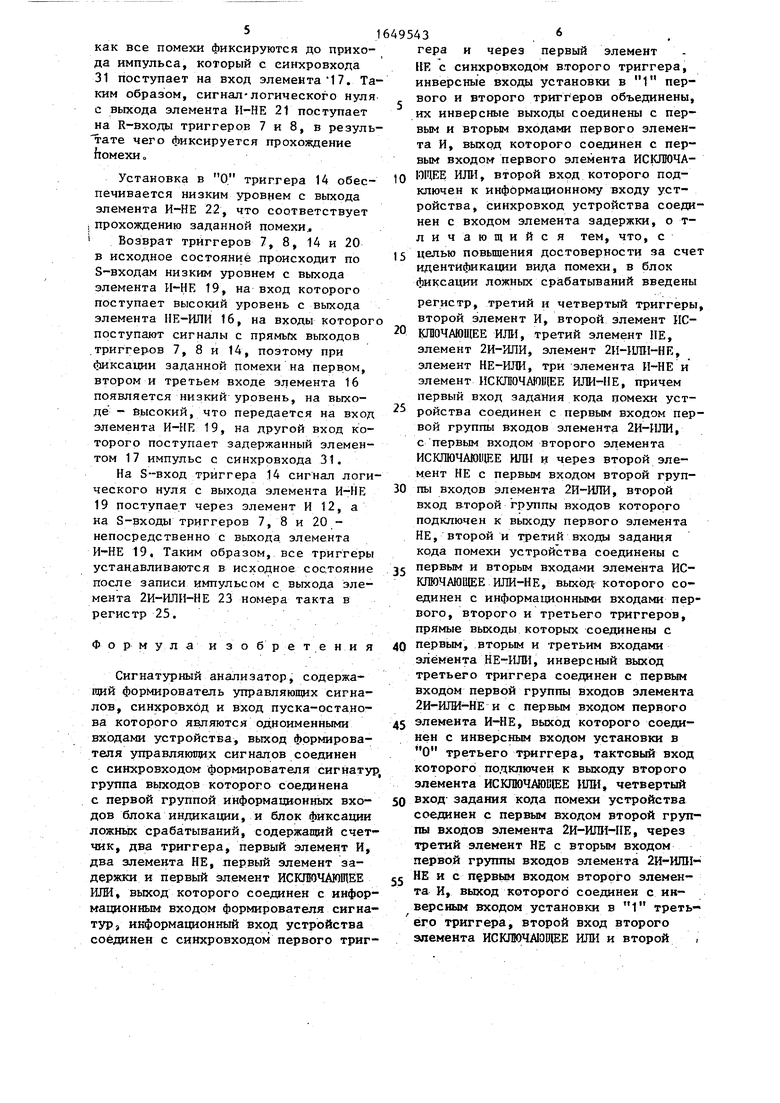

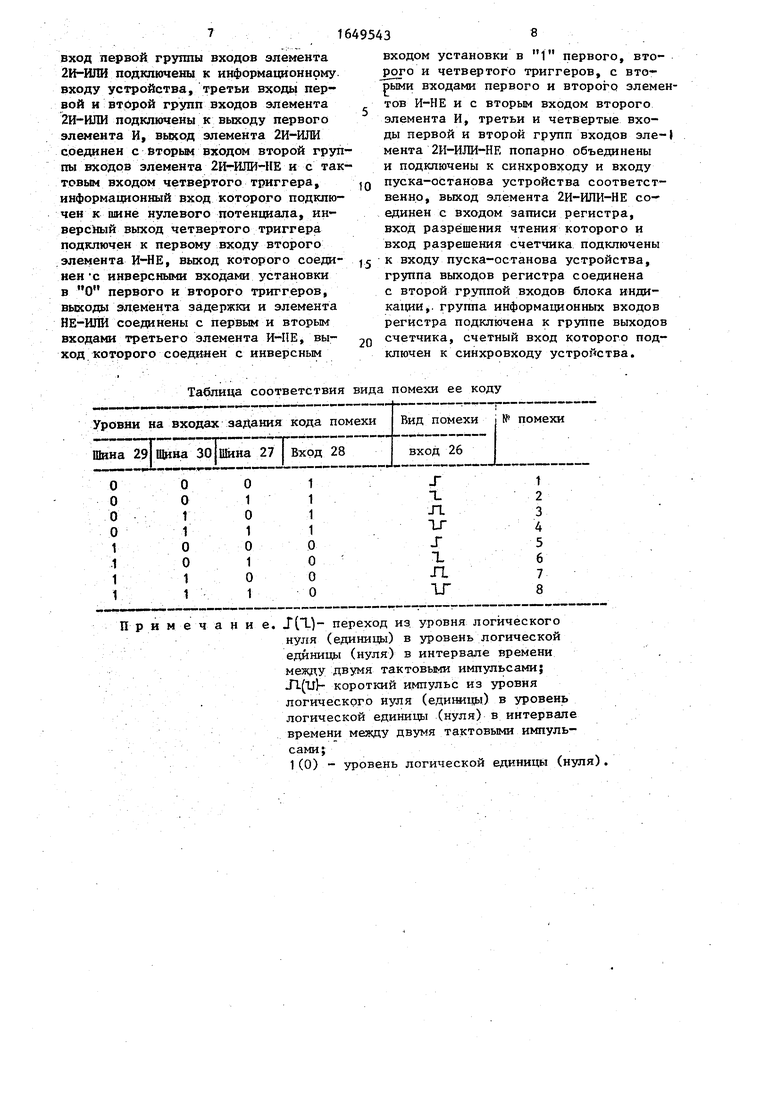

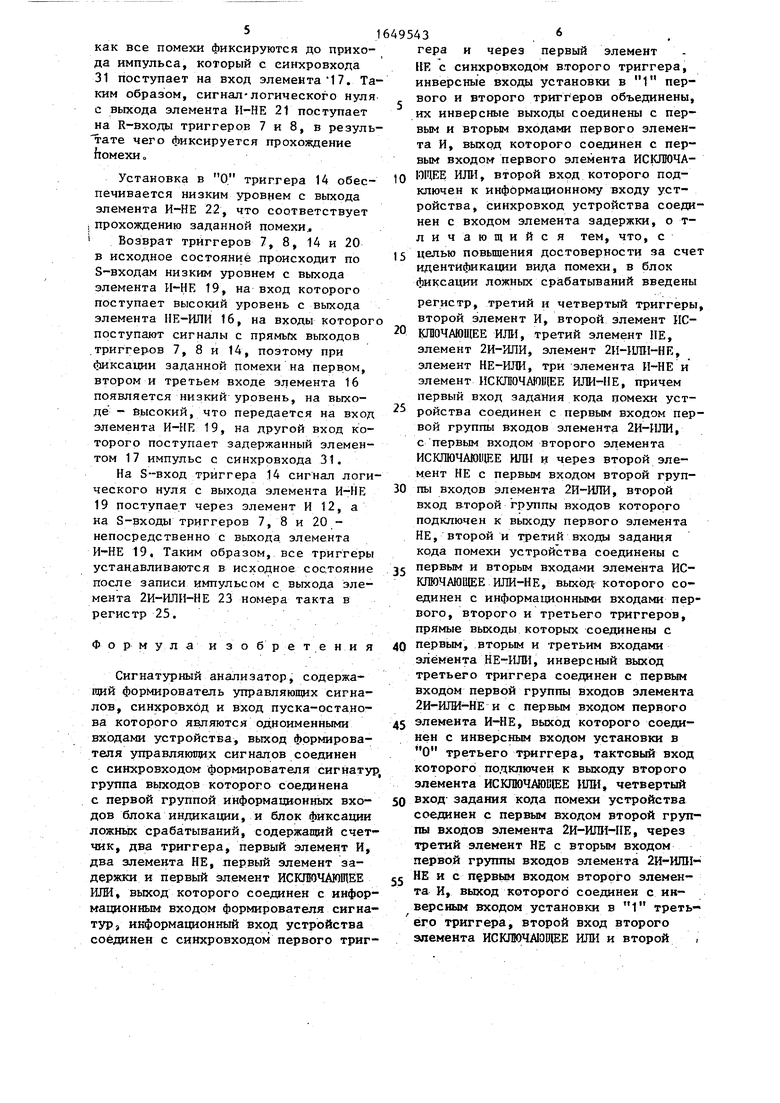

На фиг. 1 и 2 представлена фун- кциональная схема сигнатурного анализатора; на фиг. 3 - временные диаграммы его работы.

Сигнатурный анализатор содержит блок 1 индикации, формирователь 2 сигнатур, формирователь 3 управляющих сигналов и блок 4 фиксации ложных срабатываний, включающий в себя элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент И 6, триггеры 7 и 8, элементы НЕ 9 и 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11,

элемент И 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13, триггер 14, элемент 2И-ИЛИ 15, элемент НЕ-ИЛИ 16, элемент 17 задержки, элемент НЕ 18, элемент И-НЕ 19, триггер 20, элементы И-НЕ 21 и 22, элемент 2И-ИЛИ-НЕ 23, счетчик 24 и регистр 25. Кроме того, анализатор имеет информационный вход 26, входы 27-30 задания кода помехи, синхровход 31 и вход 32 пуска-останова„

На диаграмме обозначены временные последовательности сигналов: а - на синхровходе 31 сигнатурного анализатора; 6 - на выходе элемента 17 задержки; 8 - на информационном входе 26, Ј - на входе 28; % - на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13; б - на выходе 2И-ИЛИ 15; Ж - на ииверс%

QP

%

со

ном выходе триггера 14; U - на выходе элемента 2И-ИЛИ-НЕ 23; 1C - на входе 27; Л - на входе 30; Л - иа входе 29.

Сигнатурный анализатор работает следующим образом.

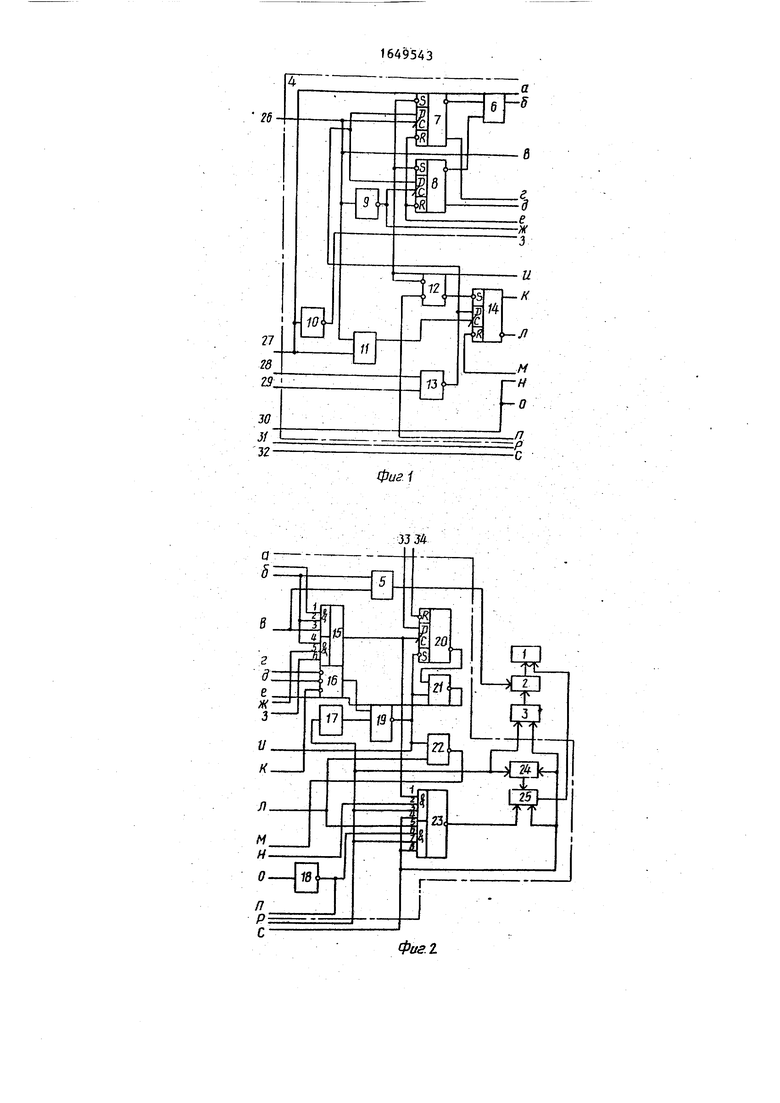

На входы 27-30 задаются в соответствии с таблицей уровни логического нуля (низкий) или логической единицы (высокий) для выделения поме- хи в исследуемом сигнале, который подается на вход 26.

Запись данньвс входа 26 для свертки в сигнатуру ведется по переднему фронту импульсов с синхровхода 31 в формирователь 2 сигнатур. В случае высокого уровня на входе 29 и высокого уровня на входе 28, а также в случае низкого уровня на входе 28 и входе 29 помехи типа 3, 4, 7, 8 (см.таблицу) формирователем 2 сигнатур не фиксируются, а в любом другом случае формирователь 2 зафиксирует указанные помехи в виде отличной от эталонной сигнатуры В регист- ре 25 записывается номер такта, в котором произошла первая заданная в соответствии с таблицей помеха.

Это происходит следующим образом. На вход счетчика 24 поступает сигнал с входа 32. В случае низкого уровня на указанном входе счетчик обнуляется и находится в таком состоянии, пока на входе 32 не появится высокий уровень, который соответствует интервалу измерения. В этом случае счетчик 24 подсчитывает количество импульсов с синхровхода 31 и эти данные поступают на группу информационных входов регистра 25. В случае возникновения помехи, соответствующей заданной, на входах 27-30 и на выходе элемента 2И-ИЛИ 23 формируется перепад из высокого уровня в низкий, по которому в регистр 25 записывается состояние счетчика 24, соответствующее номеру такта, в котором произошла помеха.

При появлении сигнала низкого уровня на входе 32 интервал измерения заканчивается и регистр 25 переходит в режим выдачи информации, т.е. номера такта, в котором произошла помеха, код которой задан в соответствии с таблицей.

При фиксации помех вида 1, 2, 5, 6 (см. таблицу) срабатывает триггер 14 на инверсном выходе которого в исходном состоянии - низкий уровень. По

5

0

Q

5

0

5

0

5

0

еле срабатывания триггера 14 сигнал логической единицы с инверсного выхода поступает на вход элемента 2И-ИЛИ-ИЕ 23, на входах которого присутствует также сигнал логической единицы с выхода элемента НЕ 18. При поступлении импульса с синхровхода 31 на выходе элемента 2И-ИЛИ-НЕ 23 формируется импульс, который записывается в регистр 25 данный номер такта с выхода счетчика 24.

Например, если задан первый вид помехи (см.таблицу), то на информационный вход (D) триггера 14 сигнал логического нуля поступает с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13, поскольку на входах последнего присутствуют сигнал логической единицы с входа 28 и сигнал логического нуля с вх ца 29, а на тактовом входе триггера 4 формируется положительный пе- pei п, с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, обусловленный сигналом логического нуля с входа 27 и переходом с входа 26, Таким образом, на инверсном выходе триггера 14 возникает высокий уровень.

В случае, если задан режим фиксации помех вида 3, 4, 7, 8, триггер 14 блокируется по S-входу низким уровнем с выхода элемента И 12, обусловленный сигналом логического нуля с выхода элемента НЕ 18, на входе которого присутствует высокий уровень с входа 30. Помехи вида 3, 4, 7, 8 фиксируются триггерами 7, 8, а их идентификация обеспечивается элементом г 2И-ИЛИ 15

Например, если задана помеха вид 3, то сигнал логической единицы на выходе элемента 2И-ИЛИ 15 появляется в случае, если при наличии сигнала логической единицы на выходе элемента НЕ 10 на выходе элемента И 6 сформи-- руется сигнал логической единицы после прохождения короткого импульса на входе 26, форма которого соответствует третьему виду помехи.

Триггер 20 фиксирует состояние триггеров 7 и 8 после прохождения заданной помехи и на инверсном выходе триггера 20 появляется сигнал логической единицы 1, который поступает на вход элемента И-НЕ 21, на другом входе которого присутствует высокий уровень с выхода элемента И-НЕ 19, вызванный низким уровнен на. выходе элемента 17 задержки, так

51649543

и фиксируются до прихокоторый с еинхровхода на вход элемента 17. Тасигнал-логического нуля ента И-НЕ 21 поступает иггеров 7 и 8, в резульсируется прохождение

ге НЕ ин во их вы та вы ЛО ЮЩ кл ро не л 15 це ид фи

Установка в О триггера 14 обеспечивается низким уровнем с выхода

соответствует

элемента И-НЕ 22, что

прохождению заданной помехи.. Возврат триггеров 7, 8, 14 и 20 в исходное состояние происходит по S-входам низким уровнем с выхода элемента PI-HE 19, на вход которого поступает высокий уровень с выхода элемента НЕ-ИЛИ 16, на входы которого поступают сигналы с прямых выходов триггеров 7, 8 и 14, поэтому при иксации заданной помехи на первом, втором и третьем входе элемента 16 появляется низкий уровень, на выходе - высокий, что передается на вход элемента И-НЕ 19, на другой вход которого поступает задержанный элементом 17 импульс с еинхровхода 31.

На S-вход триггера 14 сигнал логического нуля с выхода элемента И-НЕ 19 поступает через элемент И 12, а на S-входы триггеров 7, 8 и 20 - непосредственно с выхода элемента И-НЕ 19. Таким образом, все триггеры устанавливаются в исходное состояние после записи импульсом с выхода элеента 2И-ИЛИ-НЕ 23 номера такта в регистр 25.

Формула изобретения 40

20

Сигнатурный анализатор, содержащий формирователь управляющих сигналов, синхровход и вход пуска-останова которого являются одноименными входами устройства, выход формирователя управляющих сигналов соединен с синхровходом формирователя сигнатур, группа выходов которого соединена с первой группой информационных входов блока индикации, и блок фиксации ложных срабатываний, содержащий счетчик, два триггера, первый элемент И, два элемента НЕ, первый элемент задержки и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом формирователя сигнатур, информационный вход устройства соединен с синхровходом первого триг

5

0

0

6

гера и через первый элемент НЕ с синхровходом второго триггера, инверсные входы установки в 1 первого и второго триггеров объединены, их инверсные выходы соединены с первым и вторым входами первого элемента И, выход которого соединен с первым входом первого элемента ИСКЛЮЧАО ЮЩЕЕ ИЛИ, второй вход которого подключен к информационному входу устройства, синхровход устройства соединен с входом элемента задержки, о т- личающийся тем, что, с 5 целью повышения достоверности ча счет идентификации вида помехи, в блок фиксации ложных срабатываний введены

регистр, третий и четвертый триггеры, второй элемент И, второй элемент ИС0 КЛЮЧАЮЩЕЕ ИЛИ, третий элемент НЕ, элемент 2И-ИЛИ, элемент 2И-ИЛИ-НЕ, элемент НЕ-ИЛИ, три элемента И-НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, причем первый вход яадания кода помехи устройства соединен с первым входом первой группы входов элемента 2И-ИЛИ, с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и через второй элемент НЕ с первым входом второй группы входов элемента 2И-ИЛИ, второй вход второй группы входов которого подключен к выходу первого элемента НЕ, второй и третий входы задания кода помехи устройства соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выход которого соединен с информационными входами первого, второго и третьего триггеров, прямые выходы которых соединены с первым, вторым и третьим входами элемента НЕ-ИЛИ, инверсный выход третьего триггера соединен с первым входом первой группы входов элемента 2И-ИЛИ-НЕ и с первым входом первого

5 элемента И-НЕ, выход которого соединен с инверсным входом установки в 0й третьего триггера, тактовый вход которого подключен к выходу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый вход задания кода помехи устройства соединен с первым входом второй группы входов элемента 2И-ИЛИ-НЕ, через третий элемент НЕ с вторым входом первой группы входов элемента 2И-ИЛИ- НЕ и с первым входом второго элемента И, выход которого соединен с инверсным входом установки в 1 третьего триггера, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй ,

5

0

5

вход первой группы входов элемента 2И-ИЛИ подключены к информационному входу устройства, третьи входы первой и второй групп входов элемента 2И-ИЛИ подключены к выходу первого элемента И, выход элемента 2И-ИЛИ соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ и с тактовым входом четвертого триггера, информационный вход которого подключен к шине нулевого потенциала, инверсный выход четвертого триггера подключен к первому входу второго элемента И-НЕ, выход которого соединен фс инверсными входами установки в О первого и второго триггеров, выходы элемента задержки и элемента НЕ-ИЛИ соединены с первым и вторым входами третьего элемента И-ИЕ, выход которого соединен с инверсным

16495438

входом установки в 1 первого, второго и четвертого триггеров, с вторыми входами первого и второго элемен тов И-НЕ и с вторым входом второго элемента И, третьи и четвертые входы первой и второй групп входов эле-| мента 2И-ИЛИ-НЕ попарно объединены и подключены к синхровходу и входу

JQ пуска-останова устройства соответственно, выход элемента 2И-ИЛИ-НЕ соединен с входом записи регистра, вход разрешения чтения которого и вход разрешения счетчика подключены

15 к входу пуска-останова устройства, группа выходов регистра соединена с второй группой входов блока индикации, группа информационных входов регистра подключена к группе выходов

2Q счетчика, счетный вход которого подключен к синхровходу устройства.

рыми входами первого и второго элементов И-НЕ и с вторым входом второго элемента И, третьи и четвертые входы первой и второй групп входов эле-| мента 2И-ИЛИ-НЕ попарно объединены и подключены к синхровходу и входу

пуска-останова устройства соответственно, выход элемента 2И-ИЛИ-НЕ соединен с входом записи регистра, вход разрешения чтения которого и вход разрешения счетчика подключены

к входу пуска-останова устройства, группа выходов регистра соединена с второй группой входов блока индикации, группа информационных входов регистра подключена к группе выходов

счетчика, счетный вход которого подключен к синхровходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Сигнатурный анализатор | 1985 |

|

SU1287162A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Сигнатурный анализатор | 1984 |

|

SU1171797A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и диагностики неисправностей. Цель изобретения - повышение достоверности контроля. Анализатор содержит блок индикации, формирователь сигнатур, йор- мирователь управляющих сигналов и блок фиксации ложных срабатываний, позволяющий выявлять вид и момент появления помехового сигнала, возникающего в исследуемой последовательности. Особенно это существенно для схем с микропроцессорными элементами, в которых сбойные ситуации могут возникать при выполнении набора некоторых команд на определенном временном интервале. 3 иЛо СЛ

Таблица соответствия вида помехи ее коду

Примечание,

.Г(Т.)- переход из уровня логического нуля (единицы) в уровень логической единицы (нуля) в интервале времени между двумя тактовыми импульсами; JT(TJ}- короткий импульс из уровня логического нуля (единицы) в уровень логической единицы (нуля) в интервале времени между двумя тактовыми импульсами;1(0) - уровень логической единицы (нуля).

ФигЗ

| Электроника, 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Сигнатурный анализатор | 1985 |

|

SU1287162A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1988-01-11—Подача