Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи.

Целью изобретения является расширение функциональных возможностей путем обеспечения контроля последовательностей в произвольном порядке.

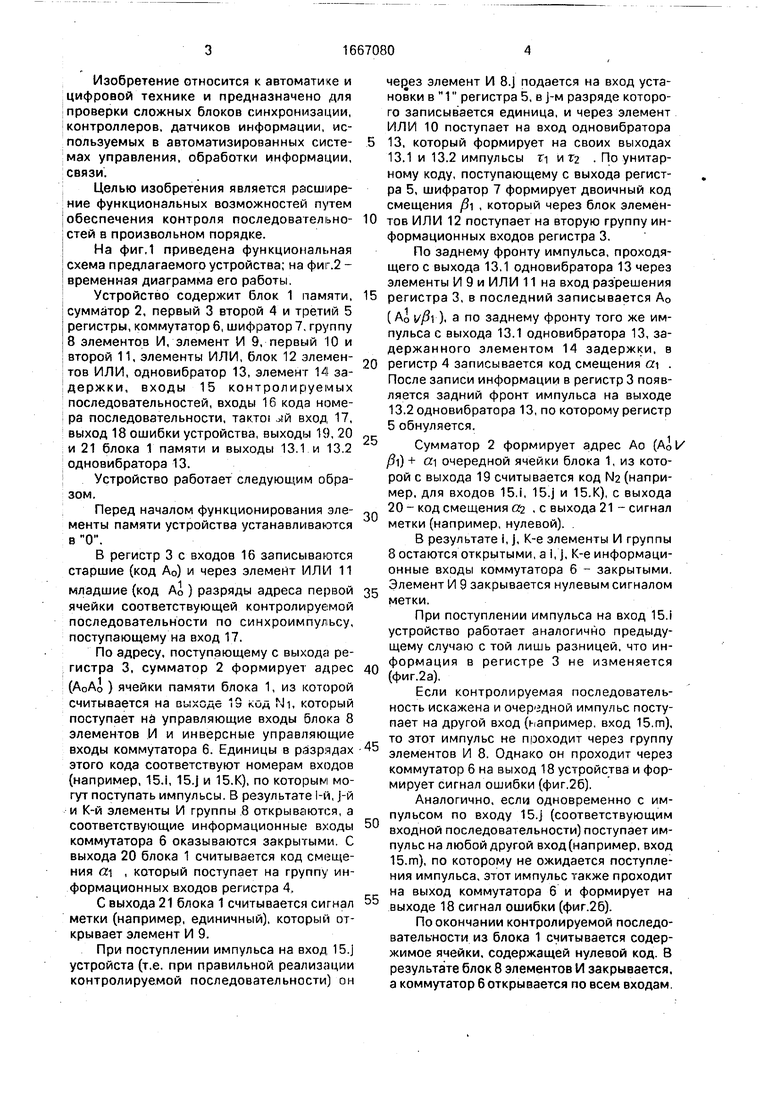

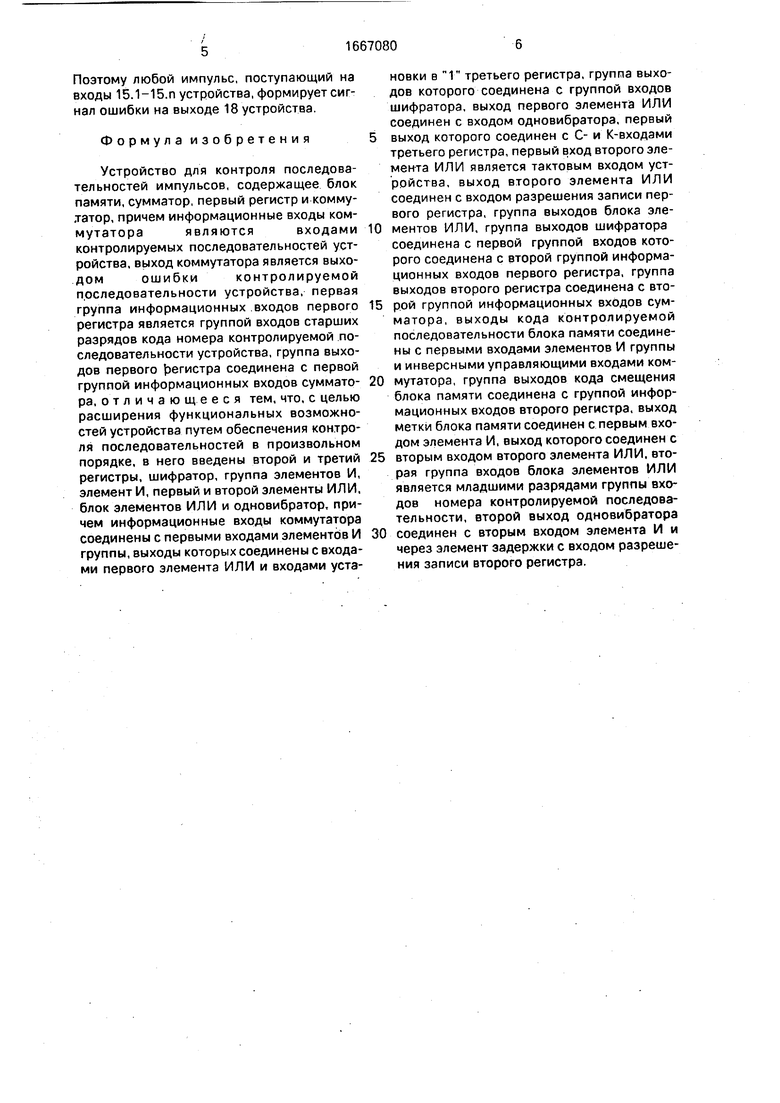

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - временная диаграмма его работы.

Устройство содержит блок 1 памяти, сумматор 2, первый 3 второй 4 и третий 5 регистры, коммутатор 6, шифратор 7, группу 8 элементов И, элемент И 9, первый 10 и второй 11, элементы ИЛИ, блок 12 элементов ИЛИ, одновибратор 13, элемент 14 задержки, входы 15 контролируемых последовательностей, входы 16 кода номера последовательности, такто ли вход 17, выход 18 ошибки устройства, выходы 19, 20 и 21 блока 1 памяти и выходы 13.1 и 13.2 одновибратора 13.

Устройство работает следующим образом.

Перед началом функционирования элементы памяти устройства устанавливаются в О.

В регистр 3 с входов 16 записываются старшие (код А0) и через элемент ИЛИ 11

младшие (код Ai ) разряды адреса первой ячейки соответствующей контролируемой последовательности по синхроимпульсу, поступающему на вход 17.

По адресу, поступающему с выхода регистра 3, сумматор 2 формирует адрес

(А0Ао ) ячейки памяти блока 1, из которой считывается на выходе 13 код NI, который поступает на управляющие входы блока 8 элементов И и инверсные управляющие входы коммутатора 6. Единицы в разрядах этого кода соответствуют номерам входов (например, 15.i, 15.J и 15.К), по которым могут поступать импульсы. В результате i-й, j-й и К-й элементы И группы 8 открываются, а соответствующие информационные входы коммутатора 6 оказываются закрытыми. С выхода 20 блока 1 считывается код смещения а , который поступает на группу информационных входов регистра 4.

С выхода 21 блока 1 считывается сигнал метки (например, единичный), который открывает элемент И 9.

При поступлении импульса на вход 15.J устройств (т.е. при правильной реализации контролируемой последовательности) он

0

5

0

5

0

5

0

5

0

5

через элемент И 8.J подается на вход установки в 1 регистра 5, в j-м разряде которого записывается единица, и через элемент ИЛИ 10 поступает на вход одновибратора 13, который формирует на своих выходах

13.1и 13.2 импульсы ri и Т2 . По унитарному коду, поступающему с выхода регистра 5, шифратор 7 формирует двоичный код смещения , который через блок элементов ИЛИ 12 поступает на вторую группу информационных входов регистра 3.

По заднему фронту импульса, проходящего с выхода 13.1 одновибратора 13 через элементы И 9 и ИЛИ 11 на вход разрешения регистра 3, в последний записывается А0

( ), а по заднему фронту того же импульса с выхода 13.1 одновибратора 13, задержанного элементом 14 задержки, в регистр 4 записывается код смещения а . После записи информации в регистр 3 появляется задний фронт импульса на выходе

13.2одновибратора 13, по которому регистр 5 обнуляется.

Сумматор 2 формирует адрес АО (Aol/ /Ji) + a очередной ячейки блока 1, из которой с выхода 19 считывается код N2 (например, для входов 15.1, 15.j и 15.К), с выхода 20 - код смещения щ , с выхода 21 - сигнал метки (например, нулевой).

В результате i, J, К-е элементы И группы 8 остаются открытыми, a i, J, К-е информационные входы коммутатора б - закрытыми. Элемент И 9 закрывается нулевым сигналом метки.

При поступлении импульса на вход 15.i устройство работает аналогично предыдущему случаю с той лишь разницей, что информация в регистре 3 не изменяется (фиг.2а).

Если контролируемая последовательность искажена и очередной импульс поступает на другой вход (например, вход 15.т), то этот импульс не пооходит через группу элементов И 8. Однако он проходит через коммутатор 6 на выход 18 устройства и формирует сигнал ошибки (фиг.26).

Аналогично, если одновременно с импульсом по входу 15.J (соответствующим входной последовательности) поступает импульс на любой другой вход (например, вход 15.т), по которому не ожидается поступления импульса, этот импульс также проходит на выход коммутатора 6 и формирует на выходе 18 сигнал ошибки (фиг.26).

По окончании контролируемой последовательности из блока 1 считывается содержимое ячейки, содержащей нулевой код. В результате блок 8 элементов И закрывается, а коммутатор 6 открывается по всем входам.

Поэтому любой импульс, поступающий на входы 15.1-15.п устройства, формирует сигнал ошибки на выходе 18 устройства.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок памяти, сумматор, первый регистр и коммутатор, причем информационные входы коммутатораявляютсявходамиконтролируемых последовательностей устройства, выход коммутатора является выходом ошибки контролируемой последовательности устройства, первая группа информационных входов первого регистра является группой входов старших разрядов кода номера контролируемой последовательности устройства, группа выходов первого регистра соединена с первой группой информационных входов сумматора, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения контроля последовательностей в произвольном порядке, в него введены второй и третий регистры, шифратор, группа элементов И, элемент И, первый и второй элементы ИЛИ, блок элементов ИЛИ и одновибратор, причем информационные входы коммутатора соединены с первыми входами элементов И группы, выходы которых соединены с входами первого элемента ИЛИ и входами установки в 1 третьего регистра, группа выходов которого соединена с группой входов шифратора, выход первого элемента ИЛИ соединен с входом одновибратора. первый

выход которого соединен с С- и К-входами третьего регистра, первый вход второго элемента ИЛИ является тактовым входом устройства, выход второго элемента ИЛИ соединен с входом разрешения записи первого регистра, группа выходов блока элементов ИЛИ. группа выходов шифратора соединена с первой группой входов которого соединена с второй группой информационных входов первого регистра, группа выходов второго регистра соединена с второй группой информационных входов сумматора, выходы кода контролируемой последовательности блока памяти соединены с первыми входами элементов И группы и инверсными управляющими входами коммутатора, группа выходов кода смещения блока памяти соединена с группой информационных входов второго регистра, выход метки блока памяти соединен с первым входом элемента И, выход которого соединен с

вторым входом второго элемента ИЛИ, вторая группа входов блока элементов ИЛИ является младшими разрядами группы входов номера контролируемой последовательности, второй выход одновибратора

соединен с вторым входом элемента И и через элемент задержки с входом разрешения записи второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Асинхронное устройство для программного управления | 1987 |

|

SU1481712A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1619277A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1649548A1 |

Изобретение относится к области автоматики и цифровой техники и предназначено для проверки сложных блоков синхронизации, контролеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи. Отличительной особенностью устройства является то, что оно позволяет обеспечить контроль многоальтернативного поступления импульса за счет записи в блоке памяти всех входов, по которым может поступить очередной импульс, и формирование очередного адреса обращения к памяти с учетом номера входа, по которому поступил импульс. Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей в произвольном порядке. Поставленная цель достигается за счет введения регистров 4, 5, шифратора 7, группы элементов И 8, элементов И 9, 10, элемента ИЛИ 11, блока 12 элементов ИЛИ, одновибратора 13. 2 ил.

| Фотоэлектрический прибор для определения границ облаков в полете | 1959 |

|

SU125930A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1501064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-09-20—Подача