Изобретение относится к цифровой вычислительной технике и может найти применение в составе специализированного вычислительного устройства для вычисления интегральных операторов Вольтерра - Гаммерштейна с ядрами об щего вида для решения задач анализа и оптимизации нелинейных электрических цепей измерения и контроля napaметров, моделирования, управления и регулирования объектов и процессов, связанных с преобразованием и передачей энергии, например преобразование энергии в различных датчиках, прохождение сигналов в линиях связи, явлени теп.по- и массопереноса, химические;, и ядерные превращения .и т.д.

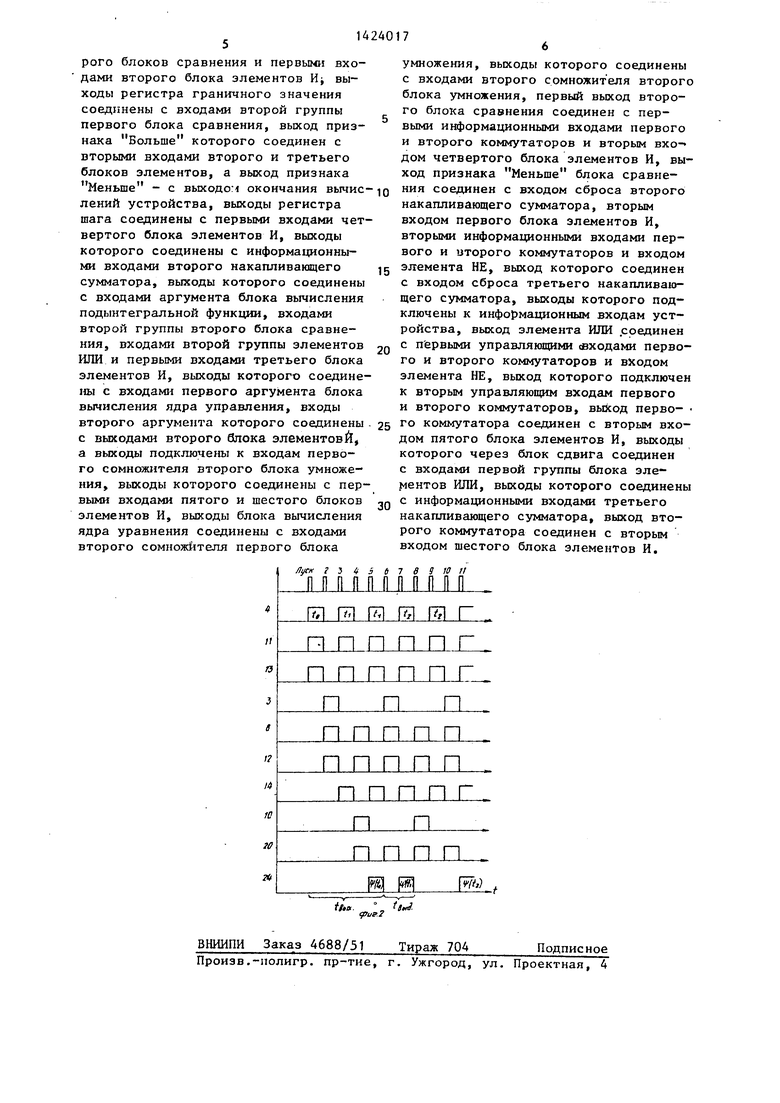

Цель изобретения - повышение точности вычислений и быстродействия. На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы блоков устройства.

Устройство содержит регистр 1 niara, HcpBbiii блок 2 элементов И, первьп накаплипаюпр1Й сут-матор 3, первый блок 4 сравнения, регистр 5 граничного значения, второй 6 и третий 7 блоки элементов II, блок 8 вычисле- ПИЯ ядра уравнения, четвертый блок 9 элементов Н, второй наканливающий cjT.ii.jaTop 10, блок 11 вычисления подынтегральной функции, первый блок 12 умножения, второй блок 13 сравнения, второй блок 14 умножения,элемент ИПИ 15, элемент НЕ 16, nepBbtfi коммутатор 17, пятый блок 18 элементов И, элемент 19 задержки, блок 20 сдвига, второй коммутатор 21, шестой блок 22 элементов И, блок 23 элементов Ш1Н, третий накат1пиваюи(ий сумматор 24.

Описание физическшс процессов при решепии задач сводится к решению нелинейного интегрального уравнения Вольтерра-Гаммерштейна 2-го рода

y(t)-J k(t,s)(s)ds f(t), (1)

CL

где y(t) - исследуемьш сигнал, k(t;,s) - ядро интегрального уравнения, которое несет информацию об исследуемом объекте;

F - заданная нелинейная функция;

f(t) - отклик объекта на исследуемый сигнал; t - время.

Эффективность решения интегрального уравнения (1) зависит от того, насколько успешно будет реализован входящий в него интегра/1ьный оператор

«fC

t) k(t,s)F(f (s)ds (2)

От успешной реализации интегрального оператора зависит производительность и экономичность сепциализиро- ванных процессора и устройства, реализующих интегральньй оператор и уравнение Вольтерра-Гаммерштейна.

В устройстве реализуется квадратурный метод численной реализации интегрального оператора (2) посредством расчетного выражения I

(ti)h Ajk(tj,t;)F f(tj), (3)

J.O

где Aj

0,5 при j О, j 1; 1 при О i. j 4 i.

5 . 5

„

0

5

5

т.е. реализуются квадратурная формула трапеций с шагом дискретизации h const.

Устройство работает следующим образом.

Перед началом работы значение шага h заносится в первый регистр 1, а значение b верхней границы интегрального оператора - в регистр 5.Все остальные операционные блоки устанавливаются в О. После подачи управляющего сигнала Пуск на шину Выдача кода первого 3 и второго 10 накапливающих сумматоров (первый такт работы процессора) значение t: ь tp О с сумматора 3 поступает на первый вход первого блока 11 сравнения, на второй вход которого с регистра 5 поступает значение Ь в результате этого в первом блоке 4 сравнения выполняется сравнение tg с. Ь, Одновременно значение переменной t t О поступает на первый вход второго блока 13 сравнения, на второй вход ко торого с накапливающего сумматора 10 поступает значение переменной t tp О, в результате чего на втором блоке 13 сравнения происходит сравнение переменной tj t с переменной t tg. Кроме того, одновременно значение переменной t; О поступает на п-входовый элемент ИЛИ 15 (на выходе которого в результате вьтолне- ния логической операции ИЛИ вьфабаты- вается нулевой сигнал, выполняющий

функции управления) и на вход блока 11 (в нем вычисляется значение нелинейной функции F f(t )J.

Во втором такте в первом умножителе 12 выполняется умножение значения шага h, поступающего с регистра 1, на значение налинейной функции ), поступающей с блока 11. В результате получаем значение про- изведения h- F(to)j, а значения переменных tj О и t О через открытые управляющим сигналом t . b с первого выхода первого блока 4 сравнения второй 6 и третий 7 блоки элементов И проходят на , блок 8, в результате чего в нем вычисляется значение ядра k(te, to). Одновременно управляющий сигнал tj tj (j i) поступает на вход элемента 19 задержки, на пину сброса третьего накапливающего сумматора, на первые входы первого 17 и второго 21 коммутаторов и открывает первый блок 2 элементов И, в результате чего на первом накапливающем сумматоре 3 вычисляется t t to + h h.

В третьем такте в первом блоке А сравнения вьшолняется сравнение t j t с b, во втором блоке 13 срав нения - tj с t| , в блоке 11 вычисляется значение нелинейной функции F L f (о) а на втором умножителе 14 произведение h k(tp, to ) х (to) .

В четвертом такте через открытый

управляющим сигналом tj с tj с перво- го выхода второго блока сравнения чевертый блок 9 элементов И значение шга h поступает на второй накапливающий сумматор 10, где вычисляется значение tj t tp + h h, в блоке 8 вычисляется значение ядра k(t , to ) в первом умножителе 12 - произведение (to) , в блоке 20 сдвига выполняется сдвиг на один разряд в в сторону младщих разрядов значения произведения h.k(t6,to) (t ) , в результате чего указанное значение произведения умножается на коэффициент AJ 0,5.

В пятом такте в первом блоке 4 сравнения выполняется сравнение t t с b, во втором блоке 13 сравнения tj t с t; t-, в блоке 11 вычисляется значение (to)l, во втором умножителе 14 - произведение h k(t , t,) (t ), а в третьем накапливающем сумматоре 24 - значени функции V (to) 0,5 h.k(tp, t) .

5 5

Q

с

5

. F f (to) . Через время задержки X , достаточное для фиксации и выдачи результата, с элемента 19 задержки на шину сброса выходного накапливающего сумматора 24 поступает управляющий сигнал, которьй очищает и подготавливает его к вычислению следующего значения оператора (t).

Таким образом, :дикл работы устройства состоит из пяти тактов. Работа его иллюстрируется временной диаграммой (фиг. 2).

Как видно из временной диграммы, распараллеливание вычислительного процесса позволяет вычислять один член суммы

i.

ZhAj k(ti,tj) (to)

0

5

j o

за время t ц 5 N.ftt, где N - номер узла дискретизации, ut - квант времени, определяемый временем обработки информации в самом медленнодействующем операционном блоке устройства. Однако после заполнения всех операционных блоков информацией время вьщачи результата вычисления одного члена , суммы за счет перекрытия циклов работы будет составлять Т j 2 N , т.е. установившаяся производительность устройства будет всего лишь примерно в два раза меньше производительности его самого медленнодействующего операционного блока.

Формула изобретения

Устройство для вычисления нелинейных интегральных операторов, содержащее элемент НЕ, регистр шага, регистр граничного значения и блок вычисления подьштегральной функции, отличающееся тем, что, с целью повьш1е- ния точности вычислений и быстродействия, оно содержит шесть блоков элементов И, блок вычисления ядра управления, блок элементов ИЛИ, три накапливающих сумматора, элемент задержки, два блока умножения, элемент ИЛИ, два блока сравнения, два коммутатора, блок сдвига, причем выходы регистра шага соединены с входами первого сомножителя первого блока умножения и первыми входами первого блока элементов И, выходы которого соединены с входами первого накапливающего сум-, матора, выходы которого соединены с входами первой группы первого и вто

рого блоков сравнения и первыми входами второго блока элементов И выходы регистра граничного значения соединены с входами второй группы первого блока сравнения, выход признака Больше которого соединен с вторыми входами второго и третьего блоков элементов, а выход признака Меньше - с выходом окончания ВЫЧИС ланий устройства, выходы регистра шага соединены с первыми входами четвертого блока элементов И, выходы которого соединены с информационными входами второго накапливающего сумматора, выходы которого соединены с входами аргумента блока вычисления подынтегральной функции, входами второй группы второго блока сравнения, входами второй группы элементов ИЛИ и первыми входами третьего блока элементов И, выходы которого соединены с входами первого аргумента блока вычисления ядра управления, входы второго аргумента которого соединены с выходами второго блока элементовЙ, а выходы подключены к входам первого сомножителя второго блока умножения, выходы которого соединены с пер ВЫ14И входами пятого и шестого блоков элементов И, выходы блока вычисления ядра уравнения соединены с входами второго сомножителя первого блока

5

0

5

0

умножения, выходы которого соединены с входами второго сомножителя второго блока умножения, первый выход второго блока сравнения соединен с первыми информационными входами первого и второго коммутаторов и вторым вхо-- дом четвертого блока элементов И, выход признака Меньше блока сравнения соединен с входом сброса второго накапливающего сумматора, вторым входом первого блока элементов И, вторыми информационными входами первого и иторого коммутаторов и входом элемента НЕ, выход которого соединен с входом сброса третьего накапливающего сумматора, выходы которого подключены к информационным входам устройства, выход элемента ИЛИ соединен с п ервыми управляющими «ходами первого и второго коммутаторов и входом элемента НЕ, выход которого подключен к вторым управляющим входам первого и второго коммутаторов, вьЬсод перво- го коммутатора соединен с вторым входом пятого блока элементов И, выходы которого через блок сдвига соединен с входами первой группы блока элементов ИЛИ, выходы которого соединены с информационными входами третьего накапливающего сумматора, выход второго коммутатора соединен с вторым входом шестого блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интегральных уравнений | 1987 |

|

SU1446619A1 |

| Устройство для решения линейных интегральных уравнений Вольтерры | 1985 |

|

SU1290311A1 |

| Устройство для решения интегрального уравнения измерительного преобразователя скорости потока | 1989 |

|

SU1651283A1 |

| Устройство для решения линейных интегральных уравнений (его варианты) | 1985 |

|

SU1278899A2 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Многоканальное устройство для контроля температуры | 1985 |

|

SU1328799A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения линейных интегральных уравнений | 1980 |

|

SU926682A1 |

| Устройство для решения линейных интегральных уравнений Вольтерры | 1983 |

|

SU1124322A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

Изобретение относится к цифровой вычислительной технике и применяется для решения интегральных уравнений Вольтерра-Гаммерштейна в задачах, ГП « /71fj связанных с расчетом прохождения сигналов в линиях связи, теплопереноса и т.д. Целью изобретения является повышение точности вычислений и быстродействия. Устройство содержит регистр 1 шага, первый блок элементов И 2, первьш накапливающий сумматор 3, первый блок сравнения 4, регистр 5 граничного значения, второй и третий блоки элементов И 6, 7, блок 8 вычисления ядра уравнения, четвертый блок элементов И 9, второй накапливающий сумматор 10, блок 11 вычисления подынтегральной функции, первый блок умножения 12, второй блок сравнения 13, второй блок умножения 14, элемент ИЛИ 15, элемент НЕ 16, первый коммутатор 17, пятый блок элементов И 18, элемент задержки 19, блок 20 сдвига, второй коммутатор 21, шестой блок элементов И 22, блок 23 элементов ИЛИ, третий накапливающий сумматор 24, 2 ил. «fci-Ш |Х (Л 4 1С 4

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| АНАЛОГО-ДИСКРЕТНАЯ МОДЕЛЬ ДЛЯ РЕШЕНИЯ ИНТЕГРАЛЬНЫХ УРАВНЕНИЙ | 0 |

|

SU188163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1987-02-16—Подача