Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти систем обработки информации.

Известно устройство для сопряжения источника и приемника информации, содержащее блок памяти, счетчик, триггер, элементы И, ИЛИ и НЕ, элемент задержки 1.

Однако известное устройство не позволяет осуществлять обмен информацией блоками переменной длины.

Наиболее близким по техническому решению к изобретению является устройство для сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответственно информационными входом и выходом устройства, первый элемент ИЛИ, первый элемент задержки, соединенный входом с выходом первого элемента ИЛИ и счетным входом счетчика, выход которого подключен к адресному входу блока памяти, синхронизирующим входом подключенного к выходу первого элемента ИЛИ, первый и второй входы которого являются соответственно входами синхронизации записи и чтения, второй элемент задержки, мультиплексор, первый и второй информационные входы которого подключены соответственно к информационному входу и выходу устройства, при этом выход мультиплексора подключен к информационному входу дешифратора, стробиру- ющий вход которого соединен с выходом одновибратора, вход которого соединен с выходом первого элемента задержки, первый триггер, прямой выход которого соединен с управляющим входом дешифратора и с входом записи-чтения блока памяти и является выходом разрешения записи устройства, инверсный выход первого триггера является выходом разрешения чтения устройства, вход начальной установки устройства соединен с первым . входом второго элемента ИЛИ и с входом сброса первого триггера, выход второго элемента ИЛИ сое(Л

С

00

ю ю

динен с входом сброса первого триггера, выход второго элемента ИЛИ соединен с установочным входом счетчика 2.

Недостатком известного устройства является наложение ограничений на состав данных внутри информационного блока. Если внутри информационного блока содержится слово (или слова) данных, идентичное признаку конец информационного блока, то устройство воспринимает это слово данных как признак конец информационного блока, прерывает прием информации и переключается в режим передачи информации, что ведет к потере данных.

Цель изобретения - расширение функциональных возможностей за счет снятия ограничений на состав данных внутри информационных блоков.

Цель достигается тем, что в устройство дяя сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответственно информационными входом и выходом устройства, первый элемент задержки, соединенный входом с выходом первого элемента ИЛИ и счетным входом счетчика, выход которого подключен к адресному входу блока памяти, синхронизирующим входом подключенного к выходу первого элемента ИЛИ, первый и второй входы которого являются соответственно входами синхронизации записи и чте- ния, второй элемент задержки, мультиплексор, первый и второй информационные входы которого подключены соответственно к информационному входу и выходу устройства, а выход подключен к информационному входу дешифратора, стробирующий вход которого соединен с выходом одновибратора, вход которого соединен с выходом первого элемента задержки, первый триггер, прямой выход которого соединен с управляющим входом дешифратора и с входом записи-чтения блока памяти и является выходом разрешения записи устройства, а инверсный выход является выходом разрешения чтения устройства, вход начальной установки устройства соединен с первым входом второго элемента ИЛИ и с входом сброса первого триггера, выход второго элемента ИЛИ соединен с установочным входом счетчика, введены элемент И, второй триггер, счетный вход которого соединен с выходом дешифратора, при этом выход второго триггера соединен с первым входом элемента И и входом второго элемента задержки, выход которого соединен с вторым входом элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и со счетным

входом первого триггера, установочный вход второго триггера соединен с выходом второго элемента ИЛИ.

Введение дополнительных элементов, а именно второго триггера, элемента И и их связей, позволяет не накладывать ограничений на состав данных внутри информационных блоков. Когда внутри информационного блока встречается слово данных, идентичное коду управляющего слова, но не являю- 0 щиеся им, источник информации, передавая это слово,раздваивает его, т.е.передает его два раза подряд, а управляющее слово передается один раз. В изобретении анализируется слово данных, идентичное коду 5 признака конец информационного блока, и если оно следует в блоке данных два раза подряд, то это слово квалифицируется как слово данных, которое не влияет на режим работы устройства. Если такое слово дан- 0 ных только одно, то оно квалифицируется как признак конец информационного блока и изменяет режим работы устройства.

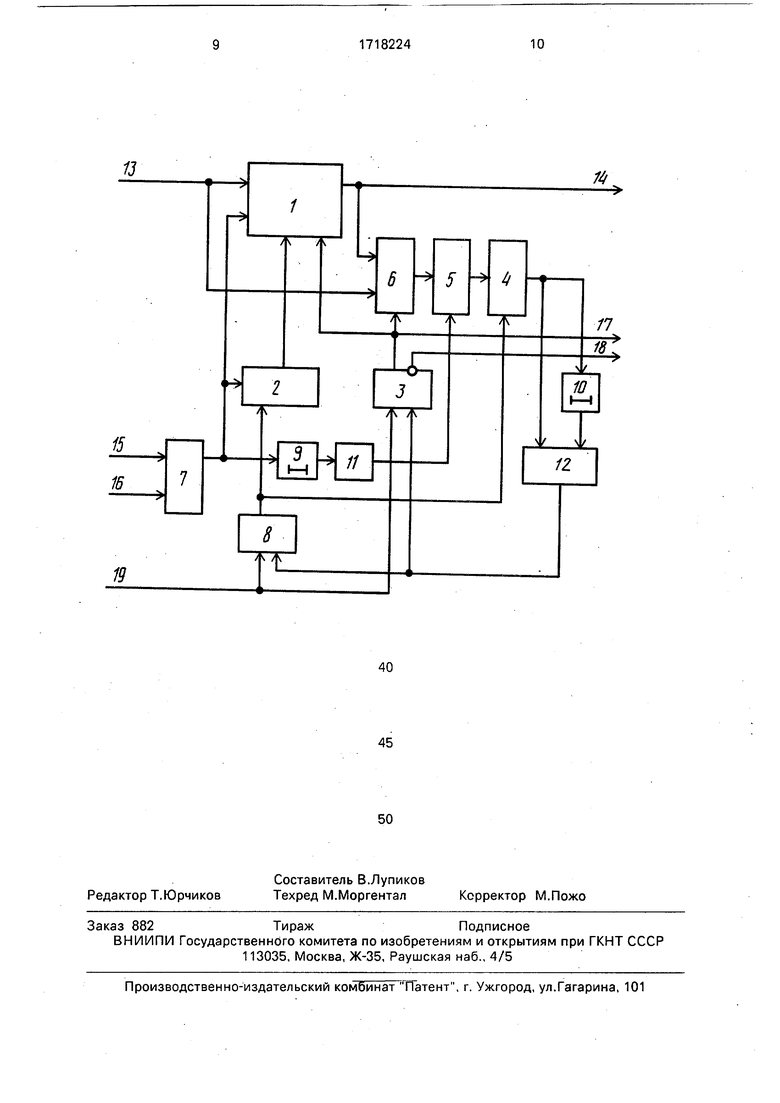

На чертеже приведена структурная схема устройства.

Устройство содержит блок 1 памяти, 5 счетчик 2, триггеры 3 и 4, дешифратор 5, мультиплексор 6, элементы ИЛИ 7 и 8, элементы 9 и 10 задержки, одновибратор 11, элемент И 12, информационные входы 13 и выходы 14, входы 15 и 16 синхронизации, выходы 17 и 18 управления, вход 19 установ- 0 ки. Информационные входы 13 и выходы 14 устройства соединены с информационными входами и выходами блока 1 памяти соответственно, адресные входы которого подключены к выходам счетчика 2. Счетный 5 вход последнего соединен с входом синхронизации обращения блока 1 памяти, входом элемента 9 задержки и выходом элемента ИЛИ 7, входы которого подключены к входам 15 и 16 синхронизации устройства. 0 Вход 19 установки устройства соединен с установочным входом триггера 3 и входом элемента ИЛИ 8, другой вход которого соединен со счетным входом триггера 3 и выходом элемента И 12. Выход элемента ИЛИ8 соединен с входом установки счетчмка 2 и входом установки триггера 4, выход которого соединен с входом элемента 10 задержки и входом элемента И 12, другой вход которого соединен с выходом элемента 10 за- 5 держки. Информационные входы первой и второй группы мультиплексора 6 соединены с информационными входами и выходами блока 1 памяти соответственно, прямой выход триггера 3 соединен с выходом 17 уп- 0 равления, входом управления режимом блока 1 памяти и входом управления типлексора 6, выход которого соединен с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1989 |

|

SU1730630A2 |

| Устройство для объединения лексических множеств | 1990 |

|

SU1795477A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| Многоканальное цифровое устройство для акустико-эмиссионного контроля | 1985 |

|

SU1329369A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

Изобретение может быть использовано при построении устройств сопряжения систем обработки информации. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения прозрачности принимаемых сообщений относительно удвоенного кода конец информационного блока. Цель достигается введением в устройство, содержащее блок памяти, мультиплексор, дешифратор, два элемента задержки, одновибратор, два элемента ИЛИ, счетчик и первый триггер, второго триггера и элемента И. 1 ил.

Л

/

/

входом дешифратора 5, выход которого соединен со счетным входом триггера 4. Инверсный выход триггера 3 соединен с. выходом 18 управления, вход стробирова- ния дешифратора 5 соединен с выходом од- новибратора 11, вход которого соединен с выходом элемента 9 задержки.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 19 установки счетчик 2, триггеры 3 и 4 устанавливаются в нулевое состояние. Низкий уровень сигнала на прямом выходе триггера 3, т.е. на выходе 17 управления, устанавливает для блока 1 памяти режим записи и запрещает приемнику информации обращаться с запросами на чтение дан- ных. Высокий уровень сигнала на инверсном выходе триггера 3, т.е. на выходе 18 управления, разрешает источнику информации обращаться с запросами на запись данных.

Записываемые данные поступают на вход 13 устройства в сопровождении сигнала на входе 15 синхронизации, который поступает через элемент ИЛИ 7 на вход синхронизации обращения блока 1 памяти и осуществляет запись данных с входов 13 в блок памяти по адресу, сформированному на счетчике 2. Задним фронтом сигнала синхронизации по входу 15 производится модификация содержимого счетчика 2, т.е. к его содержимому добавляется единица. Запись последующих информационных слов в устройстве осуществляется аналогично.

При записи каждого информационного слова анализируется его содержимое с целью фиксации появления признака конец информационного блока. Этот анализ выполняется на дешифраторе 5, входы которого соединены с выходами мультиплексора 6. В режиме записи низкий уровень сигнала на прямом выходе триггера 3, воздействуя на вход управления мультиплексора 6, обеспечивает подключение к входам дешифратора 5 информационных входов 13. На вход стробирования дешифратора 5 поступает выходной сигнал одновибратора 11, который формирует сигнал по переднему фронту сигнала на выходе элемента ИЛИ7, задержанного на элементе 9 задержки.

При появлении на информационных входах 13 информационного слова, идентичного коду признака конец информационного блока и его записи в блок 1 памятм, в момент стробирования дешифратора 5 на его выходе появляется сигнал, по заднему фронту которого триггер 4 изменяется на противоположное свое состояние (в данном

случае устанавливается в -единичное состояние). Элемент 10 задержки задерживает

сигнал, поступающий на его вход, на время большее, чем период следования импульсов синхронизации на входах 15 и 16 управления устройства, поэтому сигнал на выходе элемента И 12 не формируется. Если на информационных входах 13 появляется информационное слово, которое также идентично коду признака конец информационного блока, то в момент стробирования дешифратора 5 на его выходе

появляется сигнал, по заднему фронту которого триггер 4 изменяет свое состояние на противоположное (в данном случае устанавливается в нулевое состояние, так как триггер 4 работает в счетном режиме). Нулевой

уровень с выхода триггера 4 поступает на первый вход элемента И 12 и запрещает формирование сигнала на его выходе. Следующие подряд два информационных слова на входе 13, идентичные коду признака конец информационного блока, таковыми не являются, и запись информации в блок 1 памяти продолжается.

Если за появлением на информационных входах 13 информационного слова,

идентичного коду признака конец информационного блока, не последует следующее такое слово подряд, то триггер 4 не будет сброшен и через промежуток времени, на которое сигнал с выхода триггера 4

задержан элементом 10 задержки, на выходе элемента И 12 появляется сигнал, который, пройдя через элемент ИЛИ 8, устанавливает счетчик 2 и триггер 4 в нулевое состояние. По заднему фронту сигнала

с выхода элемента И 12 триггер 3 изменяет свое состояние на противоположное (в данном случае устанавливается в единичное со- стояние), тем самым подготавливает устройство для работы в режиме чтения. Высокий уровень сигнала на прямом выходе триггера 3, т.е. на выходе 17 устройства, разрешает приемнику информации обращаться с запросами на чтение данных, низкий уровень сигнала на инверсном выходе

триггера 3, т.е. на выходе 18 устройства, запрещает источнику информации обращаться к устройству с запросами на запись. Одиночное информационное слово, идентичное коду признака конец информационного блока, и является этим признаком.

В режиме чтения каждого информационного слова запрос приемника информации поступает на вход 16 синхронизации и, пройдя через элемент ИЛИ7, воздействует

на вход синхронизации обращения блока 1 памяти, что приводит к появлению на информационных выходах 14 информационного слова, считанного из блока 1 памяти по адресу, сформированному на выходах счетчика 2. Чтение последующих слов информационного блока в устройстве выполняется аналогично.

В режиме чтения точно так же, как и в режиме записи, производится поиск признака конец информационного блока. В этом случае к дешифратору 5 через мультиплексор 6, на входе управления которого присутствует в данный момент высокий уровень сигнала, подключаются выходные сигналы блока 1 памяти. При считывании из блока 1 памяти подряд двух информационных слов, идентичных коду признака конец информационного блока, режим чтения продолжается.

При считывании из блока 1 памяти одиночного информационного слова, идентичного коду признака конец информационного блока, что означает, что был считан признак конец информационного блока, на выходе элемента И 12 аналогично режиму записи формируется сигнал, который пройдя через элемент ИЛИ 8, устанавливает счетчик 2 и триггер 4 в нулевое состояние, а по заднему фронту сигнала с выхода элемента И 12 триггер 3 изменяет свое состояние на противоположное (в данном случае устанавливается в нулевое состояние), тем самым подготавливая устройство для работы в режиме записи данных.

Технико-экономические преимущества предлагаемого устройства заключаются в том, что при его использовании в качестве устройства сопряжения источника и приемника информации не накладывается никаких ограничений на состав данных внутри информационного блока. Это, в свою очередь, позволяет более эффективно организовать обмен данными между источником и приемником информации.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответственно информационным входом и выходом устройства, первый элемент задержки, соединенный входом с выходом первого элемента ИЛИ и

счетным входом счетчика, выход которого подключен к адресному входу блока памяти, синхронизирующим входом подключенного к выходу первого элемента ИЛИ, первый и второй входы которого являются соответственно входами синхронизации записи и чте- ния, второй элемент задержки, мультиплексор, первый и второй информационные входы которого подключены соответственно к информационному входу

устройства и выходу блока памяти, выход мультиплексора подключен к информационному входу дешифратора, стробирующий вход которого соединен с выходом одновиб- ратора, вход которого соединен с выходом

первого элемента задержки, первый триггер, прямой выход которого соединен с управляющим входом мультиплексора и с входом записи-чтения блока памяти и является выходом разрешения записи устройства, инверсный выход первого триггера является выходом разрешения чтения устройства, вход начальной установки устройства соединен с первым входом второго элемента ИЛИ и с входом сброса первого

триггера, выход второго элемента ИЛИ соединен с установочным входом счетчика, отличающееся тем, что, с целью расширения его функциональных возможностей за счет обеспечения прозрачности принимаемых сообщений относительного удвоенного кода конец информационного блока, в него введены элемент И и второй триггер, причем счетный вход и установочный вход второго триггера подключены соответственно к выходам дешифратора и второго элемента ИЛИ, вторым входом соединенного со счетным входом первого триггера и выходом элемента И, первым входом подключенного к выходу второго триггера и через

второй элемент задержки к второму входу элемента И.

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ обработки деталей | 1986 |

|

SU1653921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-03-07—Публикация

1990-01-08—Подача