1

Изобретение относится к вычисли - тельнон технике и предназначено для ускоренного вычисления функций

у

arctg -, необходимой при выполнении

X

преобразования декартовых координат в полярные координаты.

Цель изобретения - повышение точности вычислений.

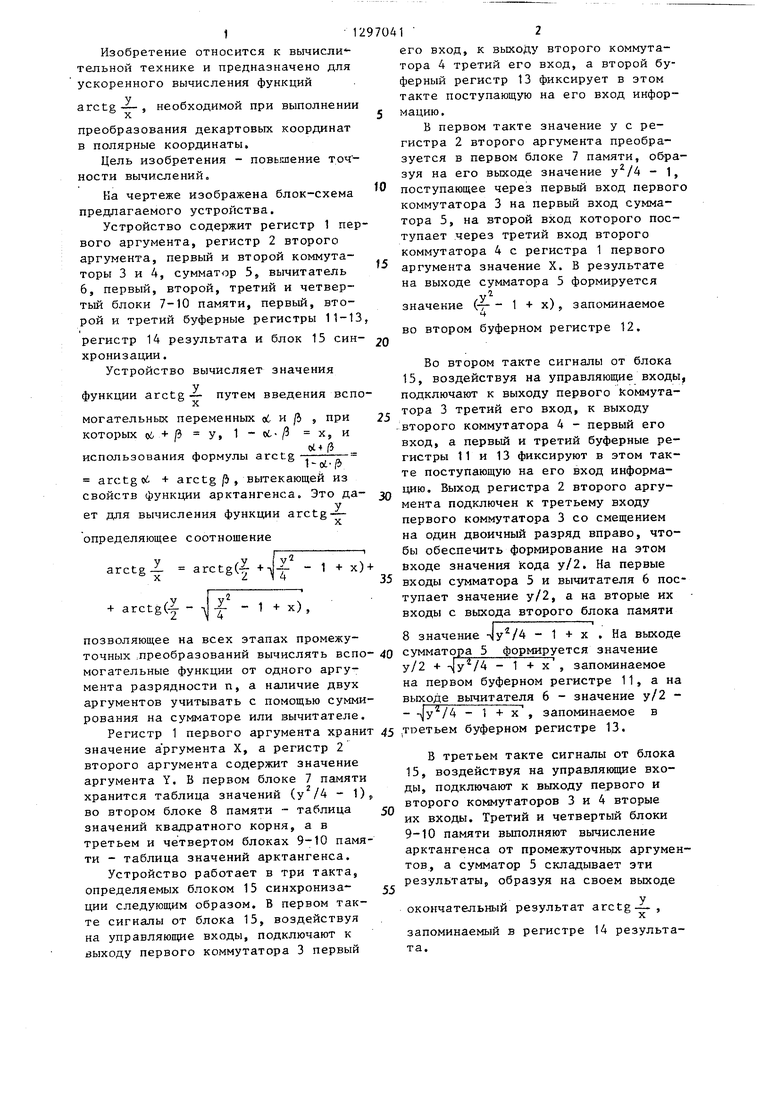

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит регистр 1 первого аргумента, регистр 2 второго аргумента, первый и второй коммутаторы 3 и 4, сумматор 5, вычитатель 6, первый, второй, третий и четвертый блоки 7-10 памяти, первый, второй и третий буферные регистры 11-13,

регистр 14 результата и блок 15 синхронизации.

Устройство вычисляет значения

В первом такте значение у с регистра 2 второго аргумента преобразуется в первом блоке 7 памяти, образуя на его выходе значение - 1, 0 поступающее через первый вход первого коммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второго коммутатора 4 с регистра 1 первого аргумента значение X. В результате на выходе сумматора 5 формируется

15

20

значение (-;- 1 + х), запоминаемое

ц

во втором буферном регистре 12.

функции arctg -

X

путем введения вспо25

30

Во втором такте сигналы от блока 15, воздействуя на управляющие входы, подключают к выходу первого Коммутатора 3 третий его вход, к выходу второго коммутатора 4 - первый его вход, а первый и третий буферные регистры 11 и 13 фиксируют в этом такте поступающую на его вход информацию. Выход регистра 2 второго аргумента подключен к третьему входу первого коммутатора 3 со смещением на один двоичный разряд вправо, чтобы обеспечить формирование на этом входе значения кода у/2. На первые 35 входы сумматора 5 и вычитателя 6 поступает значение у/2, а на вторые их входы с вькода второго блока памяти

позволяющее на всех этапах промежу-8 значение - 1 + х . На выходе

точных ;Преобразований вычислять вспо- 40сумматора 5 формируется значение

могательные функции от одного аргу-У/2 /4 - 1 + х , запоминаемое

мента разрядности п, а наличие двухна первом буферном регистре 11, а на

аргументов учитывать с помощью сумми-выходе вычитателя 6 - значение у/2 рования на сумматоре или зычитателе.-Jy/4-l+x, запоминаемое в

Регистр 1 первого аргумента хранит 45,т1эетьем буферном регистре 13.

значение а ргумента X, а регистр 2

В третьем такте сигналы от блока

15, воздействуя на управлякяцие входы, подключают к выходу первого и второго коммутаторов 3 и 4 вторые их входы. Третий и четвертый блоки 9-10 памяти вьтолняют вычисление арктангенса от промежуточньк аргуменмогательных переменных od и /5 , при которых , 1-oi,-/3 х, и

ut+ (3 использования формулы arctg --

1 Oi,- Р

arctg oi + arctg/5 , вытекающей из свойств функции арктангенса. Это даует для вычисления функции arctgX

определяющее соотношение

V

f V f t- i-t ;

arctg(|- - д -f

второго аргумента содержит значение аргумента Y. В первом блоке 7 памяти хранится таблица значений (у /4 - 1) во втором блоке 8 памяти - таблица значений квадратного корня, а в третьем и четвертом блоках 9-10 памяти - таблица значений арктангенса.

Устройство работает в три такта, определяемых блоком 15 синхронизации следующим образом. В первом такте сигналы от блока 15, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 первый

50

55

тов, а сумматор 5 складывает эти результаты, образуя на своем выходе

у

окончательный результат arctg-i- ,

запоминаемый в регистре 14 результата.

97041 2

его вход, к выходу второго коммутатора 4 третий его вход, а второй буферный регистр 13 фиксирует в зтом такте поступающую на его вход инфор- 5 мацию.

В первом такте значение у с регистра 2 второго аргумента преобразуется в первом блоке 7 памяти, образуя на его выходе значение - 1, 0 поступающее через первый вход первого коммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второго коммутатора 4 с регистра 1 первого аргумента значение X. В результате на выходе сумматора 5 формируется

15

20

значение (-;- 1 + х), запоминаемое

ц

во втором буферном регистре 12.

тов, а сумматор 5 складывает эти результаты, образуя на своем выходе

у

окончательный результат arctg-i- ,

запоминаемый в регистре 14 результата.

31

Формула изобретения Устройство для вычисления функции

у

arctg- , содержащее регистр аргумента X, регистр аргумента Y, блок син- хронизацга, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сум матора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно, с управляющими входа ми первого и второго коммутаторов, отличающее с я тем, что, с целью повышения точности, в него введены вычитатель, блок памяти значений (у /4 - 1), блок памяти значений квадратного корня, первьй и второй блоки памяти значений арктангенса, выходы которых соединены с первыми.информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента

Редактор Л.Повхан Заказ 782/52

Техред М.Ходанич Корректор Т

Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

970414

Y и регистра аргумента X соответственно, третьи информационные входы первого и Bfoporo коммутаторов сое динены с выходами блока памяти значений ( - 1) и второго буферного регистра соответственно, адресный вход блока памяти значений .( - - 1) соединен с выходом регистра аргумента Y, выходы первого и второго

fO коммутаторов соединены с входами

уменьшаемого и вычитаемого вычитате- ля соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход 15 которого соединен с адресным входом второго блока памяти значений арктангенсов, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным вхоДЬм вто20

рого буферного регистра, третий, четвертый и пятый выходы сикх- ронизации соединены с входами синхронизации соответственно первого, втог рого и третьего буферных регистров, выход первого буферного регистра соединен с адресньм входом первого блока памяти значений арктангенса.

Составитель З.Шершнева

Техред М.Ходанич Корректор Т.Колб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для ускоренного вычисления функции arctg у/х. В устройстве регистр 2 аргумента у непосредственно и через блок 7 памяти соединен со входами коммутатора 3, а регистр аргумента X соединен со входом коммутатора 4. Выходы коммутаторов подключены ко входам сумматора 5 и вычитателя 6, выход сумматора 5 связан череё регистр 11 и блок 10 памяти, а также через блок 8 памяти и регистр 12 со входами коммутатора 4. Выход вычитателя 6 через регистр 13 и блок 9 памяти соединен со входом коммутатора 3. Блоки 7, 8, 9, 10 памяти хранят таблицы промежуточных , преобразований.,. Процесс вычисления в устройстве осно.J . и ван на разложении arctg вь р arctg об + arctg fi вытекающей из свойств функции арктангенса, и pear лизуется за три такта сложения и три такта выборки из блоков памяти, 1 ил. i О) ;о

| Устройство для вычисления функций | 1982 |

|

SU1067510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-11—Подача