Изобретение относится к области автоматизации технологических процессов и касается работающего с разделением времени выполняющего несколько команд одновременно интерполятора. В известной системе fl, предназначенной для цифрового управления металлорежущими станками, каждый станок оборудован соответствующим цифровым контроллером,Который управляется управляющей вычислительной машиной. В такой системе осуществляют управление множеством цифровых контроллеров, а система становится дорогостоящей, поскольку количество управляющих осей возрастает. При этом контроллеры взаимно перекрываются и, следовательно, эффективность использования таких контроллеров невысока. Наиболее близким техническим ре.шением к изобретению является устройство для программного управления группой станков L2 , содержащее oneративное запоминающее устройство (ОЗУ) с регистром числа и регистром адреса, регистр команд, один из выходов которого соединен с входом блока переключения квадрантов, соответствующие выходы которого соединены с регистром знаков координат и оценочных функций и с регистром состояний, блок конца интерполирования, соединенный с блоком временной диаграммы интерполирования, соединенный с блоком временной диаграммы интерполятора, блок унитарных кодов, выходы которого соединены с управляющими входами одноразрядного сумматора модификации координаты и сумматора вычисления оценочной функции, управляемые входы блока коммутации слагаемых, регистра команд, регистра знаков координат и оценочных функций, регистра состояний, схемл сравнения и анализа координат и регистра числа соединены с выходами усилителей ОЗУ. Выходы схемы сравнения и анализа координат сое-динены с соответствующими входами регистра состояний, выходы блока связи с ЭВМ, устройств ввода информации, регистра команд, регистра знаков координат и оценочных функций , регистра состояний соединены с управляемыми входами регистра числа. Выходы блока коммутации результатов сложения соединены входами регистра числа и регистра знаков координат и оценочных функций. Входы одноразрядных сумматоров модификации координат

и вычислений оценочной функции соединены с соответствующими выходами блока коммутации слагаемых, а выходы с соответствующими входами блока коммутации результатов сложения. Управ гшющие входы блока коммутации слагаемых и блока коммутации результатов сложения соединены с соответствующим выходами блока унитраных кодов. Входы регистра ,адреса соединены с выходами блока приоритетов, а выходы с входами дешифратора, который соединен с соответствующими входами блока временной лвдаграммы. Выходы последнего соединены с управляющими входами регистра команд, регистра знаков координат и оценочных функций, регистра состояний, регистра числа, блока пространственного интерполирования , блока конца интерполирования, блока переключения квадрантов и блока унитарных кодов, соединенного с входами блока коммутации унитарных кодов, выходы которого соединены с входами блоков управления приводами рабочих органов, а управляющие входы блока коммутации унитарных кодов блока связи с ЭВМ и блока кoмзvIyтaции управляющих сигналов устройств ввода соединеныс выходами блока приоритетов, входы которого соединены с выходами автоматических устройств,, выходами блока конца интерполирования и блока временной диarpaMJ-Esi, Выходы блока пространственного интерполирования соединены с вхдами блока конца интерполирования -и с входами регистра команд, а входы с выходами регистра состояний и регистра команд. Выходы блока концаинтерполирования соединены с входами регистра,, состояний, а входы - с регистром команд и регистром состояний. Соответствующие выходы блока временной ди аграмкы соединены с входами блока связи с ЭВМ, блока коммутации слагаемых, регистра адреса, ОЗУ и блока управляющих сигналов устройств ввода, выходы которого соединены с-входами блока коммутации управляющих сигналов устройств ввода, а выходы последнего соединены с управляющими входаг-ли устройств ввода информации.

Недостатком данного устройства является узкая область его применения .

. Цель изобретения - расширение области применения устройства путем обеспечения возможности управления станками в режиме разделения времени

Поставленная цель достигается тем что в устройстве для программного управления группой станков, содержащем интерполятор, выходы которого соединены с первыми входами блока синхронизации, генератор импульсов и блок ручного управления, подключенный выходами к первым входам арифметического блока, а интерполятор содержит первый триггер, первый регистр первый элемент И, подключенный первым входом к выходу второго, регистра, запоминающий блок, выход которого соединен с первым входом второго элемента И, третий регистр, подключенный выходом ко входу детектора конечной точки, сумматор, первый выход которого соединен с первым входом третьего элемента И, второй триггер, подключенный входом к выходу четвертого элемента И,блок управления, первый вход которого соединен с выходом пятого элемента И, а также шестой и седьмой элементы И и элемент ИЛИ, вторые входы блока синхронизации соединены с выходом генератора импульсов, выходы - с вторыми входами арифметического блока, а в интерполятор введены блок совпадения кодов, первый коммутатор, последовательно соединенные блок счетчиков, первый переключатель и группа восьмых элементов И и последовательно соединенные дешифратор, группа девятых элементов И, блок синхронизирующих триггеров и второй коммутатор, а также второй переключатель, входы которого соединены с вторыми.входами группы восьмых элементов И, с вторым входом блока управления,с первым входом первого коммутатора и с выходами дешифратора, а выходы - с вторыми входами второго коммутатора, подсоединенного выходом к первому входу четвертого элемента И, второй выход которого соединен с выходом первого коммутатора, подключенного вторым входом к выходу детектора конечной точки. Первые входы запоминающего блока подключены к выходам группы восьмых элементов И, второй вход - к выходу шестого элемента И, а выход - к первому входу сумматора,, второй выход которого соединен с первым входом седьмого элемента И, а второй вход с первым входом шестого элемента И и через третий регистр - с выходом элемеНта ИЛИ, подключенного входами к выходам первого, второго и седьмого элементов И. Первый вход блока совпадения кодов соединен с вторым выходом блока счетчиков и с входом дешифратора, второй вход - с выходом первого регистра,а выход - с первым входом пятого элемента И,второй вход которого подключен к выходу первого триггера, третий вход блока управления соединен с третьим выходом блока счетчика, четвертый вход - с выходом второго триггера, а первый, второй, третий, четвертый, пятый и шестой выходы - с вторыми.входами второго, первого, седьмого, шестого и с третьим входом четвертого, элементов И и с вторым входом- третьего регистра соответственно. Второй вход третьего элемента И подключен к третьему

выходу блока управления, вторые входы группы девятых элементов И соединены с выходом третьего элe 1eнтa И, а вторые входы и выходы блока синхронизирующих триггеров - с тактирующими входами и выходами интерполятора соответственно,

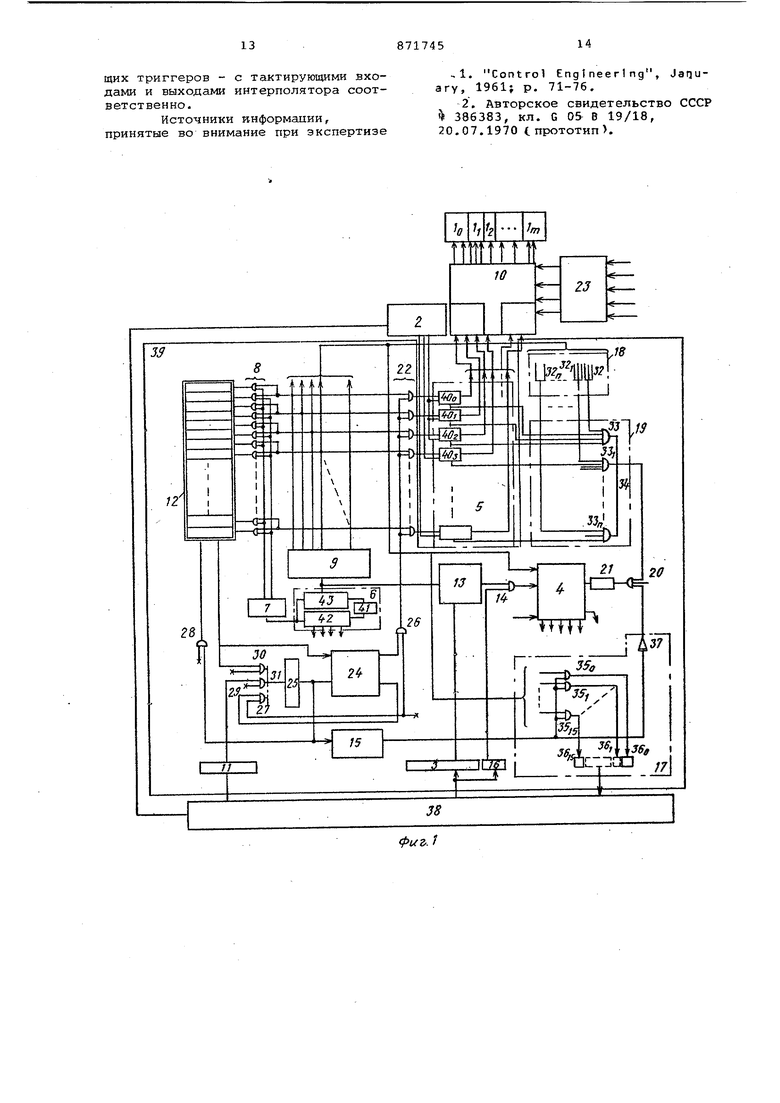

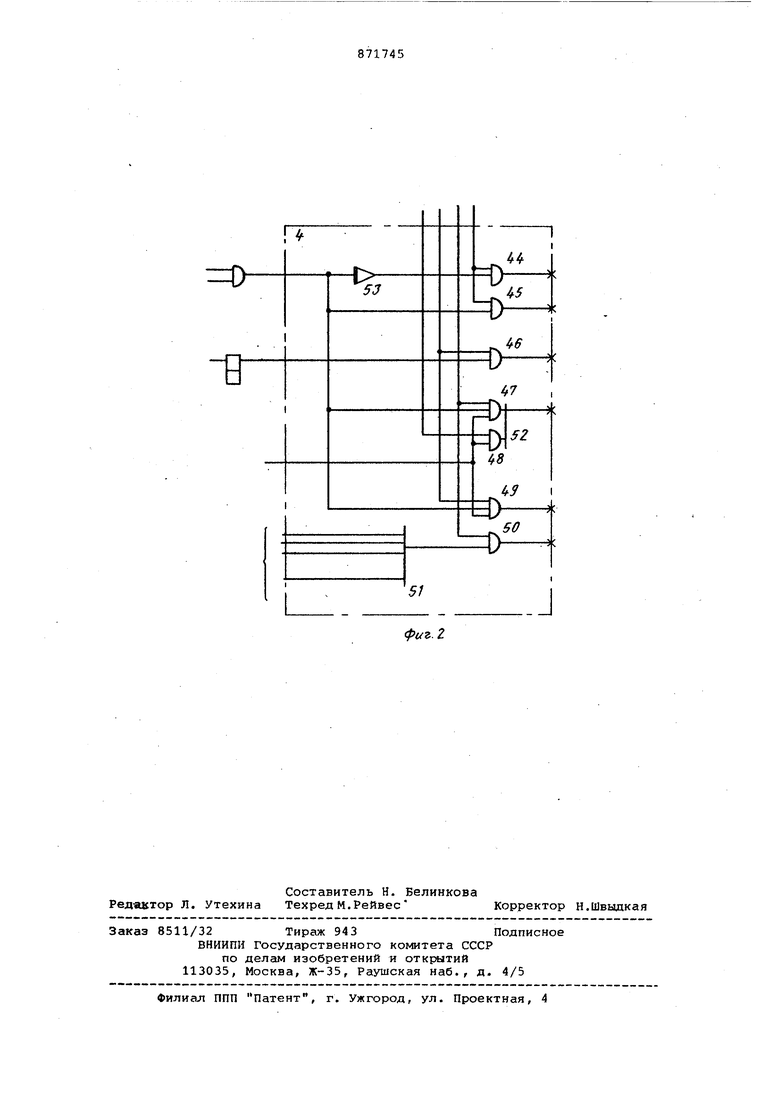

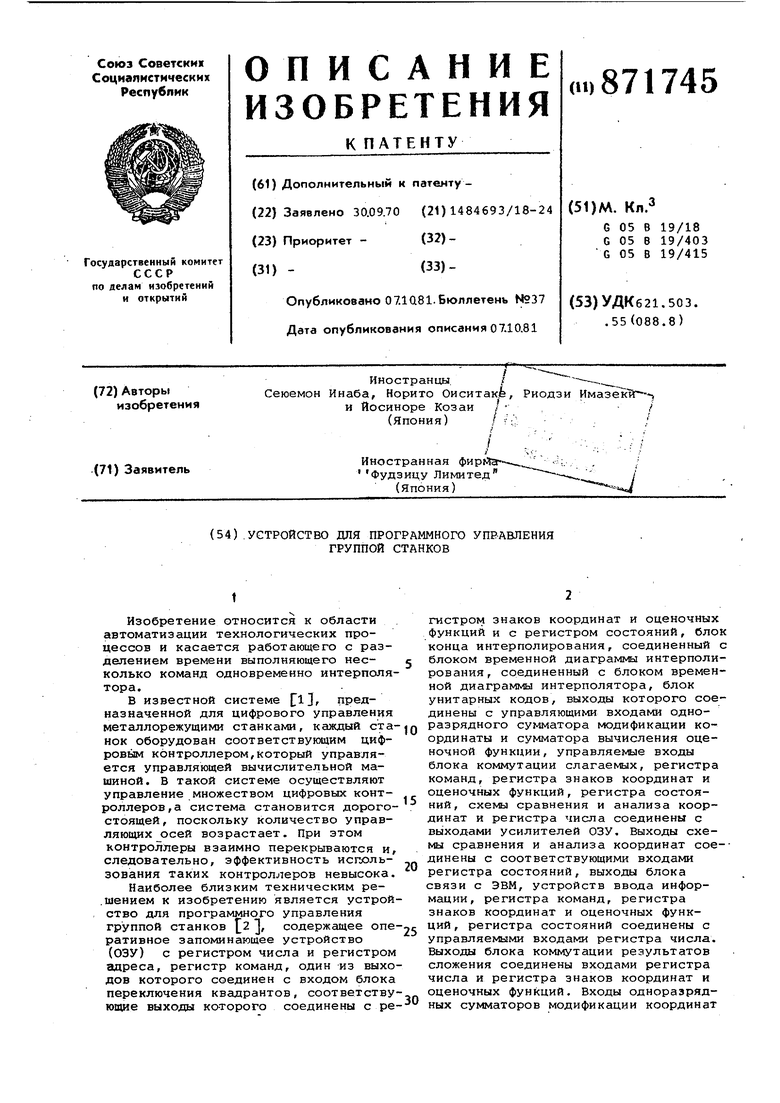

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 схема блока управления.

Устройство содержит группу станков 10 ,-lfy,,генератор 2 импульсов, первый, регистр 3, блок 4 управления, блок 5 синхронизации, блок 6 счетчиков, первый переключатель 7, группу 8 восьмых элементов И, дешифратор 9, арифметический блок 10, второй регистр 11, запоминающий блок 12, блок 13 совпадения колов, пятый элемент И 14, детектор 15 конечной точки, первый триггер 16, первый коммутатор 17, второй переключатель 18, второй коммутатор 19, четвертый элемент И 20, второй триггер 21, группу 22 девятых элементов И, блок 23 ручного управления, сумматор 24, третий регистр 25, т{5етий 26, седьмой 27, шестой 28, первый 29 и второй 30 элементы И и элемент ИЛИ 31.

Переключатель 18 состоит из элементов ИЛИ 320-32j, коммутатор 19 из элементов И ,, и элемента ИЛИ 34, коммутатор 17 - из элементов И t триггеров и инвертора 37.

Устройство также содержит блок 38 связи с ЭВМ, интерполятор 39, Бло 5 состоит из синхронизирующих триггерных схем 40Q-40 5 / э блок 6 - из генератора 41 и счетчиков 42 и 43.

Блок 4 управления содержит элементы И 44-50, элементы ИЛИ 51, 52 и инвертор 53.

Устройство работает следующим образом.

При количестве управляемых осей из множества управляемых станков п.1 работающий, с разделением времени интерполятор выполняет несколько команд одновременно. Количество (п+1 цифровой информации, т.е. команд, касающихся количества движения ( j соответстующих количеству (п+1) управляемлх осей, поступают на выполняющий одновременно несколько команд интерполятор 39 , а импульсы, количество которых равно этой команде, посылается к (п+1) выходным терминалам, соответствующих осям. Например, сигнал OF на выходе интерполятора 39 соответствует входному сигналу IP, и сигнал ОРд отбирается как серия импульсов с числом, равным цифровой величине, представленной входным сигналом интерполятора д. Арифметические операции для отправления выходных импульсов осуществляютс в соответствии с принципом разделения времени, и повторяются определенное количество раз, например, в тако порядке: нулевая ось, первая ось, вторая ось ... -я ось в блоке 10. Количество (п+1) выходных данных (команды, касающиеся скорости) f-, соответствующие вводам интерполятора 39 поступают на генератор 2 с блока 38. При этом серии импульсов частота которых пропорциональна команде, генерируются в (п+1) количестве выходных терминалов генератора 2. Например, один из выходов генератора 2 соответствует вводу fg и представляет собой серию импульсов, частота которой пропорциональна команде представленной вводом fg . Блок 5 сначала накапливает выходные импульсы с интерполятора 39, а затем посылает их синхронно с выходными импульсам с генератора 2. Выходные сигналы OPQ , OFf , OF , .. . с интерполятора 39 посылаются на выходы блока 5 синхронно с соответствующими выходными сигналами FPo ,FP-ir РРз - FPvi с генератора 2. Блок 10 имеет (п + 1) выходных терминалов, соответствующих сериям выходных импульсов So, S, 82, ...Sy-, блока 5, и сглаживает импульсы, напрмер, серии импульсов SQ таким образо чтобы превратить эту последовательность импульсов в серию импульсов, не имеющую быстрой смены частоты, и посылает их на выход устройства (на станки l ... ly,). Аналогичные операции осуществляются на других: осях. В устройстве, показанном на фиг. 1, нулевую, первую и вторую ось используют для управления осями одного станка, требующего одновременного управления по трем осям. Аналогично четвертую ось из числа п осей используют для управления несколькими другими станками. Команда поступает с вычислительной машины через блок 38 на интерполятор 39 и на генератор 2 каждый- раз после того, как закончена арифметическая операция распределения одного блока, в отнощении которого осуществлено распределение импульсов.

Запоминающий блок содержит 16 регистров 16 регистров CQ-C соответствующих 16 осям О до 15, соответственно.

Генератор 41 синхронизирующих импульсов X, счетчик 42, счетчик 43, переключатель 7 и дешифратор 9 образуют цепь выбора оси.

Регистры блока 12 можно выбрать с помощью сигнала от элемента И из группы 8. Импульсы от генератора 41 подаются на вход четвертичного счетчика 42 и, когда он совершает один раз полный цикл счета, один импульс подсчитывается счетчиком 48. Счетчик 43 является двоичным счетчиком с четырьмя битами, имеющими 16 видов состояний и формирующим на выходе сигналя соответственно Н,,-}} , соответствующие содержимому счетчика Переключатель 7 является селектором, содержащим простую логическую схему для формирования сигнала 1 на выходе 5 , когда состояние счетчика 42 соответствует Тд или и, для формирования сигнала 1, посыла емого на выход $2, когда состояние счетчика 42 соответствует Т или Т. Поэтому в соответствии с режимом, при котором содержимое счетчика 42 изменяется от Т до Т при формировании сигналсз-Нд, обозначающего ось NO, происходит выбор регистров блока 12 в следующем порядке. Ад-регистр, Со-регистр., А -регистр. Затем, когда счетчиком 43 считывается 1 от дешифратора 9 поступает сигнал Н и в то время, когда содержимое счетчика 42 изменяется от Т до Т, выбор регистров блока 12 производится в сл дующем порядке- А -регистр, C;f-peгистр, А -регистр. Последующие регистры выбираются .аналогично. Сигнгшы от дешифратора 9, предназначенные для переключения номеров соответствующих осей, поступают на элементы И группы 22, соответствующие определенным осям, и поэтому/ если распределительные импульсы генерируются в результате осуществления арифметической операции, то эти импульсы направляются на выходную сторону через элемент И группы 22 набираемлй дешифратором 9. Регистр 25, сумматор 24, элементы И 26-30 и элемент ИЛИ 31 образуют, цифровой узел, который является общим для всех осей. Элемент 26 предусмотрен для формирования импульсов которые вырабатываются в резуль тате совершения арифметической oneрации для подачи на элементы И группы 22, а элемент 28 предусмотрен для обеспечения записи содержимого регис ра 25 в выбранный регистр блока 12. С помощью элемента И 30 пересылается содержимое выбранного регистра блока 12 в регистр 25. Элемент 29 использу ется для пересылки цифровой информации, хранящейся в регистре 11, в регистр 25, а элемент И 27 - для пересьзлки результата добавления сумматором 24 в регистр 25. Сигналы, соотве ствующие командам, относящимся к колрчесхву движения для обозначенных осей и к адресам осей, направляются Нб1|осредственно от операционной части вычислительной машины через блок 38 в регистры 11 и 3. Когда дешифратор 9 формирует сигнал , и выбирается ось О, содержимое регистра ( CQ)блока 12 добавляется к содержимому регистра (AQ), и полученный результат запоминается в регистрах блока 12, если в сумматоре 24 формируется импульс, обеспечивающий переполнение счета, то этот импульс используется в качестве распределительного импульса. Если арифметическая операция повторяется с постоянным периодом, то импульс,, обеспечивающий переполнение счета, генерируется с частотой которая пропорциональна соответствующим командам (содержимому С -регистра блока 12} . В данном устройстве арифметическая операция осуществляется в соответствии с принципом разделения времени для каждой из осей, поэтому, когда заканчивается добавление для оси О, в качестве следующей оси выбирается ось 1, и осуществляется аналогичная операция, и т.д. послег довательно для каждой из осей. Когда заканчивается операция для оси 15, аналогичная операция повторяется для оси О. Детектор 15 предусмотрен для обозначения оси, например оси О, и для обнаружения того, что импульсы, число которых соответствует командной информации регистра.( GO) для этой оси, были посланы на сторону вывода, т.е. для детектирования конечной точки. При этом детектор обнаруживает результат сложения (сумму;, накопленный в регистре 25 каждый раз, когда добавление имеет место. Когда эта величина достигает значения 1000 ... Ох, на выходе детектора 15 формируется сигнал детектирования конечной точки 1. Формирование этого сигнала основывается на том принципе, что если поступает еще .один бит в дополнение к минимальному биту командной информации и эта операция обеспечивает получение 1 (данные рассматриваются в качестве командной информации и затем добавляется к содержимому регистра, то обеспечивается формирование импульсов, обеспечивающих переполне-ние счета, число которых равно командной информации. Причем формирование происходит, когда накопленное значение, достигает величины, равной 100 ... О . Блок 13 формирует и посылает команду управления передачей к блоку 4 через элемент И 14 в момент времени, когда адрес, указанный для регистра 3, совпадает с содержимым счетчика 4.3, т.е. с адресом оси. В этот момент блок 4 запоминает содержимое регистра 11, которое соответствует новой командной информации, а регистры блока 12 - оси, определенной регистром 3, через элемент И 29, регистр 25 и элемент И 28, и обнуляет соответствующий регистр , блока 12. Блок 5 содержит триггерные схемы -15 которые соответствуют 16 осям. При этом каждая ось может накапливать три обеспечивающих переполнение сч.ета импульса в максимуме для оси и формиро ватель ббеспечивающий переполнение счета импульс к стенкам 1-0 синхронн с питающим импульсом,поступающим с г нератора 2.Следовательно,из числа импульсов, оставшихся в блоке 5, вычитается один импульс. В результат распределительные импульсы интерполятора 39 могут посылаться последовательно синхронно с питающими импульсами. В устройстве, приведенном на фиг. 1, используются для одновременного управления по трем осям управляемого станка три оси (О, 1и 2, а оси 3, 4 и 5 используются для управления другим станком). Отсюда следует, что когда одна из синхронизирующих триггерных схем 40, 40, 40 блока 5 заполнена, т.е. запомнила три оставшихся импульса, необходи мо предотвратить дальнейшую арифметическую операцию по распределению импульсов, и для этой цели предусмот рены коммутатор 19 и переключатель 18. Переключатель 18 предназначен для того, чтобы привести номер оси дешифратора 9 в соответствие с номером станка. При этом сигналы дешифратора 9 объединены в несколько групп с помощью элементов ИЛИ Когда ни одна из схем 40, использованных для управления станком нокюр О, не заполнена (Full) и выбирается арифметическая операция для осей 0-2 на выход коммутатора 19 посылается сигнал 1. Такой метод также исполь зуется при работе с другими станками. Если один из синхронизирующих триггеров осей, используемых для управления станками, заполнен, то сигнал на выходе коммутатора 19 станови ся равным О, при этом арифметическая операция по распределению импуль сов, относящихся к осям, принадлежащим этому станку, прекращается немед ленно. Коммутатор 17, обеспечивающий зап рос и передачу данных, содержит 16 элементов И , на входы которых поступают сигналы Н(, дешифратора 9 и сигналы с выхода детектора 15, и триггеры , обеспечивающие запрос передачи данных,которы размещены в соответствии с выходами вентилей. При обнаружении конечной точки триггер коммутатора 17, обеспе чивающий передачу данных соответствующего станка, включается изапрашивает следующую командную информа цию от ЭВМ через блок 38. Блок 4 управляет работой группы элементов И 26-30, так что-включение триггера 21 можно осуществить через элемент И 20 и заданная арифметическая операция может, быть выполнена в том случае, если сигнал GEX на элемент И 20 по,дается в момент времени, когда не достигнута конечная точка и на выходе коммутатора 19 возникает выходной сигнал 1. Цикл передачи в устройстве осуществляется следующим образом. После поступления командной Информации и адреса оси непосредственно в регистр 11 типа D и в буферный регистр 3 типа AR соответственно, из оперативной части вычислительной машины с блока 38 выходной сигнал триггера 16 становится равным 1, Если счетчик 43 продолжает вести отсчет и содержимое счетчика 43 совпадает с содержимым регистра 3, блок 13 генерирует сигнал совпадения. При этом сигнал управления передачей посылается в блок 4 для управления арифметической операций через элемент И 14 и начинается цикл передачи. . В момент TO сигнал GOB с выхода блока 4 открывает элемент И 29 по сигналу TQ со счетчика 42, и командная информация, накопленная в регистре 11, передается в регистр 25. В момент Т. может быть получен сигнал GWT на выходе блока 4, и содержимое регистра 25 (командная информацияЛ записывается в регистре С блока 12 оси, заданной в этот момент через элемент И 28. В момент Т2 при поступлении соответствующего тактового импульса на выходе счетчика 42 может быть получен сигнал 8CLR на выходе блока 4 и регистр 25 сбрасывается в нулевое состояние. В момент т через элементы И 47 и 48 и элемент ИЛИ 52 блока 4 на выходе этого блока может быть получен сигнал GWT. По этому сигналу содер-. жимое регистра 25 ) записывается в соответствующий регистр Cfj-C f блока 12 упомянутой оси, а регистры (5-блока 12 обнуляются. Таким образом, командная информация, заданная буферному регистру 11, хранится в регистре С блока 12, который соответствует адресу оси, заданному регистру 3, а регистр А блока 12 этой же оси очищен, при этом можно осуществить отправку командной информации. Эту посылку командной информации можно осуществить независимо и безотносительно , к арифметической операции распределения по другим осям. Арифметическая операция в интерполяторе осуществляется следующим образом. Одна ось, например содержимое регистра .a 12, передано в регистр 25, а содержимое регистра блока 12 считано и прибавлено к содержимому регистра 25. Результат записан в регистр 25, далее переписан в регистр Если в течение этого периода времени возникает импульс переполнения то он запоминается в синхронизирующей триггерной схеме блока 5. Сигнал управления GAB элементом И 30 может быть получен, и содержимое регистров Ад-Ау блока 12 отведенной оси переносится на регистр 25 через элемент И 44, Например, если будет иметь место выходной сигнал Н на дешифраторе 9, содержимое регистра Ар блока 12 передается регистру 25. В момент Т1 может иметь место сигнал управления БА элементом И 20 и если ни одна из схем 4 не взведена, вырабатывается сигнал GEX для управления выполнением арифмети ческой операции. В момент Т2 вырабатывается сигна управления элементам И 27, открывает ся этот элемент, содержимое выбранного регистра блока 12 и содер .жимое регистра 25 складываются в сум маторе 24, и результат передается tчерез элементы 27 и 31) и хранится в регистре 25. Если вырабатывется им пульс переполнения в это же время, т он хранится в соответствующей схеме 40o-40 f , куда передается через элемент И 26 и соответствующий элемент И группы 22. в момент Тз вырабатывается сигн управления элементом И 28 и содержи мое регистра 25 записывается в ре.гистр А А 5-блока 12, предназначенн выбранной оси, например 10, посредством элемента И 28. Когда счетчик 42 возвращается в момент Тр и 1 подсчитывается счетчиком 43 ,выбира ся следующая ось, и выполняется та же арифметическая операция. Использование данного устройства в системах управления станками позволяет значительно расширить обдаст их использования. Формула изобретения Устройство для программного управления группой станков, содержащее интерполятор, выходы которого соединены с первыми входами блока синхронизации, генератор импульсов и блок управления, подключенный выходйми к первым входам арифметическогЬ блока, а интерполятор содержит первый триггер, первый регистр, первый элемент И, подключенный первцм входом к выходу второго регистра, запоминающий блок, выход которого соединен с первым входом второ го элемента И, третий регистр, подключенный выходом к входу детектора конечной, точки, сумматор, первый вы .ход которого соединен с первым вход третьего элемента И, второй триггер подключенный входом к выходу четвертого элемента И, блок управления,, первый вход которого соединен с выходом пятого элемента И, а также шестой и седьмой элементы И и элемент ИЛИ, отличающееся тем,, что, с целью расширения области применения устройства путем обеспечения возможности управления станками в режиме разделения времени, в устройстве вторые входы блока синхронизации соединены с выходом генератора импульсов, выходы - с вторыми входами арифметического блока, а в интерполятор введены блок совпадения кодов, первый коммутатор, последовательно соединенные блок счетчиков, первый переключатель и группа восьмых элементов И и последовательно соединенные дешифратор, группа девятых элементов И, блок синхронизирующих триггеров и второй коммутатор, а также второй переключатель, входы которого соединены с вторыми входами группы восьмых элементов И, с вторым входом блока управления, с первым входом первого коммутатора и с выходами дешифратора, а выходы с вторыми входами второго коммутато-ра, подсоединенного выходом к первому входу четвертого элемента И, второй выход которого соединен с выходом первого коммутатора, подключен-ного BTopEiM входом К ВЫХОДУ детектора конечной точки, первые входы запоминающего блока подключены к выходам группы восьмлх элементов И, второй вход - к выходу шестого элемента И, а выход - к первому входу сумматора, второй выход которого соединен с первым входом седьмого элемента И, а второй вход - с первым входом шестого элемента И и через третий регистр с выходом элемента ИЛИ, подключенного входами к выходам первого, второго и седьмого элементов И, первый вход блока совпадения кодов соединен с вторым выходом блока счетчиков и с входом дешифратора, второй вход - с выходом первого регистра, а выход - с первым входом пятого элемента И, второй вход которого подключен к выходу первого триггера, третий вход блока соединен с третьим выходом блока счетчиков, четвертый вход - с выходом второго триггера, а первый, второй, третий, четвертый, пятый и шестой выходы с вторыми входами второго, первого, седьмого, шестого и с третьим входом четвертого элементов И и с вторым входом третьего регистра соответственно, второй вход третьего элемента И подключен к третьему выходу блока управления, вторые входы группы девятых элементов И соединены с выходом третьего элемента И, а вторые входы и выходы блока синхронизирующих триггеров - с тактирующими входами и выходами интерполятора соответственно.

Источники йнформадии, принятые во внимание при экспертизе

-1. Control Engineering, Jarjuагу, 1961; p. 71-76.

2. Авторское свидетельство СССР 386383, кл. G 05 В 19/18, 20.07.1970 С прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ ГРУППОЙ ЕДИНИЦ ТЕХНОЛОГИЧЕСКОГО ОБОРУДОВАНИЯ | 1991 |

|

RU2020537C1 |

| Линейный интерполятор | 1979 |

|

SU819796A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1615744A2 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Система программного управления станками | 1985 |

|

SU1328792A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1989 |

|

SU1777144A1 |

фиг. г

Авторы

Даты

1981-10-07—Публикация

1970-09-30—Подача