Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах при обработке радиолокационных сигналов, решении задач распознавания.

Целью изобретения является упрощение сумматора.

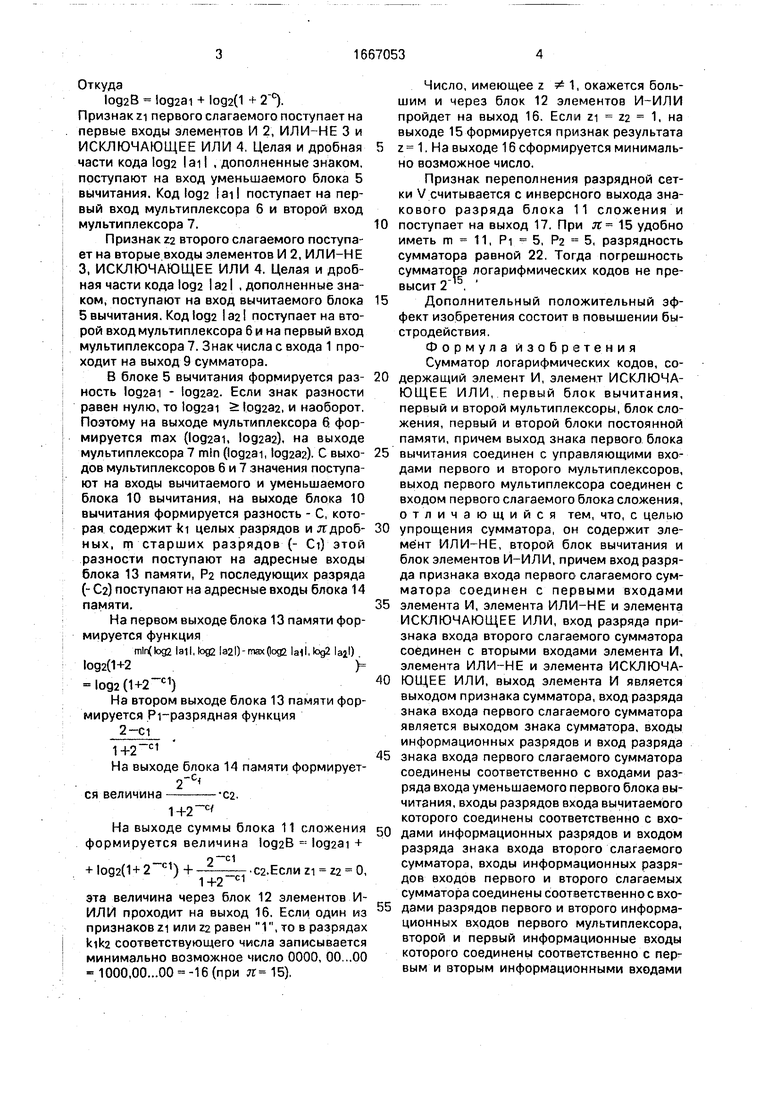

На чертеже представлена схема сумматора логарифмических кодов.

Сумматор содержит вход 1 первого слагаемого сумматора, элемент И 2, элемент ИЛИ-НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первый блок 5 вычитания, первый и второй мультиплексоры 6 и 7, вход 8 второго слагаемого сумматора, выход 9 знака сумматора, второй блок 10 вычитания, блок 11 сложения, блок 12 элементов И-ИЛИ, первый и второй блоки 13 и 14 постоянной памяти, выход 15 признака сумматора, выход 16 суммы сумматора, выход 17 переполнения сумматора.

Сумматор логарифмических кодов предназначен для сложения двух чисел с одинаковыми знаками, представленными в логарифмических кодах. Логарифмический

код некоторого числа at есть xi (092tail. Так как 0 lai | 1, то 0 xi -1од2Я, где я- разрядность числа а. Логарифмический код xi имеет следующий формат

sign z kik2,

где в однобитовом поле sign записывается знак числа ai, в однобитовом поле z записывается код 1, если ai 0, в поле ki, имеющем 1одалг разрядов, записывается целая часть Iog2 lai I , в поле К2, имеющем я разрядов, записывается дробная часть Iog2 jail . При 4, К2 15 и логарифмический код х 1 содержит21 разряд. Знак Iog2 lail всегда отрицателен и поэтому не записывается.

Сумматор работает следующим образом.

Пусть необходимо найти сумму В ai + 32. На входы устройства 1 и 8 приходят логарифмические коды чисел ai и аз. Необходимо найти логарифмический код суммы В

2 °92В 2l°gai j 21о9а2

Выберем max(logai, Ioga2). Пусть logai Ioga2. Тогда

2l°92B f - + 2lo9a2 logai 2loga1(1 ).

Ё

О

о

J

о

ел со

Откуда

IOQ2B 109231 + IOQ2(1 + ).

Признак zi первого слагаемого поступает на первые входы элементов И 2, ИЛИ-НЕ 3 и ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Целая и дробная части кода Iog2 lai I , дополненные знаком, поступают на вход уменьшаемого блока 5 вычитания. Код Iog2 lai I поступает на первый вход мультиплексора 6 и второй вход мультиплексора 7.

Признак Z2 второго слагаемого поступает на вторые входы элементов И 2, ИЛИ-НЕ 3, ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Целая и дробная части кода Iog2 Ia2l .дополненные знаком, поступают на вход вычитаемого блока 5 вычитания. Код Iog2 1321 поступает на второй вход мультиплексора 6 и на первый вход мультиплексора 7. Знак числа с входа 1 проходит на выход 9 сумматора.

В блоке 5 вычитания формируется разность Iog2ai - 1од2Э2. Если знак разности равен нулю, то Iog2ai 1од2Э2, и наоборот. Поэтому на выходе мультиплексора 6. формируется max (Iog2ai, 1од2Э2), на выходе мультиплексора 7 mln (Iog2ai, Iog232). С выходов мультиплексоров 6 и 7 значения поступают на входы вычитаемого и уменьшаемого блока 10 вычитания, на выходе блока 10 вычитания формируется разность - С, которая содержит ki целых разрядов и п дробных, m старших разрядов (- Ci) этой разности поступают на адресные входы блока 13 памяти, 2 последующих разряда (- С2) поступают на адресные входы блока 14 памяти.

На первом выходе блока 13 памяти формируется функция

гоЦ1од2 Iail,log2 Ia2)-max(fog2 Iall,log2 lajl)

log2(1+2)

-Iog2()

На втором выходе блока 13 памяти формируется Pi-разрядная функция 2-ci

1+2

-С1

На выходе блока 14 памяти формирует,-с.

ся величина

С2.

На выходе суммы блока 11 сложения формируется величина log2B Iog2ai +

+ 1од2(1+2 С1)+-С2.Еслиг1 г2 0,

1+2 с1

эта величина через блок 12 элементов И- ИЛИ проходит на выход 16. Если один из признаков zi или Z2 равен 1, то в разрядах kika соответствующего числа записывается минимально возможное число 0000, 00...00 -1000,00...00 -16 (при ).

Число, имеющее z M, окажется большим и через блок 12 элементов И-ИЛИ пройдет на выход 16. Если zi Z2 1. на выходе 15 формируется признак результата

z 1. На выходе 16 сформируется минимально возможное число.

Признак переполнения разрядной сетки V считывается с инверсного выхода знакового разряда блока 11 сложения и

0 поступает на выход 17. При к 15 удобно иметь m 11, Pi 5, г 5, разрядность сумматора равной 22. Тогда погрешность сумматора логарифмических кодов не превысит 2 .

5Дополнительный положительный эффект изобретения состоит в повышении быстродействия.

Формула изобретения Сумматор логарифмических кодов, со0 держащий элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый блок вычитания, первый и второй мультиплексоры, блок сложения, первый и второй блоки постоянной памяти, причем выход знака первого блока

5 вычитания соединен с управляющими входами первого и второго мультиплексоров, выход первого мультиплексора соединен с входом первого слагаемого блока сложения, отличающийся тем, что, с целью

0 упрощения сумматора, он содержит элемент ИЛИ-НЕ, второй блок вычитания и блок элементов И-ИЛИ, причем вход разряда признака входа первого слагаемого сумматора соединен с первыми входами

5 элемента И, элемента ИЛИ-НЕ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход разряда признака входа второго слагаемого сумматора соединен с вторыми входами элемента И, элемента ИЛИ-НЕ и элемента ИСКЛЮЧА0 ЮЩЕЕ ИЛИ, выход элемента И является выходом признака сумматора, вход разряда знака входа первого слагаемого сумматора является выходом знака сумматора, входы информационных разрядов и вход разряда

5 знака входа первого слагаемого сумматора соединены соответственно с входами разряда входа уменьшаемого первого блока вычитания, входы разрядов входа вычитаемого которого соединены соответственно с вхо0 дами информационных разрядов и входом разряда знака входа второго слагаемого сумматора, входы информационных разрядов входов первого и второго слагаемых сумматора соединены соответственно с вхо5 дами разрядов первого и второго информационных входов первого мультиплексора, второй и первый информационные входы которого соединены соответственно с первым и вторым информационными входами

второго мультиплексора,выход которого соединен с входом уменьшаемого второго блока вычитания, вход вычитаемого которого соединен с выходом первого мультиплексора и с первым входом первой группы блока элементов И-ИЛИ, выход которого является выходом суммы сумматора, выход переполнения которого соединен с инверсным выходом знака блока сложения, выходы старших и младших разрядов выхода второго блока вычитания соединены соответственно с адресным входом первого блока постоянной памяти и с первым адресным

входом второго блока постоянной памяти, первый и второй выходы первого блока постоянной памяти соединены соответственно с входом второго слагаемого блока сложения и с вторым адресным входом второго блока постоянной памяти, выход которого соединен с входом третьего слагаемого блока сложения, выход суммы которого соединен с первым входом второй группы блока элементов И-ИЛИ, выходы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ИЛИ-НЕ соединены соответственно с вторыми входами первой и второй групп блока элементов И-ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор логарифмических кодов | 1990 |

|

SU1730619A1 |

| Устройство для возведения в степень | 1984 |

|

SU1228101A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

| Формирователь логарифмического кода | 1989 |

|

SU1693604A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является упрощение сумматора. Сумматор содержит элемент И 2, элемент ИЛИ - НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первый и второй блоки 5 и 10 вычитания, первый и второй мультиплексоры 6 и 7, блок 11 сложения, блок 12 элементов И - ИЛИ, первый и второй блоки 13 и 14 постоянной памяти со связями. 1 ил.

т

РГ Р.2 .

14 J

| Устройство для сложения в избыточной системе счисления | 1986 |

|

SU1365077A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-09-27—Подача