Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах общего и специализированного назначения.

Цель изобретения - повышение быстродействия устройства и его упрощение.

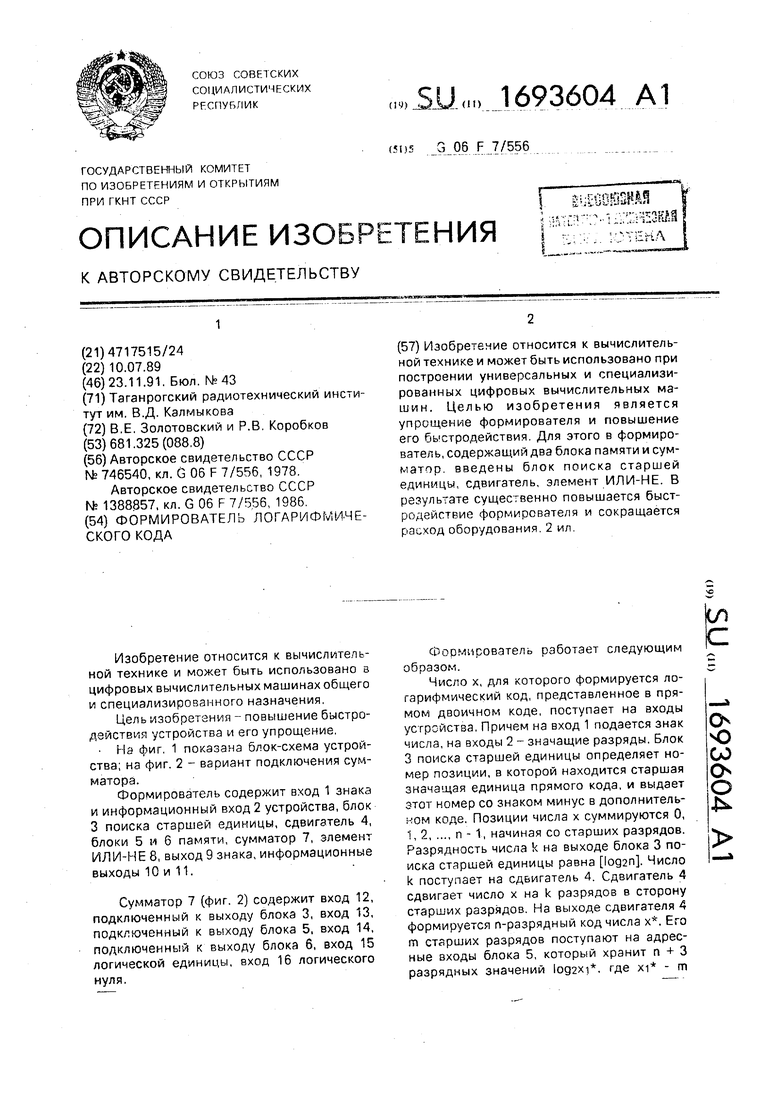

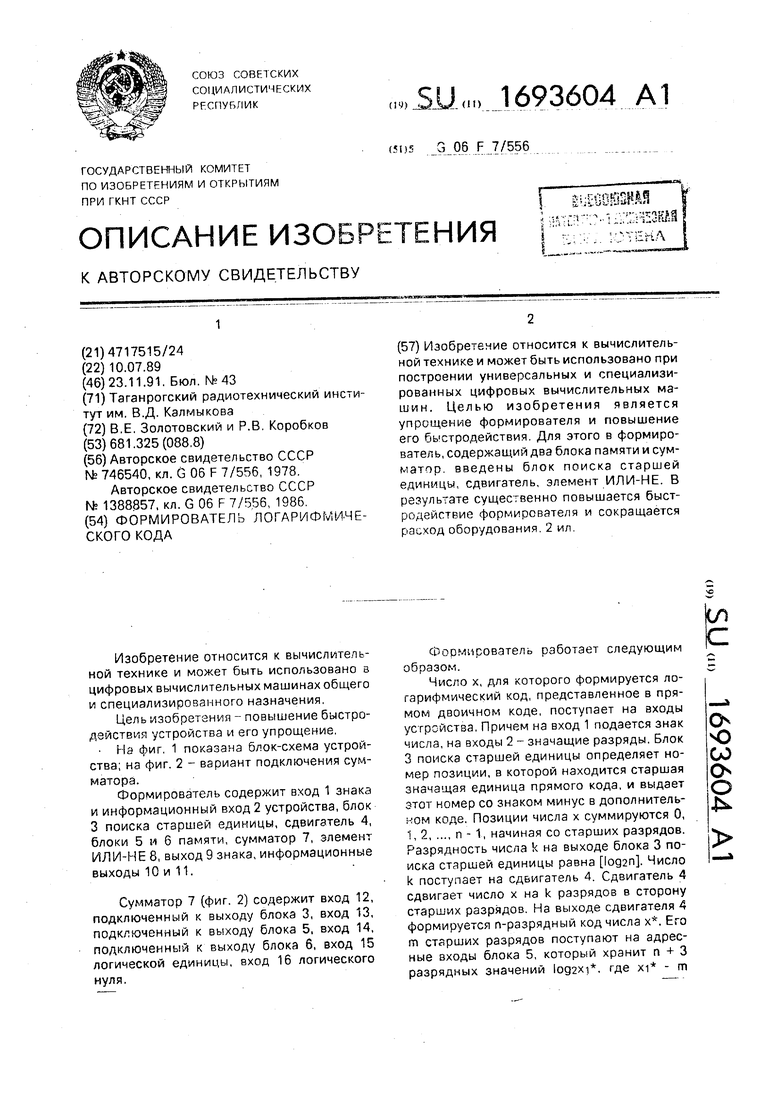

На фиг. 1 показана блок-схема устройства; на фиг. 2 - вариант подключения сумматора.

Формирователь содержит вход 1 знака и информационный вход 2 устройства, блок 3 поиска старшей единицы, сдвигатель 4, блоки 5 и 6 памяти, сумматор 7, элемент ИЛИ-НЕ 8, выход 9 знака, информационные выходы 10 и 11.

Сумматор 7 (фиг. 2) содержит вход 12, подключенный к выходу блока 3, вход 13, подключенный к выходу блока 5, вход 14, подключенный к выходу блока 6, вход 15 логической единицы, вход 16 логического нуля.

Формирователь работает следующим образом.

Число х, для которого формируется логарифмический код, представленное в прямом двоичном коде, поступает на входы устройства. Причем на вход 1 подается знак числа, на входы 2 - значащие разряды. Блок 3 поиска старшей единицы определяет номер позиции, в которой находится старшая значащая единица прямого кода, и выдает этот номер со знаком минус в дополнительном коде. Позиции числа х суммируются О,

1, 2п - 1, начиная со старших разрядов.

Разрядность числа k на выходе блока 3 поиска старшей единицы равна Iog2n Число k поступает на сдвигатель 4. Сдвигатель 4 сдвигает число х на k разрядов в сторону старших разрядов. На выходе сдвигателя 4 формируется n-разрядный код числа х. Его m старших разрядов поступают на адресные входы блока 5, который хранит п + 3 разрядных значений loo,2xi, где xi - m

(Л

с

о чэ со о

2

старших разрядов числа х. На адресные входы блока 6 поступают Х2 - р старших разрядов х, и n -m и младших разрядов х.

В блоке 6 хранятся значения

численные до n + 3-го разряда. Число k из сдвигателя 4, величины из блоков 5 и 6 поступают на входы сумматора 7. Число х поступает на входы элемента 1/1ЛИ-НЕ 8, который формирует признак z 1, если х 0. С выхода 9 считывается знак логарифмического кода sign у, с выходов 10 считывается сам логарифмический код, с выхода 11 считается признак z.

Сумматор приведен для случая, когда n 15, m 11, р 7.

Формирователь предназначен для формирования логарифмического кода числа х. Логарифмический код числа х содержит следующие разряды: один разряд для представления признака z; один разряд для представления знака числа; logan разрядов для представления целой части логарифмического кода; n разрядов для представления дробных разрядов логарифмического кода.

Так как I х i 1, то у од2 х О, поэтому знак у опускается.

В настоящее время существует досо- точно широкий круг задач, требующих вычисления суммы произведений иида

m n Ј (Пхи).

J 11 1

Точность формирования значений xij невелика (обычно 10-12 двоичных разрядов). Требования к быстродействию вычисления очень высоки. Для обеспечения приемлемого времени решения формирователь должен выполнять 20-50 миллионов операций умножения в секунду, В настоящее время такое быстродействие может быть обеспечено лишь при использовании логарифмических кодов.

Для формирования логарифмического кода необходимо на вход 1 подать знак числа х, на входы 2 - его значащие разряды

(удобно представлять последние в прямом двоичном коде).

Вычисление логарифмического кода осуществляется по формуле .у k + 1092x1 + (1од2Х1)хз),

где xi - m старших разрядов числа

хз - n - m младших разрядов числа х.

Производная (logzx)) вычисляется по приближенной формуле

( 092 X )

1

15

где Х2 - р старших разрядов числа х.

Значение logaxi определяется в блоке

5, значение -

хз

определяется в блоке 6.

Х2 Л2

В сумматоре 7 формируется значение у.

Формирование у удобно осуществлять в дополнительном коде.

Если х 0, то блок 3 формирует k 0, с выходов блоков 5 и 6 считываются нули. С учетом опускаемого знака имеют у ...О 00.,.00, т. е, у принимает минимально возможное значение. Признак z при этом равен 1.

Формула изобретения Формирователь логарифмического кода, содержащий первый и второй блоки памяти и сумматор, отличающийся тем, чго, с целью позьгшения быстродействия и упрощения, о1- содержит элемент ИЛИ-НЕ, блока поиска старшей единицы и сдвигатель, причем информационный вход устройства подключен к входам элемента ИЛИ-НЕ и блока поиска стаошей единицы и информационному входу сдвигателя, управляющий вход которого соединен с выходом

блока поиска старшей единицы и входом первого слагаемого сумматора, входы второго и третьего слагаемых которого соединены с выходами соответственно первого и второго блоков памяти, адресные входы которых подключены к выходу сдвигателя, выходы элемента ИЛИ-НЕ и сумматора соединены соответственно с первым и вторым информационными выходами устройства, выход знака устройства соединён с

входом знака устройства.

SM7

.t.K.cc,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Устройство для вычисления функции @ | 1985 |

|

SU1305671A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Преобразователь логарифмического кода в двоичный код | 1990 |

|

SU1716506A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для возведения в степень | 1984 |

|

SU1171788A1 |

| Устройство для вычисления натурального логарифма | 1987 |

|

SU1559345A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является упрощение формирователя и повышение его быстродействия Для этого в формирователь, содержащий два блока памяти и сумматор, введены блок поиска старшей единицы, сдвигатель, элемент ИЛИ-НЕ. В результате существенно повышается быстродействие формирователя и сокращается расход оборудования 2 ил

15

/i. ii U и J i,

ti I

jiAi v,i

Id 12

| Устройство для вычисления логарифмов чисел | 1978 |

|

SU746540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования | 1986 |

|

SU1388857A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-23—Публикация

1989-07-10—Подача