4

4

00 00 ел

Од

ш

1

Изобретение относится к вычислительной технике и предназначено лля использования я цифровых вычислительных машинах паяличного азняченияо

Целью изобретения является упрощение и пояьппение быстродействия устройства,

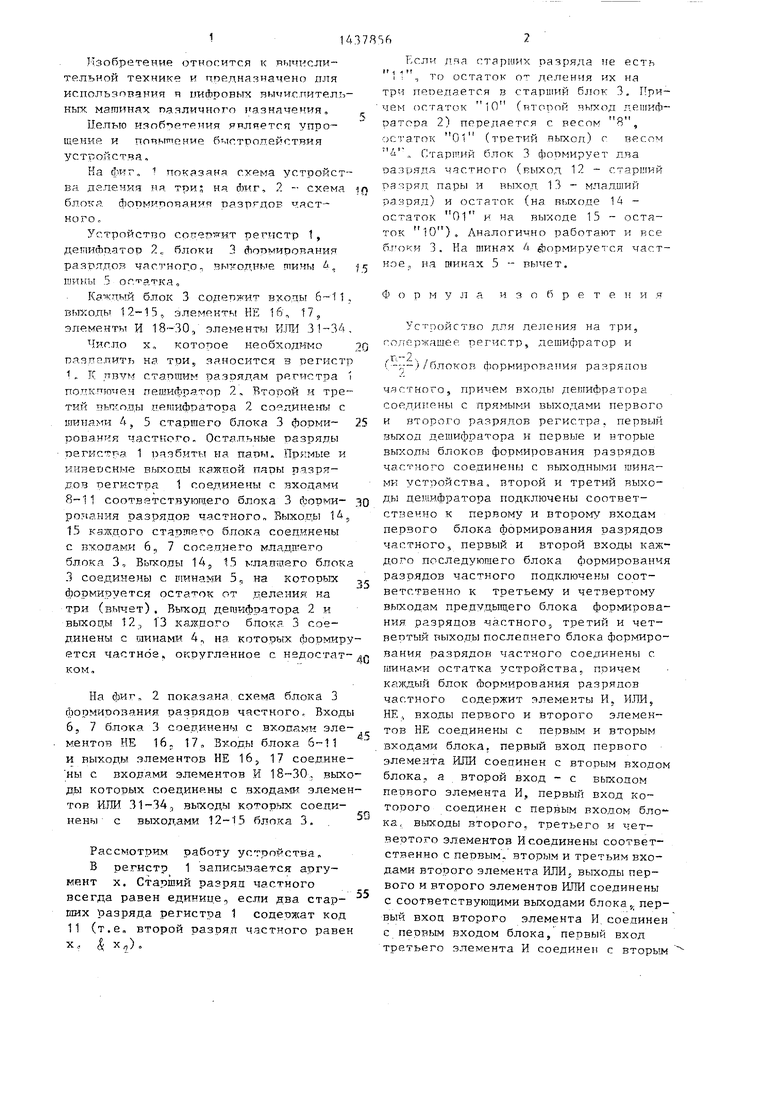

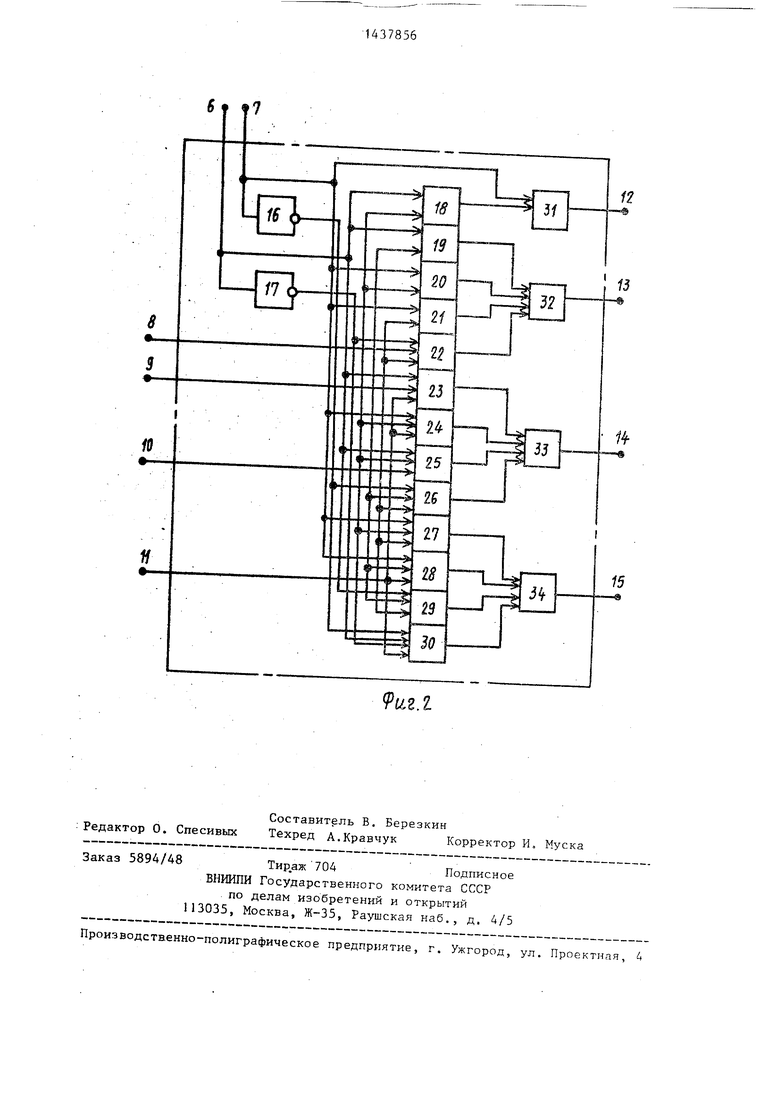

На фиг„ 1 показана схема устройст-- БгЧ деления на три; на Лиг, 2 - схема блока формирочани разргдов частного .

Устройство cptrepwHT регистр 1, дешийо.атор 2„ блоки 3 формирования разрядов частного. вы1- одные тины -, 15 шины 5 остатка,

Кахггъ й блок 3 содержит входы 6-11 , вькоды 12-15, элементы Н Ё 16, 17, элементы И 18-30, элементы ШШ 31-34,

Чиг.ло х„ которое необходимо 20 разпялить на три, заносится з регистр . К ДВУМ стапшим разрядам регистра 1 додклю чен пеп1ифратор 2, Второй и третий вьпсоды дешифратора 2 соединены с шинами 4, 5 старшего блока 3 форми- 25 рования частного. Остальные разряды регистра 1 разбиты на пары. Прямые и инвепсные выходы каждой пяры разрядов регистра 1 соединены с входами 8-11 соответствующего блока 3 форми- зо рояания разрядов частного г, Выходы 15 каждого старшего блока соединены с входами 6, 7 соседнего младшего блока 3, Выходы 14, 15 клядшего блока 3 соединены с шинами 5, на которых , формируется остаток от деления на три (вычет). Выход дешифратора 2 и выходы 12-, 13 каждого блока 3 соединены с шинами 4, на которых формируется частное, округланное с недостат-д ком.

143785ft

.- дяа старших разряда не есть 11, то остаток от деления их на три пепедается в cTapmtift блок 3. Причем остаток 10 (нторой выход дешифратора 2) передается с весом 8 , остаток 01 (третий выход) г весом , Старший блок 3 фопмирует два разряда частного (выход 12 - старший рз,чря,д пары и выход, 13 - младширг разряд) и остаток (на в 1ходе 14 - остаток 01 и на выходе 15 - остаток 10), Аналогично работают и все бт оки 3. На шинах 4 йзормирует-ся частное, на шинах 5 -- вычет.

Формула и 3 о б р е т е Ti и ,я

Устройство для деления на три, го/гержащее регистр, дешифратор и

()/блоков формирования разряпов

частного, причем входы деигифратора соединены с прямыми выходами первого и второго разрядов регистра, первый выход дешифратора и первые и вторые выходы блоков формирования разрядов частного соединены с выходными шинами устройства, второй и третий выходы дешифратора подключены соответственно к первому и второму входам первого блока формирования разрядов частного, первый и второй входы каждого последующего блока формирования разрядов частного подключены соответственно к TpeTbeNry и четвертому выходам предудьпцего блока формирования разрядов частного, третий и четвертый выходь последнего блока формирования разрядов частного соединены с шинаг« и остатка устройства, причем каждый блок Формирования разрядов частного содержит элементы И. ИЛИ, НЕ, входы первого и второго элементов НЕ соединены с первым и вторым входами блока, первый вход первого элемента ШШ соединен с вторым входом блока, а второй вход - с выходом первого элемента И, первый вход которого соединен с первым входом блока, выходы второго, третьего и чет- ве:отого элементов И соединены соответственно с первым, вторы,м и третьим входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с соответствующими выходами блока , дер- вый вхоц второго элемента И.соединен с первым входом блока, первый вход третьего элемента И соединен с вторы-м

На фиг, 2 доказана, схема блока 3 формирования разрядов частного. Входы 6, 7 блока 3 соединены с входами элементов НЕ 16; 17, Входы блока 6-11 и выходы элементов НЕ 16, 17 соедине- ны с входами элементов И 18-30,, выходы которых соединены с входами элементов ИПИ 31 -34,, выходы которых соединены с выходами 12-15 блока 3.

Рассмотрим работу устройства, В регистр 1 записывается аргумент X, Старший разряц частного всегда равен единице, если рва старших Разряда регистра 1 содержат код 11 (т,е„ второй разряд частного равен

X,, ( X,) ,

5

0

5

Формула и 3 о б р е т е Ti и ,я

Устройство для деления на три, го/гержащее регистр, дешифратор и

()/блоков формирования разряпов

частного, причем входы деигифратора соединены с прямыми выходами первого и второго разрядов регистра, первый выход дешифратора и первые и вторые выходы блоков формирования разрядов частного соединены с выходными шинами устройства, второй и третий выходы дешифратора подключены соответственно к первому и второму входам первого блока формирования разрядов частного, первый и второй входы каждого последующего блока формирования разрядов частного подключены соответственно к TpeTbeNry и четвертому выходам предудьпцего блока формирования разрядов частного, третий и четвертый выходь последнего блока формирования разрядов частного соединены с шинаг« и остатка устройства, причем каждый блок Формирования разрядов частного содержит элементы И. ИЛИ, НЕ, входы первого и второго элементов НЕ соединены с первым и вторым входами блока, первый вход первого элемента ШШ соединен с вторым входом блока, а второй вход - с выходом первого элемента И, первый вход которого соединен с первым входом блока, выходы второго, третьего и чет- ве:отого элементов И соединены соответственно с первым, вторы,м и третьим входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с соответствующими выходами блока , дер- вый вхоц второго элемента И.соединен с первым входом блока, первый вход третьего элемента И соединен с вторы-м

входом блока, первый вход четвертого элемента И соединен с выходом первого эле 5ента НЕ, а второй вход - с третьим входом блока, выходы пятого, шестого и седьмого элементов И соединены соответственно с пе.рвым,, вторым и третьим входами третьего элемента 11ПИ, первь й вход пятого элемента И соединен с первым входом блока, первый вход шестого,элемента И соединен с вторым входом блока, первый и второй входы седьмого элемента И соединены с выходами соответствующих элементов НЕ, выходы восьмо- го. девятого и десятого элементов И соединены соответственно с первым, вторым и третьим входами четвертого элемента ИЛИ, первый вход восьмого элемента И соединен с вторым входом блока, первый вход девятого элемента И соединен с первым входом блока, первый и второй входы десятого элемента И соединень с выходами соответствующих элементов НЕ, выходы третьего и четвертого элементов И соединены с соответствующими выходами блока, отличающееся тем, что, с пелью упрощения и повы- .шения быстродействия, входы с третьего по шестой i-ro блока формирования разрядов частного (,.,.,

5в

п-2,

-г) соеднпены с прямыми и инверсными, выходами (2г + 1)-го и (21 + 2) го разрядов регистра, а в каждом бпо ке формирования разрядов частного третий.вход соединен с вторыми входами первого, третьего, шестого третьим входом десятого и первыми входами одиннадцатого и двенадцатого элементов И, четвертый вход блока подключен к вторым входам второго, пятого, восьмого, девятого и третьим входам седьмого элементов Н, пятый вход блока подключен к первому входу тринадцатого, вторым входам одиннадцатого, двенадцатого, третьим входам четвертого, девятого и четвертому входу седьмого элементов И, шестой вход блока пп.дключен к третьим входам пятого, шестого, восьмого и четвертому входу десятого элемен- тов И, второй вход тринадцатого элемента И соединен с вторым входом блока, третьи входы одиннадцатого и двенадцатого элементов И соединены соответственно с первым и вторым входами блока, выходы одиннадцатого двенадцатого и тринадцатого эдементов И соединены с четвертыми входами соответственно третьего, четвертого и второго элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления на три | 1989 |

|

SU1667058A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1174923A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

9lLZ.l

| Устройство для деления двоичных чисел на три | 1982 |

|

SU1062690A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления п-разрядного двоичного кода на три | 1974 |

|

SU506853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1987-03-16—Подача