Изобретение относится к вычислительной технике и может быть использовано в качестве звеньев спецпроцессора, вычисляющего значения функций методом непрерывных дробей Эйлера, или автономно - для определения значения выражения cvi z2 r/(a+xy).

Цель изобретения - расширение функциональных возможностей за счет вычисления элементов непрерывной дроби Эйлера.

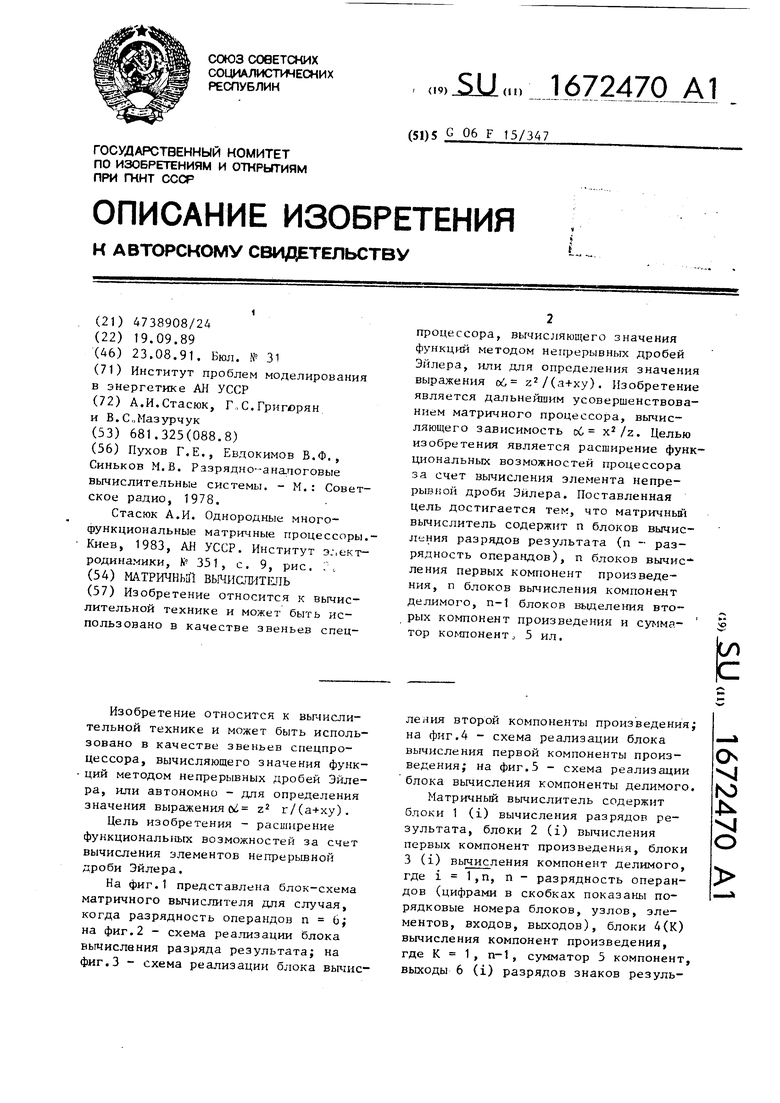

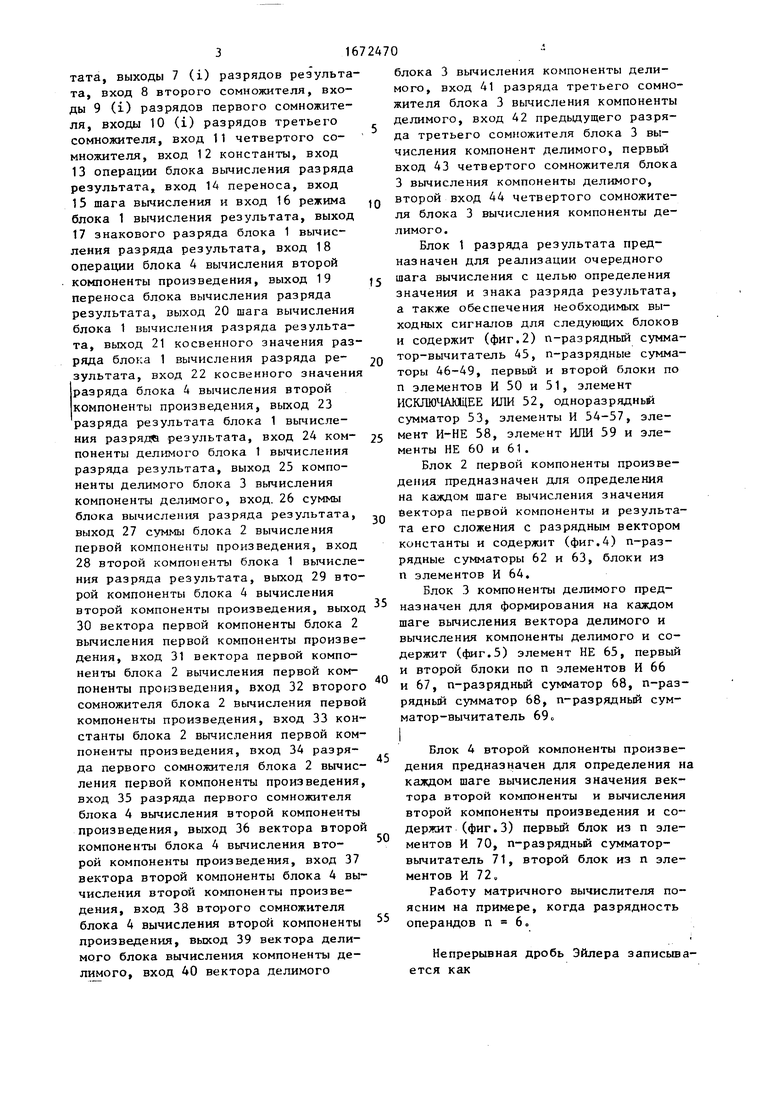

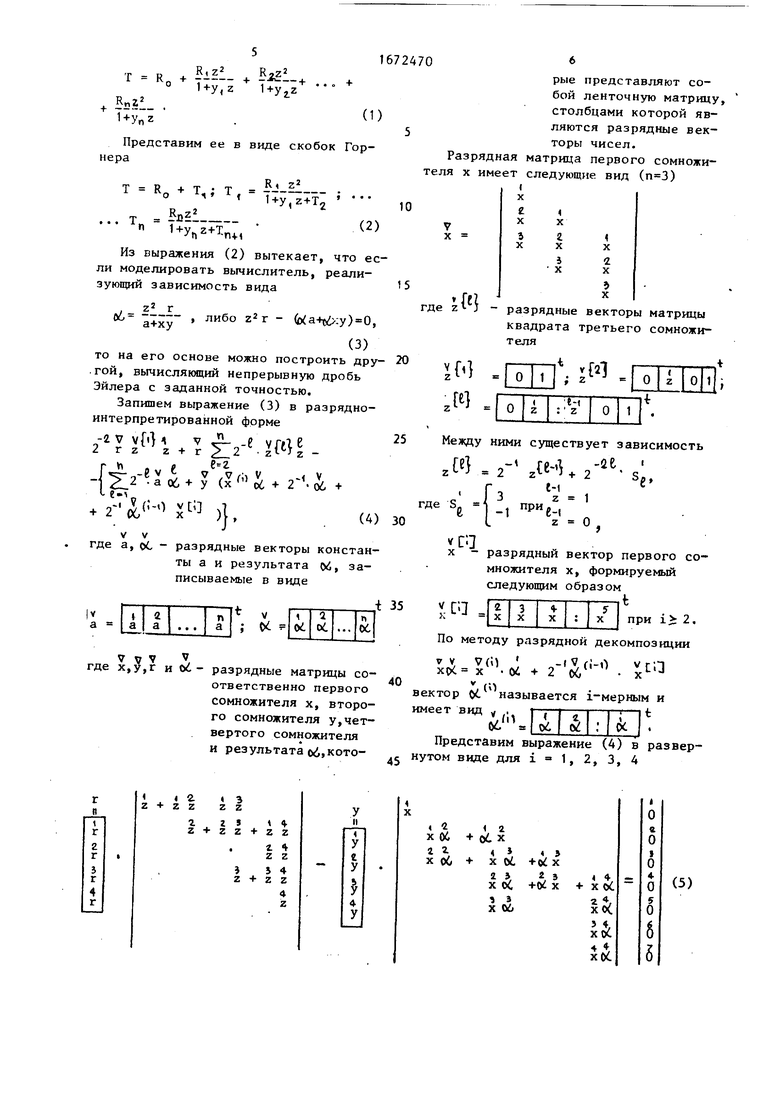

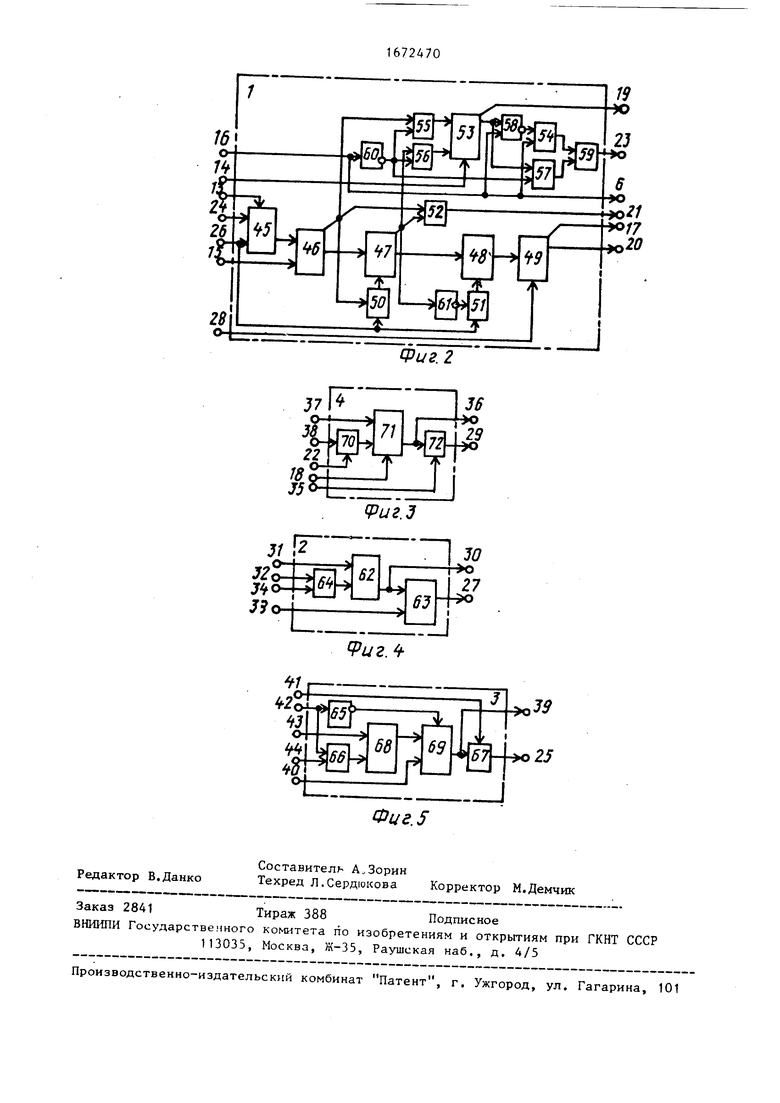

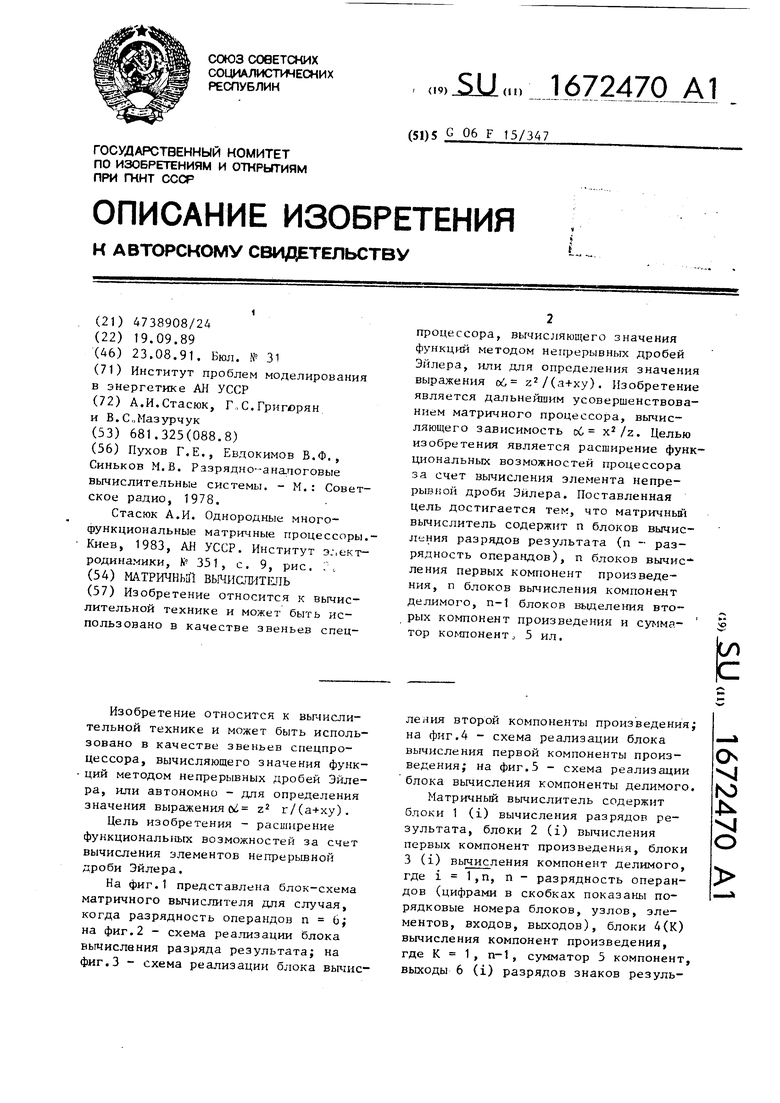

На фиг.1 представлена блок-схема матричного вычислителя для случая, когда разрядность операндов п Ь; на фиг.2 - схема реализации блока вычисления разряда результата; на фиг.З - схема реализации блока вычисления второй компоненты произведения; на фиг.4 - схема реализации блока вычисления первой компоненты произведения; на фиг.5 - схема реализации блока вычисления компоненты делимого.

Матричный вычислитель содержит бпоки 1 (i.) вычисления разрядов результата, блоки 2 (i) вычисления первых компонент произведения, блоки 3 (i) вычисления компонент делимого, где i 1,n, n - разрядность операндов (цифрами в скобках показаны порядковые номера блоков, узлов, элементов, входов, выходов), блоки 4(К) вычисления компонент произведения, где К 1, п-1, сумматор 5 компонент, выходы 6 Ц) разрядов знаков резульО

го

-N

ч|

о

9 (i) разрядов первого сомножите- i, входы 10 (i) разрядов третьего

тата, выходы 7 (i) разрядов результата, вход 8 второго сомножителя, входыля,

сомножителя, вход 11 четвертого сомножителя, вход 12 константы, вход 13 операции блока вычисления разряда результата, вход 14 переноса, вход 15 шага вычисления и вход 16 режима блока 1 вычисления результата, выход 17 знакового разряда блока 1 вычисления разряда результата, вход 18 операции блока 4 вычисления второй компоненты произведения, выход 19 переноса блока вычисления разряда результата, выход 20 шага вычисления блока 1 вычисления разряда результата, выход 21 косвенного значения разряда блока 1 вычисления разряда результата, вход 22 косвенного значения разряда блока 4 вычисления второй компоненты произведения, выход 23 разряда результата блока 1 вычисления разряде результата, вход 24 компоненты делимого блока 1 вычисления разряда результата, выход 25 компоненты делимого блока 3 вычисления компоненты делимого, вход. 26 суммы блока вычисления разряда результата, выход 27 суммы блока 2 вычисления первой компоненты произведения, вход 28 второй компоненты блока 1 вычисления разряда результата, выход 29 второй компоненты блока 4 вычисления второй компоненты произведения, выход 30 вектора первой компоненты блока 2 вычисления первой компоненты произведения, вход 31 вектора первой компоненты блока 2 вычисления первой компоненты произведения, вход 32 второго сомножителя блока 2 вычисления первой компоненты произведения, вход 33 константы блока 2 вычисления первой компоненты произведения, вход 34 разряда первого сомножителя блока 2 вычисления первой компоненты произведения, вход 35 разряда первого сомножителя блока 4 вычисления второй компоненты произведения, выход 36 вектора второй компоненты блока 4 вычисления второй компоненты произведения, вход 37 вектора второй компоненты блока 4 вычисления второй компоненты произведения, вход 38 второго сомножителя блока 4 вычисления второй компоненты произведения, выход 39 вектора делимого блока вычисления компоненты делимого, вход 40 вектора делимого

5

0

5

0

5

0

5

0

5

блока 3 вычисления компоненты делимого, вход 41 разряда третьего сомножителя блока 3 вычисления компоненты делимого, вход 42 предыдущего разряда третьего сомножителя блока 3 вычисления компонент делимого, первый вход 43 четвертого сомножителя блока 3 вычисления компоненты делимого, второй вход 44 четвертого сомножителя блока 3 вычисления компоненты делимого.

Блок 1 разряда результата предназначен для реализации очередного шага вычисления с целью определения значения и знака разряда результата, а также обеспечения необходимых выходных сигналов для следующих блоков и содержит (фиг.2) n-разрядный сумма- тор-вычитатель 45, n-разрядные сумматоры 46-49, первый и второй блоки по п элементов И 50 и 51, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 52, одноразрядный сумматор 53, элементы И 54-57, элемент И-НЕ 58, элемент ИЛИ 59 и элементы НЕ 60 и 61.

Блок 2 первой компоненты произведения предназначен для определения на каждом шаге вычисления значения Вектора первой компоненты и результата его сложения с разрядным вектором константы и содержит (фиг.4) п-раз- рядные сумматоры 62 и 63, блоки из п элементов И 64.

Блок 3 компоненты делимого предназначен для формирования на каждом шаге вычисления вектора делимого и вычисления компоненты делимого и содержит (фиг.5) элемент НЕ 65, первый и второй блоки по п элементов И 66 и 67, n-разрядный сумматор 68, п-раз- рядный сумматор 68, n-разрядный сум- матор-вычитатель 69 „

I

Блок 4 второй компоненты произведения предназначен для определения на каждом шаге вычисления значения вектора второй компоненты и вычисления второй компоненты произведения и содержит (фиг.З) первый блок из п элементов И 70, n-разрядный сумматор- вьгчитатель 71, второй блок из п элементов И 72,

Работу матричного вычислителя поясним на примере, когда разрядность операндов п 6„

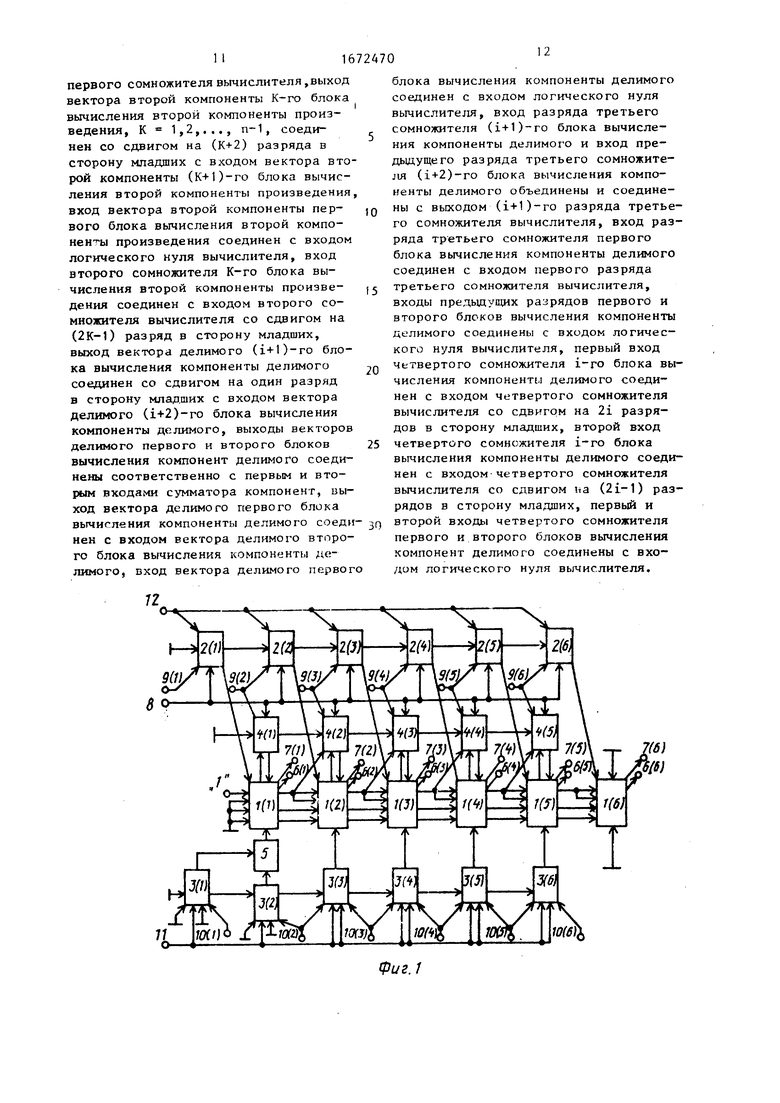

Непрерывная дробь Эйлера записывается как

Rc

R,z2 Raz2 + + л+ .. o +

1+y,z 1+ytz

16724706

рые представляют собой ленточную матрицу, столбцами которой яв716724708

С помощью выражения (4) организу-Первое разрядное уравнение для

определения значения старшего разряда искомого вектора об формируется

ем вычисления в виде рекуррентных процедур каждая из которых является моделью разрядного уравнения..

следующим образом

следующим образом

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для нахождения оптимального вектора решения системы линейных неравенств | 1985 |

|

SU1315996A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве звеньев спецпроцессора, вычисляющего значения функций методом непрерывных дробей Эйлера, или для определения значения выражения α = Z2/(A + XY). Изобретение является дальнейшим усовершенствованием матричного процессора, вычисляющего зависимость α = X2/Z. Целью изобретения является расширение функциональных возможностей процессора за счет вычисления элемента непрерывной дроби Эйлера. Поставленная цель достигается тем, что матричный вычислитель содержит N блоков вычисления разрядов результата (N - разрядность операндов), N блоков вычисления первых компонент произведения, N блоков вычисления компонент делимого, N - 1 блок выделения вторых компонент произведения и сумматор компонент. 5 ил.

У, Q, z

,.|-(2-..2-), i,- i;j;;t0o

, I 1 v - О

у, -у, - 2а + 2 у,),; |0; Jj;0

I f 1 .2

.-. i,-

i

II 1 /- 3

УМ -л6,@о, 2 У, 2 ух; 2.рг- 2 , у . & ; У У| VIV + ( а + 2 ЛУ-:

оС PC, + &г

Q, 2-2 г; дг . г + Г4 i- Q , 4

Каждая посл ду ощая компонента не-известно о вектора определяется как

i

-fi+0

Л У., +QU.Z - (2.а + .О-З,.,; S-.

.

; J(D, о

,-(л

IT -2 У,-., +2-,у.

2( fCIS;. 2(.(г(-м,л;) + 2

QU -2-.

и -(ЬгК (.(+ПТ

У. У; - 2(iU( х + (2 . а + 2-J, ).

Результат вычислений образуется в

знакопох лоче if

, гфичрм i-й компоненте вектора & присваивается знак S ;, о

Матричньп вычислитель элемента непрерывной дроби Эйлера работает следующим образом.

На вход 30 подается значение константы а. На входы 33 (1) - 33 (6) подаются значения разрядов первого сомножителя х, на вход 28 - значение второго сомножителя у, на входы 41(1 41(6) - значения разрядов третьего сомножителя z, на вход 43 - значение четвертого сомножителя г

Следует отметить, что одноразрядный сумматор t9 и логические элемен i

;

-fi+0

.О-З,.,; S-.

Ь -1,

I

.

-(2i-i)l

ты НЕ 46, И 48, 50, 51 и 52, И-НЕ 47 и ИЛИ 53 выполняют логическую функцию & S-, A P,Y S; A(P(, + Жг + + Р i, ) гДе Р;., перенос.

Блоки 2 вычисления первых компонент произведения вычисляют значе- ,

т v нил векторов первых компонент L Д

и результаты их сложения с соответствующим значением разрядного вектора константы .

Блоки 3 вычисления компонент делимого формируют векторы делимого Q, и значения компо нент делимого Qji.

Блоки 4 вычисления вторых компо- не- i произведения вычисляют значения

,-Hf2)

1

i -и

XИ

вторых компонент векторов второй компоненты для чего используется косвенное значение разряда (

После окончания переходного процесса в схеме на ее выходах 18(1) - 18(6) устанавливаются значения соответствующих разрядов результата, а на выходах 12(1) - |2(6) - их соответствующие знаки.

Вычислитель является универсальным в том аспекте, что в зависимости от значений входных переменных он вычисляет результаты альтернативных функций, таких как, например э/(а+у.у); z2 /х2 ; г/(а+х) и т.д

Формула

изо

Р е

е н и я

Матричный вычислитель, го, ержащий сумматор компонент, отличающийся тем, что, с целью расширения функциональных ъи зм м;нос ген : ч счет вычисления элемента непрерывной дроби Эйлера, в него введены п блоко вычисления разрядов результата, где п - разрядность операндов, п блоков вычисления первых компонент произведения, п блоков вычисления компонент делимого, п-1 блоков вычисления вторых компонент произведения, пг -ом вход операции первого блока Б}, исле- ния разряда результата сосдино1- с входом логической егиницы гычп,лше- ля, вход перевеса, вход -цагс вычисления и вход режима первого блока вычисления разряда результата соединены

с входом логического нуля гычислнтеш нупя вычислителя, вхсц второго сомно- ля, выход знакового разряда j-ro бло- и

значения разряда i-ro блокл вычнгле- ния второй кимпоненгы произведения, РЫХОД разряда результата i-ro блока вычисления разряда результата соединен с выходом соответствующего разряда результата вычислителя, вход компоненты делимого первого блока пычг.с- пения разряда результата с динен с выходом сумматора компонс-нг, компоненты делимого гг-го блока вычисления разряда результата, где m - 2,3,0.., п-1, соелннен с выходом компоненты делимого (m+1)-ro блока вычисления компонент / делимого, вход компоненты делимого n-го блока вычисления разряда результата соединен с irco ioM логического нуля вычислите-ля , вход суммы i-го блока вычпелс-ния разряда результата соединен с выходом с/ммы 1-го блока вычисления первой компоненты произведения, вход второй компоненты 1-го б го кг. гзычнс тения рч ряда результата соединен с выходом второй компоненты i-ro блока вычисления второй компоненты произведения, вход второй компоненты n-го блока вычисления разряда ре ультата соединен с входом логического куля вычислителя, выход вектора первой компоненты i-ro блока вычисления пергой компоненты произведения соединен со сдвигом на (i + 1) разряд в сточоиу мллд- ших с входом вектора лерроп компоненты ()-го бпока выччсленпч первой компоненты произведен , вход гек гора первой компоненты первого блока вычисления первой компоненты произведения соединен с входом логического

жителя 1-го блока вычисления первой компоненты произведения соединен с входом второго сомножителя вычислителя со с дьигом на 25 разрядов в сторону младпих, вход константы 1-го блока вычисления первой компоненты иро- и.веден тя соединен с входом константы вычислителя со сдвигом на i разрядов в сторону младших, вход разряда первого сомножителя (i+1)-ro Г ока вычисления первой компоненты произведения соединен с входом разряда первого сомножителя 1-го блока вычисления второй компоненты произведения н с (1+1)м разрядом входа первого сомножителя вычислителя, вход разряда первого сомножителя первого блока вычисления первой компоненты произведения соединен с входом первого разряда

ка вычисления разряда. ,2,, „,n, соединен с входом операции (i-H)-ro блока вычисления агорою компоненты произведения, с входом операции и входом режима (i+1)-ro блока нычис- ления разряда результата и выходом знака соответствующего разряда результата вычислителя, выход перснсча 1-го блока вычисления разряда результата соединен с входом переноса (i+1)-го блока вычисления разряда результата, выход шага вычисление i чо блока вычисления разряд результата соединен с входом шага вычисления (i+1)-го блока вычисления разряда результата, выход косвенного значения разряда 1-го блока вычисления разряда результата соединен с входом косвенного

1672470

HI

0

Ь

5

0

5

значения разряда i-ro блокл вычнгле- ния второй кимпоненгы произведения, РЫХОД разряда результата i-ro блока вычисления разряда результата соединен с выходом соответствующего разряда результата вычислителя, вход компоненты делимого первого блока пычг.с- пения разряда результата с динен с выходом сумматора компонс-нг, компоненты делимого гг-го блока вычисления разряда результата, где m - 2,3,0.., п-1, соелннен с выходом компоненты делимого (m+1)-ro блока вычисления компонент / делимого, вход компоненты делимого n-го блока вычисления разряда результата соединен с irco ioM логического нуля вычислите-ля , вход суммы i-го блока вычпелс-ния разряда результата соединен с выходом с/ммы 1-го блока вычисления первой компоненты произведения, вход второй компоненты 1-го б го кг. гзычнс тения рч ряда результата соединен с выходом второй компоненты i-ro блока вычисления второй компоненты произведения, вход второй компоненты n-го блока вычисления разряда ре ультата соединен с входом логического куля вычислителя, выход вектора первой компоненты i-ro блока вычисления пергой компоненты произведения соединен со сдвигом на (i + 1) разряд в сточоиу мллд- ших с входом вектора лерроп компоненты ()-го бпока выччсленпч первой компоненты произведен , вход гек гора первой компоненты первого блока вычисления первой компоненты произведения соединен с входом логического

нупя вычислителя, вхсц второго сомно-

жителя 1-го блока вычисления первой компоненты произведения соединен с входом второго сомножителя вычислителя со с дьигом на 25 разрядов в сторону младпих, вход константы 1-го блока вычисления первой компоненты иро- и.веден тя соединен с входом константы вычислителя со сдвигом на i разрядов в сторону младших, вход разряда первого сомножителя (i+1)-ro Г ока вычисления первой компоненты произведения соединен с входом разряда первого сомножителя 1-го блока вычисления второй компоненты произведения н с (1+1)м разрядом входа первого сомножителя вычислителя, вход разряда первого сомножителя первого блока вычисления первой компоненты произведения соединен с входом первого разряда

первого сомножителя вычислителя,выход вектора второй компоненты К-го блока вычисления второй компоненты произведения, К 1,2,..., п-1, соединен со сдвигом на (К+2) разряда в сторону младших с входом вектора второй компоненты (К+1)-го блока вычисления второй компоненты произведения вход вектора второй компоненты первого блока вычисления второй компо- произведения соединен с входом логического нуля вычислителя, вход второго сомножителя К-го блока вычисления второй компоненты произведения соединен с входом второго сомножителя вычислителя со сдвигом на (2К-1) разряд в сторону младших, выход вектора делимого (i+l)-ro блока вычисления компоненты делимого соединен со сдвигом на один разряд в сторону младших с входом вектора делимого (i+2)-ro блока вычисления компоненты делимого, выходы векторов делимого первого н второго блоков вычисления компонент делимого соединены соответственно с первым и вторым входами сумматора компонент, выход вектора делимого первого блока вычисления компоненты делимого соеди нен с входом вектора делимого второго блока вычисления компоненты делимого, вход вектора делимого первог

Q

0

5

блока вычисления компоненты делимого соединен с входом логического нуля вычислителя, вход разряда третьего сомножителя (i+1)-ro блока вычисления компоненты делимого и вход предыдущего разряда третьего сомножителя ()-ro блока вычисления компоненты делимого объединены и соединены с выходом (i+1)ro разряда третьего сомножителя вычислителя, вход разряда третьего сомножителя первого блока вычисления компоненты делимого соединен с входом первого разряда третьего сомножителя вычислителя, входы предыдущих разрядов первого и второго блоков вычисления компоненты делимого соединены с входом логического нуля вычислителя, первый вход четвертого сомножителя 1-го блока вычисления компоненты делимого соединен с входом четвертого сомножителя вычислителя со сдвигом на 21 разрядов в сторону младших, второй вход четвертого сомножителя 1-го блока вычисления компоненты делимого соединен с входом четвертого сомножителя вычислителя со сдвигом на (21-1) разрядов в сторону младших, первый и второй входы четвертого сомножителя первого и второго блоков вычисления компонент делимого соединены с входом логического нуля вычислителя.

Фиг.1

| Пухов Г.Е., Евдокимов В.Ф., Синьков М.В | |||

| Разрядно -анапоговые вычислитепьные системы | |||

| - М | |||

| : Советское радио, 1978 | |||

| Стасюк А.И | |||

| Однородные много- Функциональные матричные процессоры | |||

| - Киев, 1983, АН УССР | |||

| Институт э.,ькт- родинамики, К 351, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-08-23—Публикация

1989-09-19—Подача