Изобретение относится к автоматике и вычислительной технике.

Цель изобретения - уменьшение статического потребления энергии.

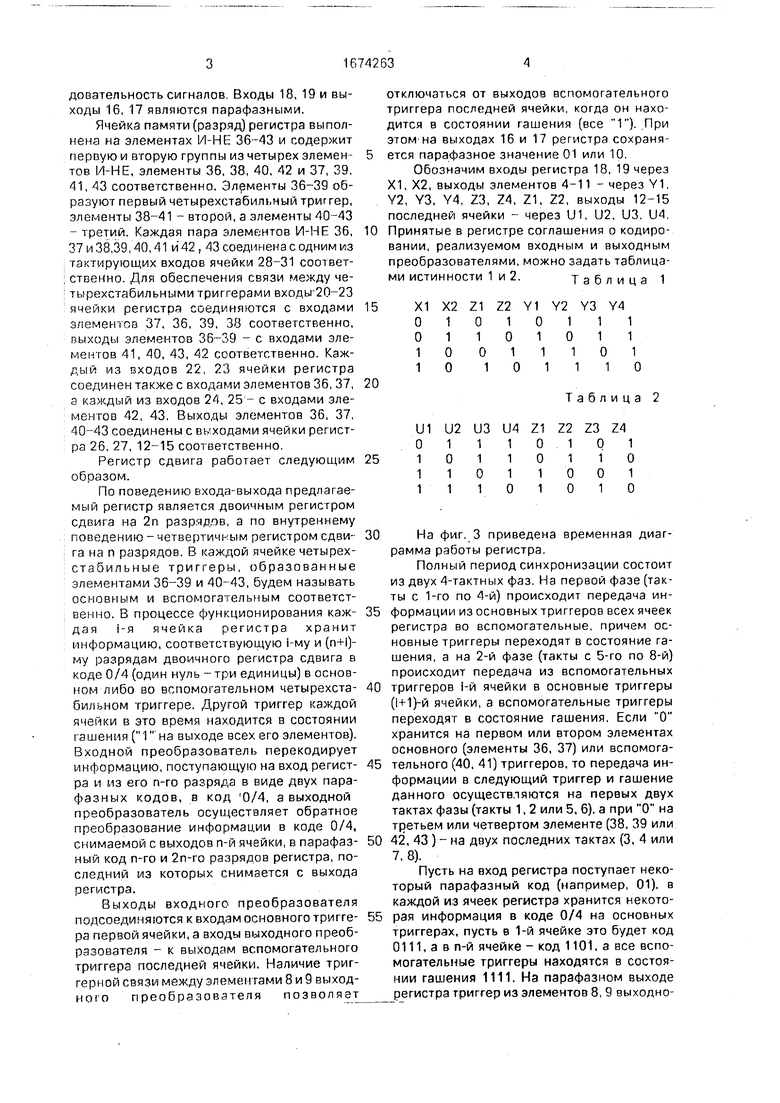

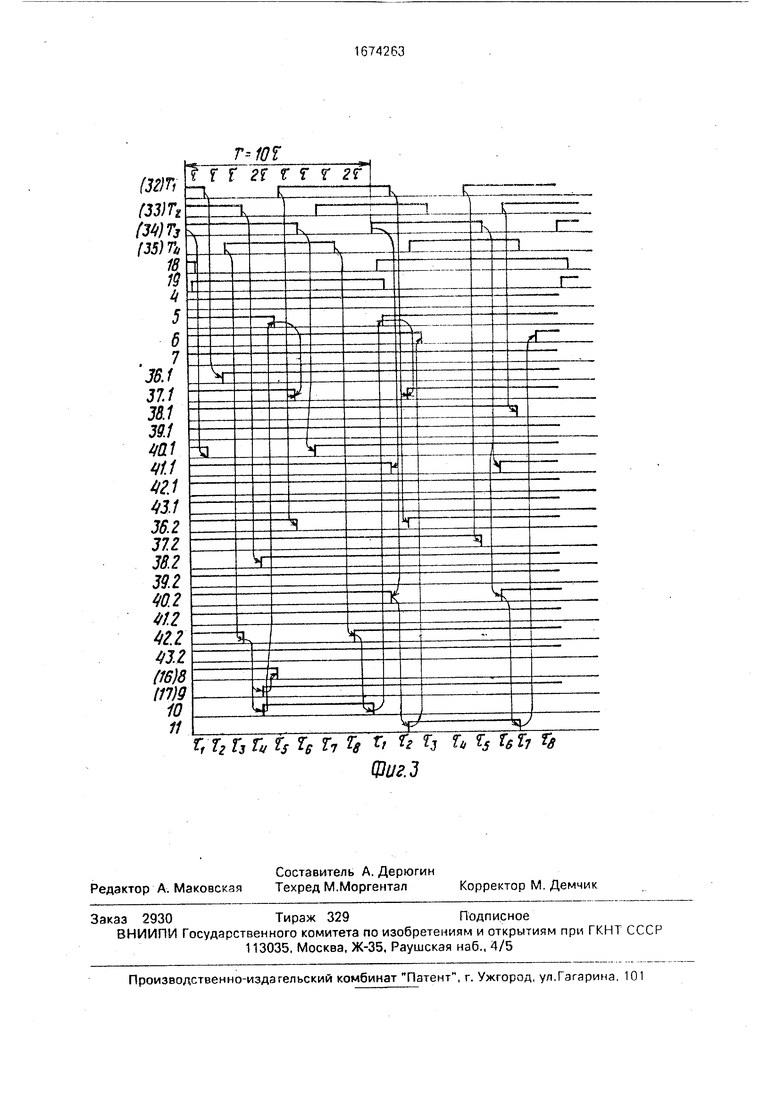

На фиг. 1 приведена схема четырехтактного поспедовательного регистра сдвига; на фиг. 2 - схема одного разряда регистра (ячейки памяти); на фиг. 3 - временная диаграмма работы регистра.

Регистр состоит из ячеек памяти (разрядов) 1, входного 2 и выходного 3 преобразователей.

Входной 2 и выходной 3 преобразователи содержат элементы И НЕ 4-7 и 8-11 соответственно, причем выходы 12-15 последней ячейки 1 соединены соответственно с входами элементов 9и11,8и11,9 и 10 и 8 и 10 преобразователя 3, выходы элементов 8 и 9 являются соответственно прямым 16 и инверсным 17 выходами регистра и соединены с входами элементов 9 и 8 соответственно, выходы элементов 10 и 11

преобразователя 3 соединены соответственно с входами элементов 5, 7 и 4, 6 преобразователя 2, прямой 18 и инверсный 19 входы регистра соединены соответственно с входами элементов 6, 7 и 4, 5 преобразователя 2, выходы элементов 4-7 преобразователя 2 соединены с соответствующими входами 20-23 первой ячейки регистра 1.

Каждая из ячеек памяти регистра имеет сходы 20-23 и 24, 25 и выходы 12-15, 26, 27. Входы 20-23 каждой из ячеек регистра, кроме первой, соединены с выходами 12-15 предшествующей ячейки, входы 24 и 25 каждой из ячеек регистров соединены с выходами 26, 27 последующей ячейки, причем входы 24, 25 последней ячейки регистра соединены с выходами 26, 27 первой ячейки Каждая из ячеек регистра имеет также входы 28-31, соединенные с входами 32-35 ре- гистра, на которые подается четырехтактная синхронизирующая послесл С

О VJ

4 ГО

о

(л)

довательность сигналов. Входы 18, 19 и выходы 16, 17 являются парафазными,

Ячейка памяти (разряд) регистра выполнена на элементах 1/1-НЕ 36-43 и содержит первую и вторую группы из четырех элементов И-НЕ, элементы 36, 38, 40, 42 и 37, 39. 41, 43 соответственно. Элементы 36-39 образуют первый четырехстабильчый триггер, элементы 38-41 - второй, а элементы 40-43 третий. Каждая пара элементов И-НЕ 36, 37 и 38,39,40,41 и 42 , 43 соединена с одним из тактирующих входов ячейки 28-31 соответственно. Для обеспечения связи между че- тырехстабильными триггерами вход.ы20-23 ячейки регистра соединяются с входами элементов 37, 36, 39, 38 соответственно, пыходы элементов 36-39 - с входами элементов 41, 40, 43, 42 соответственно. Каждый из входов 22, 23 ячейки регистра соединен также с входами элементов 36, 37, п каждый из входов 24, 25 - с входами элементов 42, 43. Выходы элементов 36, 37, 40-43 соединены с выходами ячейки регистра 26, 27, 12-15 соответственно.

Регистр сдвига работает следующим образом.

По поведению входа-выхода предлагаемый регистр является двоичным регистром сдвига на 2п разрядов, а по внутреннему поседению - четвертичным регистром сдвига на п разрядов. В каждой ячейке четырех- с т обильные триггеры, образованные элементами 36-39 и 40-43, будем называть основным и вспомогательным соответственно. В процессе функционирования каждая 1-я ячейка регистра хранит информацию, соответствующую i-му и (п-И)- му разрядам двоичного регистра сдвига в коде 0/4 (один нуль - три единицы) в основном либо во вспомогательном четырехста- бильном триггере. Другой триггер каждой ячейки в это время находится в состоянии гашения (1 на выходе всех его элементов). Входной преобразователь перекодирует информацию, поступающую на вход регистра и из его п-го разряда в виде двух пара- фазных кодов, в код 0/4, а выходной преобразователь осуществляет обратное преобразование информации в коде 0/4, снимаемой с выходов n-й ячейки, в парафаз- ный код n-го и 2п-го разрядов регистра, последний из которых снимается с выхода регистра.

Выходы входного преобразователя подсоединяются к входам основного триггера первой ячейки, а входы выходного преобразователя - к выходам вспомогательного триггера последней ячейки. Наличие триг- герной связи между элементами 8 и 9 выход- ного преобразователя позволяет

отключаться от выходов вспомогательного триггера последней ячейки, когда он находится в состоянии гашения (все 1). При этом на выходах 16 и 17 регистра сохраняется парафазное значение 01 или 10.

Обозначим входы регистра 18, 19 через XI, Х2, выходы элементов 4-11 - через Y1. Y2, Y3, Y4, Z3, Z4, Z1, Z2, выходы 12-15 последней ячейки - через U1, U2, U3, U4.

Принятые в регистре соглашения о кодировании, реализуемом входным и выходным преобразователями, можно задать таблицами истинности 1 и 2.Таблица 1

15

Х1 Х2 Z1 Z2 Y1 Y2 Y3 Y4

0

О О 1 1

101

11О

О01 О 1 О

0111 1011 1101 1110

Таблица 2

U1 U2 U3 U4 Z1 Z2 Z3 Z4

01110101

10110110

11011001

11101010

На фиг. 3 приведена временная диаграмма работы регистра.

Полный период синхронизации состоит из двух 4-тактных фаз. На первой фазе (такты с 1-го по 4-й) происходит передача информации из основных триггеров всех ячеек регистра во вспомогательные, причем основные триггеры переходят в состояние гашения, а на 2-й фазе (такты с 5-го по 8-й) происходит передача из вспомогательных

триггеров 1-й ячейки в основные триггеры (1Н)-й ячейки, а вспомогательные триггеры переходят в состояние гашения. Если О хранится на первом или втором элементах основного (элементы 36, 37) или вспомогательного (40, 41) триггеров, то передача информации в следующий триггер и гашение данного осуществляются на первых двух тактах фазы (такты 1, 2 или 5, 6), а при О на третьем или четвертом элементе (38, 39 или

42. 43 ) - на двух последних тактах (3, 4 или 7,8).

Пусть на вход регистра поступает некоторый парафазный код (например, 01), в каждой из ячеек регистра хранится некоторая информация в коде 0/4 на основных триггерах, пусть в 1-й ячейке это будет код 0111, а в n-й ячейке - код 1101. а все вспомогательные триггеры находятся в состоянии гашения 1111. На пзрафазном выходе регистра триггер из элементов 8, 9 выходного преобразователя хранит некоторый код (например. 10). На чходе входного преобра зователя, соединенного с выходом пыходно- го преобразователя, - код 00 ч, следовательно, выход входного преобртло вателя находится в состоянии гашения 1111. На 1-й фазе синхронизации (такты 1 - 4) происходят передача информации из основного во вспомогательный триггеры и гашение основных триггеров, причем д;;я первой ячейки при таком коде это происхо дит на первых двух, а для п-й - на последних двух тактах. Теперь уже во вспомогательном триггере 1-й ячейки хранится код 0111, а во вспомогательном триггере п-й - 1101. Основные триггеры находятся в состоянии гашения 1111. На выходе элементов Я-11 выходного преобразователя появляется код 0110,а на выходах элементен А 7 входного преобразователя - код 1011. На второй фа- зе синхронизации (такты 5-8) происходят передача информации из вспомогательных триггеров в основные триггеры следующих ячеек и гашение вспомогательных триггеров, в основной триггер 1-й ячейки записи- вается код 1011 с выходя сходного преобразователя, в основной триггер 2-й ячейки - код 011 с выходов вспомогательного триггера 1-й ячейки. На парафином выходе регистра фиксируется код 01 на выходах элементов 10, 11 - код 00, а выходной преобразователь будет в состоянии гашения - 1111.

Длительность всех тактов, кроме 1-го и 8-го, равна задержке элемента t. Длитель- ность 4-го и 8-го тактов равна удвоенной задержке элемента 2t, чтобы к началу иго- рой фазы работы входной преобразователь успел перейти из состояния гашения в рабочее состояние, а к началу первой фазы вход- ной преобразователь успевал отсечьс:Г от входа регистра до начала изменения слод- ных сигналов регистра. Таким образом, длительность периода работы регистра Т --- 10t.

За 1 цикл синхронизации (6 тактов - Юг.) регистр производит сдвиг информации на один разряд, а за 20 циклов парафазный код, поданный на вход регистра, достигает парафазного выхода регистра.

Для корректной работы необходимо, чтобы все переходные процессы п элементах регистра завершались в течение одного такта синхронизации, а входные сигналы должны изменяться нг первом такте работы регистра, когда входной преобразователь отсечен от входив.

В прототипе данною регистра ячейка из четырех элементов И-НЕ хранит един бит информации, причем в течение трех тактов каждой фазы в коде 0/4. а о течение 1-го

ы га (при передаче инфпрмнцин мо-кду чг ыжным и 4rnop riraic (и т ри, геи.чми / нуля из 4. В предло1 1 f HHOM регистре счг ft к а p i /n 2 бита. , ; распре/ лгмп е чу.тгй 1 ич 8 п течение м:ох тлктсп и 2 и- 5 п одного гакта.

Таким образом, предложенный регистр потреб/пет ,Г(тии ; ди i р п м т-гге чем

ИЧПеСТ ИМИ.

Формула п л о б р е i е и и л Последовательны : .ip сдпига, с:о- дер кащии п к.тждом разрр/т: первую п сто рую группы из чегыр jnoMemoH H-HE, причем выходь1 первогс . второго, третьего и че1вергого элементов И НЕ каждой группы ( разряда соединены с первыми вхо- /i м i вюрпю, третьего, ЧСГВОРГОТО зтемрн- тов И-1Ч: данной группь; данного разряда и iiij)ioio элемента И-НГ данной группы по- гледующ го рлз чд- 1 соответственно и с чюрыми входг5ми чет верти г элемента И- НЕ длиной группы продыдущсто рачряда, парного, второго и трогьего ЭЛ.-МРНТОР И- it данной группы данного разряда ссотсетст- иен.чо. третьи входы . второго, третьего и четвертого элементов И ME каж- дс. группы каждою пьзрчдч являются соот- петсшенно первым, вторым, ifinmiw и четвертым тактоьыми входами регистра,

0т л и ч а ю щ и и с ч тем. что, с целью у мен i.ii спи я era гичес кого потребления энергии, в него поедет, входной и выход- нон преобразователи, каждый m которых содержит первый, второй, г речи и четаер- тыи тлемен.ы l 1-НГ, причем третьего и четвертого элементов первой групг.ы и третьего и четвертою элементов И-ПЕ второй группы соединены соответственно с входами второго и ет-цертого. второго и третьего первого и четвертого и первого и третьего элеменгоч И-МЬ выход- ноги преобразователя, гзыход первого элемента И-НЕ выходного ппеяиразовагеля соединен г, входом второго элемента И-НЕ данного преобразователя и является прямым выходом регистра, выход второго элемента И-НЕ выходного преобразователя соединен с входом первого элемента И-НЕ данного преобразователя и является инверсным выходом регистра, выходы третьего и четвертого ола чзнтов И-НЕ выходного преобразователя соединены соответственно с первыми входами второго и четвертого и пероого и третьего элементов И-НЕ входно1о преобразователя, выходы первого, вгоро- iO, третьего и четвертого элементов И-НЕ каждой группы каждого разряда соединены с четвертыми входами четвертого элемента другой группы предыдущего разряда, первого, второго и третьего элементов другой группы данного разряда соответственно, с пятыми входами первого, второго, третьего и четвертого элементов другой группы данного разряда соответственно, с шестыми входами второго, третьего, четвертого элементов другой группы данного разряда и перэого элемента другой группы последующего разряда соответственно и с седьмыми входами третьего, четвертого элементов другой группы данного разряда и первого, второго элементов другой группы последующего разряда регистра соответственно, причем выход первого элемента каждой группы первого разряда соединен с вторым входом четвертого элемента данной группы последнего разряда и с шестым входом четвертого элемента другой группы последнего разряда, вторые входы первого и второго

элементов И-НЕ и третьего и четвертого элементов И-НЕ входного преобразователя являются соответственно инверсным и прямым информационными входами регистра, выходы первого и второго элементов И-НЕ входного преобразователя соединены соответственно с первыми входами первых элементов И-НЕ второй и первой групп первого разряда регистра, выход третьего

элемента И-НЕ входного преобразователя - с первым входом второго элемента И-НЕ второй группы и с шестыми входами первых элементов И-НЕ первой и второй групп первого разряда регистра, а выход четвертого

элемента И-НЕ входного преобразователя - с первым входом второго элемента И-НЕ первой группы и с седьмыми входами первых элементов И-НЕ первой и второй групп первого разряда регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1988 |

|

SU1624531A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Устройство для сдвига последовательных чисел в избыточном коде | 1986 |

|

SU1348823A1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Преобразователь параллельного кода в последовательный | 1977 |

|

SU780002A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Оптоэлектронный модуль | 1981 |

|

SU957437A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения состоит в уменьшении статического потребления энергии. Регистр состоит из ячеек памяти (разрядов), входного и выходного преобразователей. Для корректной работы необходимо, чтобы все переходные процессы в элементах регистра завершались в течение одного такта синхронизации, а входные сигналы должны изменяться в первом такте работы регистра, когда входной преобразователь отсечен от входов. 3 ил.

6 28

о 29

-о 24

W

Д-оО

-о 14

--025

30

Фиг.2

о 31

5 f ft Г Ts Те Г7 тв г Ъ Ъ h s Ъ Ъ Ъ

ФигЗ

| Букреев И.Н | |||

| и др Микропроцессорные схемы цифровых устройств - М/ Сов радио, 1975, с.223-227 | |||

| Реверсивный сдвигающий регистр | 1977 |

|

SU734809A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-08-30—Публикация

1988-10-10—Подача