В рабочем.режиме считывания второй мультиплексор 13 пропускает на информационные входы блока 4 управляемых инверторов сигналы информационных разрядов считанного из накопителя 1 слова. При этом расшифровка кода синдрома дeuJифpaтoром 12 разрешена, и поэтому блоки 4, 5, 12 обеспечивают исправление возможных однократных ошибок в счмта ;ных из накопителя словах данных.

Помимо основного режима работы, устройство может работать во вспомогательных режимах, обеспечивающих выявление устройств, имеющих скрытые дефекты. Вспомогательные режимы работы, используемые па этапе,тестирования ОЗУ, включ.эют процедуры проверки работоспособности ЭП хранения информационных и контрольных разрядов накопителя 1, а также совокупности схем коррекции ошибок.

Е режиме проверки ЭП хранения информационных разрядов на входах 9 и 10 поддержива1ртся сигналы логического О. Поэтому G режиме считывания на выходы мультиплексора 2 сигналы riocTynaiOT с выходов информационных разрядов накопителя 1. и, поскольку коррекция ошибок не про вводится, эти же сигналы присутствуют и нз шинах информационных выходов 11 устройстса.

Другим вспомогательным режимом работы г;редложенного устройства является режим проверки ЭП хранения контрольных разрядов В отличие от устройства-прототипа, информация в ЭП контрольных разрядов накопителя 1 записывается непосредстпен ю с внешних выходов ОЗУ (в устройстве-прототипе запись г формации и ЭП контрольных разрядов всегда осущест(зпялась с выходов формирователя контрольных разрядов). Это обеспечивается установкой на входе 9 сигнала уровня логической 1 и пропуском через первый мультмплексор 13 сигналов со входов 7 устройства. Если затем устройство переводится в режим считывания, то при отсутствии коррекции ошибок (сигналов логического О на входе 10) через второй мультиплексор 2 на информационные входы блока 4 управляемых инверторов поступают 4-разрядный код контрольных разрядов слова и 4-разрядный код синдрома. Так как сигнал на входе 10 переводит все выходные сигналы дешифратора 12 в состояние О, то блок 4 уп,1авляемых инверторов пропускает на вых:.ды устройства 11 сигналы с выходов мультиплексора 2 без изменения. Т.е. при такой последовательности циклов работы ОЗУ производится прямая проверка работоспособности ЭП контрольных разрядов

накопителя 1, что делает их проверку аналогичной проверке ЭП информационных разрядов. Следовательно, не требуется изменения программных средств внешнего

устройства контроля.

Вместе с тем прямое занесение информации со входов ОЗУ в ЭП контрольных разрядов позволяет исключить режим (а следовательно, и технические средства)

принудительной генерации ошибок для проверки работоспособности схем коррекции ошибок. Действительно, при занесении в ЭП контрольных разрядов кодов с информационных входов 7, а в ЭП информационных

разрядов-кодов со входов 7 и 8 возникает несоответствие между информационными и контрольными разрядами записанных в накопитель 1 слов( несоответствием понимается то, что контрольные разряды,

записанные в накопитель 1, не соответствует тем, которые были бы получены по информационным разрядам входов 7 и -8 с помощью формирователя 3 .контрольных разрядов. Следовательно, при считывании

таких слов из накопителя 1 на выходах формирователя синдрома 5 будут присутствовать ненулевые коды. Т.е. путем анализа выводимых вместе с контрольными разрядами через второй мультиплексор 2 кодов

(дрома можно сделать вывод о работоспособности формирователя синдрома 5. который в сравнении с другими блоками 4 и 12, является наиболее сложной схемой. Если же.возникает необходимость в проверке

дешифратора синдрома 12 и блока 4 ynpaat

ляемых инверторов, то после занесения в

накопитель 1 ошибочной комбинации

информационных и контрольных разрядов

сигнал на входе 10 следует перевести в

состояние логической 1 (включение коррекции ошибок) и по тому, какие изменения претерпевает считанное из к акопителя 1 информационное слово на выходах 11, делают вывод о работоспособности схем коррекции ошибок.

Таким образом, технико-экономическое преимущество устройства заключается в упрощении контроля ОЗУ, что достигается за счет прямой проверки ЭП хранения контрольных разрядов, исключения отдельных циклов генерации ошибок в режимах записи для проверки схем коррекции ошибок и совмещения Q режиме считывания проверки ЭП контрольных разрядов и блока формированмя синдрома.

Формула изобретения Оперативное запоминающее устройство с коррекцией ошибок, содержащее формирователь контрольных разрядов, входы

которого являютс информационными входами первой и второй групп устройства, накопитель, адресные и управляющие Bxoti,bi которого являются входами управления накопителем устройства, выходы информационных и контрольных разрядов накопителя подключены к входам формирователя синдрома, выходы которого соединены с информационными входами дешифратора, выходы которого подключены к упраг ллющим входам блока управляемых инверторов. выходы которого являются информационными выходами устройства, а сигнальные входы соединены с выходами первого мультиплексора, информационные входы первого канала которого подключены к выходам информационных разрядов накопителя, информационные входы первой группы второго канала первого мультиплексора соединены с выходами контрольных разрядов накопителя, а управляющий вход первого мультиплексора является первым управляющим входом устройства, отличающееся тем, что, с целью упрощения контроля устройства, в него введен второй

мультиплексор, примем выходы формирователя синдрома подключены к информационным входам второй группы оторого канзла первого мультиплексора, управляющий эход rvovcporo соединен с управляю.ui-iM входом sTuparo мультиплексору, и,-(фопмзц 1онмы::. входы первой и второй групп которого подключзны соответственно к выходам форми; овагеля контрольных разрядов и к инфop iau-lOнным входам второй

группы устройства, входы информационных и контрольных разрядов накопителя соединены соответственно с информационными входами устройства с выходами .т -орого мультиплексора, управляющий входдешмфратора является вторым управляющим ЕЗХОдом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1644233A1 |

| Оперативное запоминающее устройство с коррекцией ошибок и резервированием | 1989 |

|

SU1709397A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1554030A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Одноразрядное оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539843A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

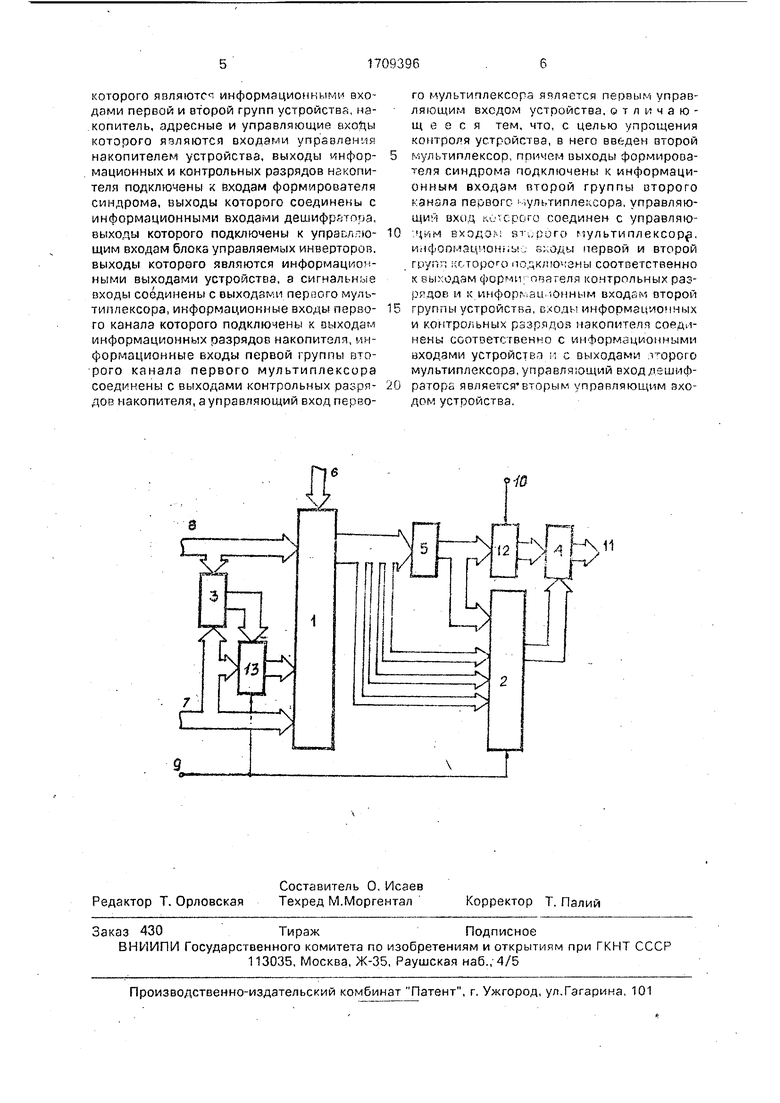

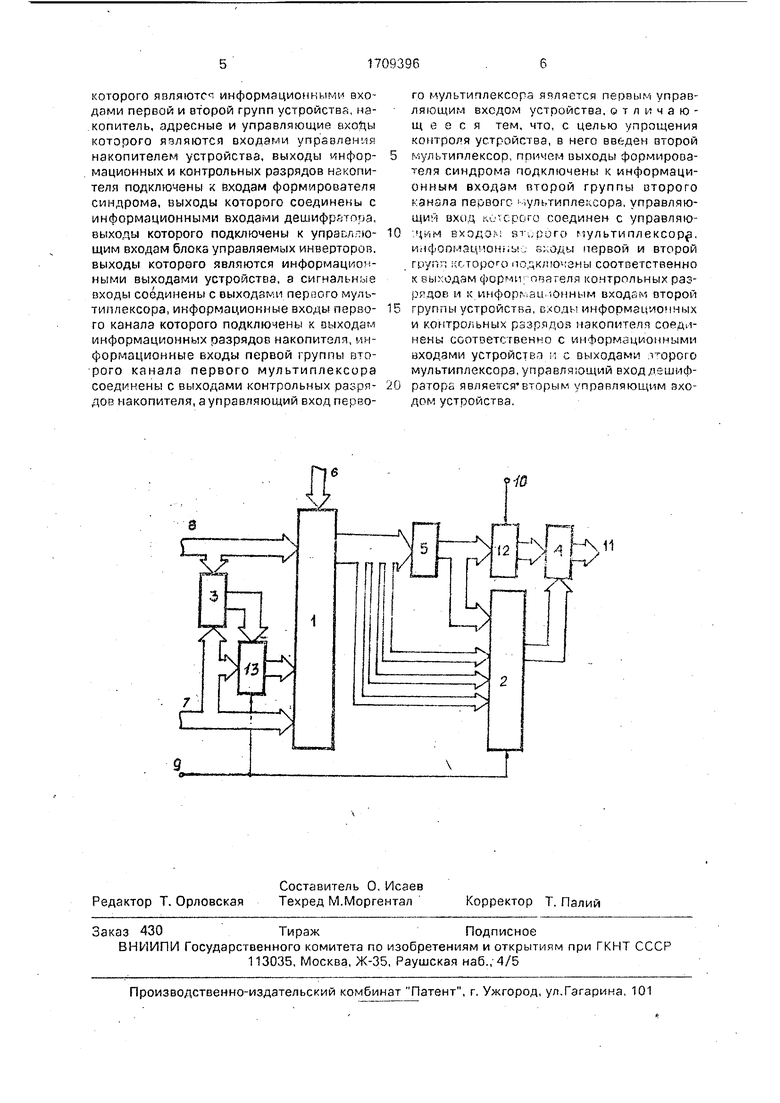

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекциейошибок, и может быть использовано при создании интегральных схем. Целью изо бретения является упрощение контроля устройства. Устройство содержит накопитель.- формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов, первый и второй мультиплексоры. Цель изобретения достигается за счет возможности непосредственной проверки избыточной части накопителя и исключения, отдельных циклов имитации ошибок в режимах записи для проверки схем коррекции, а также за счет совмещения в режиме считывания вывода на информационные выходы устройства контрольных разрядов и разрядов синдрома. 1 ил.Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекцией ошибок, и может быть использовано при создании интегральных схем.Целью изобретения является упрощение контроля устройства.На чертеже представлена структурная схема оперативного запоминающего устройства с коррекцией ошибок.Устройство содержит накопитель 1, первый мультиплексор 2, формирователь 3 контрольных разрядов, блок 4 управляемых инверторов, формирователь синдрома 5, входы 6 управления накопителем, информационные входы 7 и 8 первой и второй групп, первый 9 и второй 10 управляющие входы, информационные выходы 11, дешифратор 12 и второй мультиплексор 13.Устройство .работает следующим образом.Выбор режима работы устройства осуществляется с помощью управляющих сигналов с входов 9 и 10, а также с помощью сигнала "Запись/Считывание", поступающего на один из входов 6 устройства.Основные (рабочие) режимы работы устройства выбираются при установке на вХо- дах 10 и 9, положим, сигналов логической "1" и "О" соответственно! В этом случае при записи в накопитель 1 заносятся данные со входов 7 и 8, а также биты контрольных разрядов, сигналы которых снимаются с выходов формирователя 3. Положим также, что входное слово имеет восемь информационных разрядов и, следовательно, при использовании кодов Хзмминга число формируемых контрольных разрядов равно 4. При этом разбиение ворьми- входных информационных 'шин на входы 7 и 8 двух равных групп осуществляется произвольным образом.*слсVJ о о со ю о

А 11

.

| Огнев И.В., Сарычев К,Ф | |||

| Надежность запоминающих устройств | |||

| М.: Радио и связь, 1988, рис | |||

| Насос | 1917 |

|

SU13A1 |

| Поршень для воздушных тормозов с сжатым воздухом | 1921 |

|

SU188A1 |

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

Авторы

Даты

1992-01-30—Публикация

1988-11-24—Подача