XI

СЯ OJ

ю

кэ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1985 |

|

SU1257709A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1522293A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

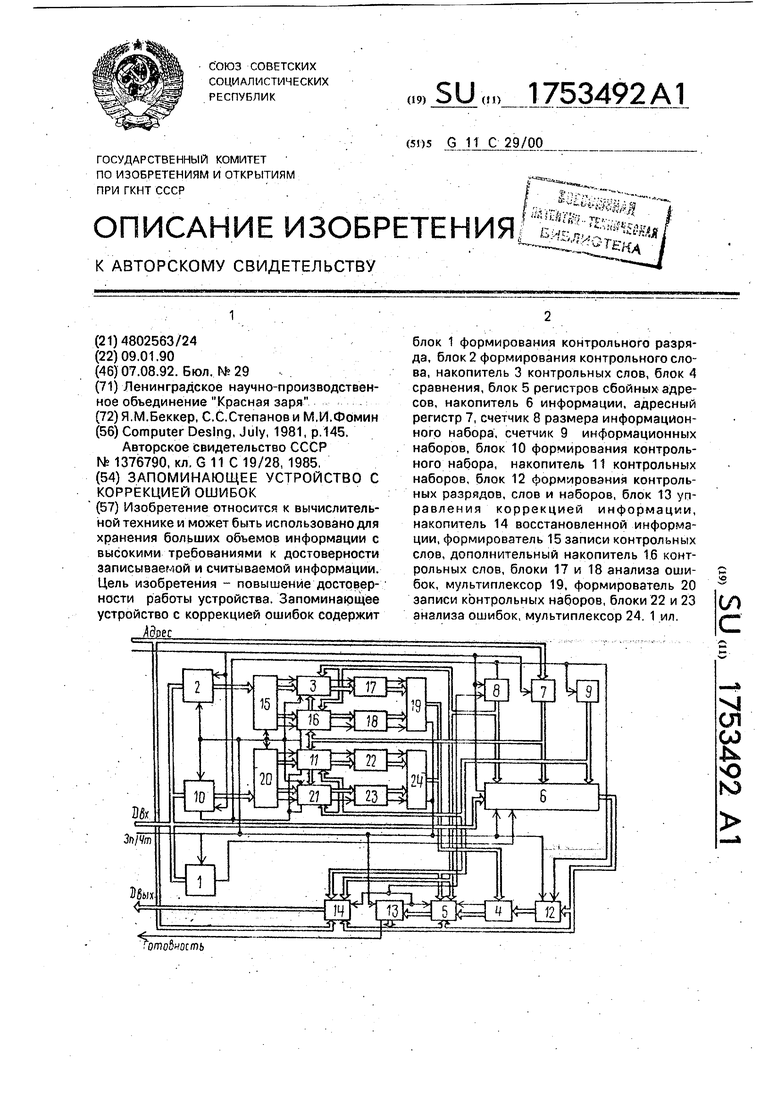

Изобретение относится к вычислительной технике и может быть использовано для хранения больших объемов информации с высокими требованиями к достоверности записываемой и считываемой информации. Цель изобретения - повышение достоверности работы устройства. Запоминающее устройство с коррекцией ошибок содержит Jfoec блок 1 формирования контрольного разряда, блок 2 формирования контрольного слова, накопитель 3 контрольных слов, блок 4 сравнения, блок 5 регистров сбойных адресов, накопитель 6 информации, адресный регистр 7, счетчик 8 размера информационного набора, счетчик 9 информационных наборов, блок 10 формирования контрольного набора, накопитель 11 контрольных наборов, блок 12 формирования контрольных разрядов, слов и наборов, блок 13 управления коррекцией информации, накопитель 14 восстановленной информации, формирователь 15 записи контрольных слов, дополнительный накопитель 16 контрольных слов, блоки 17 и 18 анализа ошибок, мультиплексор 19, формирователь 20 записи контрольных наборов, блоки 22 и 23 анализа ошибок, мультиплексор 24. 1 ил. СЛ С

чр пойг ость

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для хранения больших объемов информации с высоким требованием к достоверности считываемой информации.

Известно запоминающее устройство с коррекцией ошибок, основанное на принципе коррекции информации методом двухмерного паритета. Устройство содержит накопитель информации, блок формирования контрольного разряда по словам, блок формирования контрольного слова на массив информации, накопители контрольных разрядов и контрольных слов, блок сравнения информации, регистр адреса сбойных адресов и блок коррекции информации.

Недостатками такого запоминающего устройства являются возможность исправления только одиночных ошибок, встречающихся в массиве информации, невозможность увеличения массива информации и невозможность исправления двойных и более кратных ошибок.

Все это снижает надежность работы всего запоминающего устройства.

Наиболее близким к предлагаемому является запоминающее устройство с коррекцией ошибок.

Недостатком этого устройства является низкая надежность накопителей контрольных слов и наборов, которая становится определяющим фактором, влияющим на общую надежность устройства в целом.

Так возникновение обойной ситуации или отказа микросхемы в накопителях контрольных слов и наборов приводит к ошибочному исправлению считанной из накопителя информации в накопителе восстановленной информации или к отсутствию появления сигнала готовности устройства, что приводит к отказу устройства в целом.

Цель изобретения - повышение достоверности работы устройства.

Поставленная цель достигается тем, что в запоминающее устройство с коррекцией ошибок введены дополнительные накопители контрольных слов и контрольных наборов, формирователи записи контрольных слов и контрольных наборов с формированием контрольных разрядов, блоки анализа ошибок в накопителях и дополнительных накопителях контрольных слов и контрольных наборов и мультиплексоры выхода накопителей и дополнительных накопителей контрольных слов и контрольных наборов. Информационные входы формирователей записи контрольных слов и контрольных наборов соединены с информационными выходами блоков формирования контрольного

набора и контрольного слова. Информационные выходы мультиплексоров записи контрольных слов и контрольных наборов соединены с соответствующими информационными входами накопителей и дополнительных накопителей контрольных слов и контрольных наборов, входы режима которых объединены с входами режима накопителей контрольных слов и контрольных

наборов, выходы контрольных разрядов формирователей записи контрольных слов и контрольных наборов соединены с входами контрольных разоядов накопителей и дополнительных накопителей контрольных

слов и контрольных наборов Информационные выходы накопителей и дополнительных накопителей контрольных слов и контрольных наборов соединены с соответствующими информационными входами

блоков анализа ошибок в накопителях и дополнительных накопителях контрольных слов и контрольных наборов. Информационные выходы блоков анализа ошибок соединены с информационными входами

мультиплексоров, информационный выход которых объединен и соединен с информационным входом блока сравнения информации. Выходы сигнала ошибок блоков анализа ошибок в накопителях и дополнительных накопителях контрольных слов и контрольных наборов соединены с соответствующими входами ошибок мультиплексоров, адресные входы дополнительного накопителя контрольных слоев объединены

с соответствующими адресными входами накопителя контрольных слов, адресные входы дополнительного накопителя контрольных наборов объединены с соответствующими адресными входами накопителя

контрольных наборов.

Введение дополнительных накопителей контрольных слов и контрольных наборов формирователей записи контрольных слов и контрольных наборов с формированием

контрольных разрядов, блоков анализа ошибок в накопителях и дополнительных накопителях контрольных слов и контрольных наборов позволяет корректировать оди- ночные ошибки и сбои в. накопителях

контрольных слов и контрольных наборов, что повышает надежность коррекции ошибок и сбоев, возникающих в основном..

На чертеже представлено запоминающее устройство с коррекцией ошибок.

Устройство содержит блок Т формирования контрольного разряда, блок 2 формирования контрольного слова, накопитель 3 контрольных слов, блок 4 сравнения, блок 5 регистров сбойных адресов, накопитель б

информации, адресный регистр 7, счетчик 8

размера информационного набора, счетчик 9 информационных наборов, блок 10 формирования контрольного набора, накопитель 11 контрольных наборов, блок 12 формирования контрольных разрядов, слов и наборов, блок 13 управления коррекцией информации, накопитель 14 восстановленной информации, формирователь 15 записи контрольных слов, дополнительный накопитель 16 контрольных слов, блоки 17 и ,18 анализа ошибок, мультиплексор 19, формирователь 20 записи контрольных наборов, дополнительный накопитель 21 контрольных наборов, блоки 22 и 23 анализа ошибок, мультиплексор 24,

Устройство работает следующим образом,

Исходный пакет информации объемом n-разрядных слов делится на р информационных наборов, размером mxrt, где m - количество слов в наборе, п - разрядность слова, которые записываются в накопитель 6 информации, образуя трехмерную структуру. Запись информации осуществляется с помощью счетчика 8 размера информационного набора и счетчика 9 информационных наборов. При записи пакета рабочей информации одновременно формируются три контрольных набора х, у, г. Набор х образует контрольные разряды, полученные с помощью блока формирования контрольного разряда 1 в каждом информационном слове. Набор у составляет контрольные слова информационных наборов, получаемые операцией Сложение по модулю 2 над всеми словами контрольного набора в блоке 2 формирования контрольного слова на каждый информационный набор. Набор z формируется из контрольных слов, получаемых операцией Сложение по модулю 2 над первыми, вторыми и т.д. m-ми словами всех р информационных наборов в блоке 10 формирования контрольного набора на каждый информационный объем.

Слова контрольного набора у поступают через буфер 15 записи на входы накопителей информационных наборов 3 и 16. Буфер 15 записи формирует дополнительный контрольный разряд, полученный операцией Сложение по модулю 2 над разрядами слова контрольного набора, который записывается в накопители 3 и 16, Слова контрольного набора г поступают через буфер 20 записи на накопители 11 и 21 контрольных наборов.

Формирователь 20 записи формирует дополнительные контрольные разряды аналогично формирователю 15. Контрольный набор х запоминается в накопителе б вместе с рабочей информацией в виде одного

дополнительного бита на каждое слово. При считывании информации из накопителя 6 контрольные наборы х, у, z формируются аналогично режиму записи в блоке 12 фор- 5 мирования контрольных разрядов, слов и наборов. Эталонные наборы х, у, z, хранящиеся в накопителях 3,16,11 и 21 контрольных слов и наборов считываются через блоки 17, 18, 22 и 23 анализа ошибок. При 10 появлении ошибки или сбоя в одном из накопителей информационных слов или наборов блоки анализа ошибок определяют ее наличие в одном из накопителей контрольных слов или наборов методом сравнения 15 дополнительного контрольного разряда, считанного из накопителей с вновь сформированными контрольными разрядами информации в блоках анализа ошибок. При этом блоками анализа ошибок вырабатыва- 0 ются управляющие сигналы, подключающие через мультиплексора 19 .и 24 накопители, не содержащие ошибки или сбои, к входу блока 4 сравнения

В блоке 4 сравнения сравниваются эта- 5 лонные наборы х, у, z с вновь полученными. Результаты сравнения записываются в блок 5 регистров сбойных адресов. Параллельно осуществляется передача рабочей информации из накопителя 6 в накопитель 14 вос- 0 становленный информации. Исправление ошибочной информации осуществляется в соответствии с обобщенным алгоритмом, приведенном в прототипе.

Формула изобретения 5 Запоминающее устройство с коррекцией ошибок, содержащее блок формирова- ния контрольного разряда, блок формирования контрольного слова, блок формирования контрольного набора, счет- 0 чик размера информационного набора, счетчик информационных наборов, адресный регистр, накопители информации контрольных слов, контрольных наборов, блок формирования контрольных разрядов, слов 5 и наборов, блок сравнения, блок регистров сбойных адресов, блок управления коррекцией информации, накопитель восстановленной информации, соответствующие информационные входы накопителя инфор- 0 мации и входы блоков формирования контрольных наборов, разряда и слова объединены и являются информационными входами устройства, входы задания режима накопителя информации, блоков формиро- 5 вания контрольного разряда, слова и контрольных наборов, накопителей контрольных слов и контрольных наборов, блока управления коррекцией информации и блока формирования контрольных разрядов, слов и наборов объединены и являются

ходом задания режима устройства, входы азрешения обращения накопителя инфорации, разрешения работы блоков формиования контрольных слов и наборов, входы инхронизации счетчика размера информаионного набора и адресного регистра объдинены и являются входом обращения стройства, адресные входы накопителя восстановленной информации и адресного регистра объединены и являются адресными входами устройства, вход Контрольного разряда накопителя соединен с выходом блока формирования контрольного разряда, выходы адресного регистра соединены с адресными входами накопителя информации и накопителей контрольных слов и наборов, выходы счетчика размера информационного набора соединены с входами адреса накопителя информации, блока регистров сбойных адресов, накопителей контрольных слов и восстановленной информации, выходы счетчика размера информационного набора соединены с входами старшего разряда накопителя контрольных наборов, входом блока формирования контрольного набора, входом блока формирования контрольных слов, разрядов и наборов, входом синхронизации счетчика информационных наборов, выходы которого соединены с входами адреса набора накопителя информации, накопителей контрольных наборов и восстановленной информации и информационными входами блока регистров сбойных адресов, информационные входы блока формирования контрольных разрядов, слов и наборов соединены с информационными входами блока регистров сбойных адресов и накопителя восстановленной информации и выходами накопителя информации и блока управления коррекцией информации, выходы блока формирования контрольных разрядов, наборов и слов соединены с входами первой группы блока сравнения, информационные и управляющий выходы которого соединены с информационными входами и входом задания режима блока регистров сбойных адресов, выходы которых соединены с информационными входами блока управления коррекцией информации, выход опроса блока управления коррекцией информации соединен с входом синхронизации счетчика размера информационного набора, входа- ми разрешения блока регистров сбойных адресов и накопителя восстановленной информации, выход готовности блока управления коррекцией информации является выходом готовности устройства, выходы накопителя восстановленной информации являются информационными выходами

устройства, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены дополнительные накопители контрольных слов и наборов,

первый, второй, третий и четвертый блоки анализа ошибок, первый и второй мультиплексоры, формирователи записи контрольных слов и наборов, информационные входы формирователей записи контрольных

0 слов и наборов соединены соответственно с выходами блоков формирования контрольного набора и слова, первые и вторые выходы формирователей контрольных слов и наборов соединена соответственно с ин5 формационными входами накопителей и дополнительных накопителей контрольных слов и наборов, входы задания режима формирователей записи контрольных слов и наборов соединены с входами задания ре0 жима накопителей контрольных слов и наборов, первый и второй контрольные выходы формирователей записи контрольных слов и наборов соединены соответственно с первым и вторым контрольными

5 входами накопителя и дополнительного накопителя контрольных слов и с первым и вторым контрольными входами накопителя и дополнительного накопителя контрольных наборов, выходы накопителей и допол0 нительных накопителей контрольных слов и наборов соединены соответственно с входами первого, второго, третьего и четвертого блока анализа ошибок, выходы сигнала ошибки накопителя и дополнительного на5 копителя контрольных слов соединены с входами ошибки первого и второго блока анализа ошибки, выходы сигнала ошибки накопителя и дополнительного накопителя контрольных наборов соединены с входами

0 ошибки третьего и четвертого блока анализа ошибок, выходы первого и второго блоков анализа ошибок соединены соответственно с информационными входами первой и второй группы первого мультиплексора, пер5 вый и второй управляющие входы которого соединены с выходами ошибки первого и второго блока анализа ошибок, выходы третьего и четвертого блоков анализа ошибок соединены соответственно с информа0 ционными входами первой и второй группы второго мультиплексора, первый и второй управляющие входы которого соединены с выходами ошибки третьего и четвертого блоков анализа ошибки, соответствующие

5 выходы первого и второго мультиплексоров объединены и соединены с входами второй группы блока сравнения, адресные входы дополнительного накопителя контрольных слов объединены с соответствующими ад- ресными входами накопителя контрольных

слов, адресные входы дополнительного на-. с соответствующими адресными входами копителя контрольных наборов объединены накопителя контрольных наборов.

| Computer Deslng, July, 1981, p.145 | |||

| Авторское свидетельство СССР № 1376790, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-08-07—Публикация

1990-01-09—Подача