Изобретение относится к вычислительной технике, в частности к запоминающим устройствам со встроенной коррекцией ошибок, и может быть использсзано при создании интегральных схем.

Цель изобретения - расширение функциональных возможностей устройства за счет контроля состояния накопителя в процессе эксплуатации.

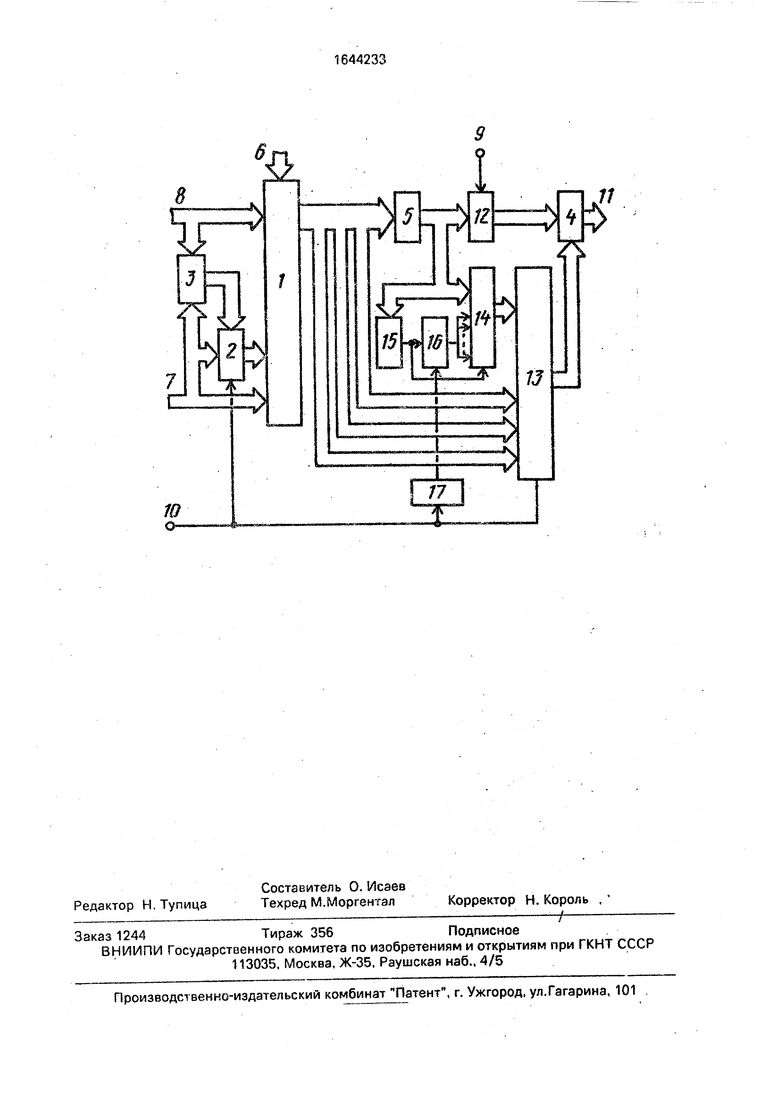

На чертеже представлена структурная схема оперативного запоминающего устройства с коррекцией ошибок.

Ус ройство содержит накопитель 1, первый мультиплексор 2, формирователь 3 контрольных разрядов, блок 4 управляемых инверторов, формирователь 5 синдрома, входы 6 управления накопителем, информационные входы первой 7 и второй 8 групп,

первый 9 и второй 10 управляющие входы, информационные выходы 11, дешифратор 12, второй 13 и третий 14 мультиплексоры, элемент ИЛИ 15, триггер 16 и формирователь 17 импульса.

Устройство работает следующим образом.

Пусть число информационных разрядов в записываемом в накопитель 1 слове данных равно восьми. Следовательно, при использовании кода Хэмминга число контрольных разрядов, формируемых блоком 3, равно четырем. Тогда шины входных информационных разрядов произвольно разбиваются на две группы 7 и 8, содержащие по четыре шины.

В основном рабочем режиме, при котором на управляющих входах 9 и 10 поддерО

fc

ГО GO СО

живаются, положим, сигналы уровней 1 и О соответственно, мультиплексор 2 пропускает на входы контрольных разрядов накопителя 1 сигналы с выходов формирователя 3 контрольных разрядов, второй мульти-. плексор 13 - сигнал с выходов информационных разрядов накопителя, а дешифратор 12 осуществляет расшифровку кода синдрома для последующего исправления ошибок в блоке 4 управляемых инверторов.

В тестовых режимах осуществляется проверка работоспособности ЭП накопителя 1 хранения информационных и контрольных разрядов слов данных. При этом при поддержании в режиме записи на ВХОДР 10 сигнала уровней соответственно 1 или О осуществляется запись в ЭП накопителя 1 хранения контрольных разрядов либо с информационных входов 7 первой группы, либо с выходов схемы формирователя контрольных разрядов. Запись информации с входов 7 необходима для прямой проверки работоспособности ЭП контрольных разрядов.

В тестовых режимах считывания сигналом входа 9 уровня логического О может быть запрещено инвертирование блоком 4 выходных сигналов второго мультиплексора 13, т.е. запрещается коррекция ошибок. Это необходимо для осуществления собственно прямой проверки работоспособности всего накопителя 1, В таком цикле проверки при поддержании на входе 10 сигнала низкого уровня на выходы 11 через второй мультиплексор 13 сигналы поступают непосредственно с выходов информационных разрядов накопителя 1 (первые две группы входов второго мультиплексора 13), а при установке его равным единице на выходы 11 поступают 4-разрядный код с выходов контрольных разрядов накопителя 1 (третья группа входов второго мультиплексора 13) и 4-разрядный код с выходов третьего мультиплексора 14 (четвертая группа входов второго мультиплексора 13).

Рассмотрим более подробно сигналы, формируемые на выходах третьего мультиплексора 14.

Поскольку в режиме проверки ЭП информационных разрядов накопителя I на входы мультиплексора 13 поступает 8-разрядный код, а при проверке ЭП контрольных разрядов - 4-разрядный код, то оставшиеся четыре входа мультиплексора J3 могут быть использованы для вывода полезной для разработчика (пользователя) информации. Такой информацией является, например, 4-разрядный код синдрома, формируемый схемой 5. На этапе тестирования ОЗУ анализ кодов синдрома позволяет сделат иывсд о работоспособности схем коррекции ошибок, а при обычной эксплуатации ОЗУ - о наличии ошибки в считываемом из накопителя слове.

Для осуществления контроля за состоянием накопителя и за условиями эксплуатации устройства в состав ОЗУ введен также элемент ИЛИ 15 и триггер 16. Если при считывании слова из накопителя 1 в нем

0 схемой 5 формирования синдрома обнаружена ошибка (ненулевой код синдрома), на выходе элемента ИЛИ 15 будет сформирован сигнал логической 1, а триггер 16 переключится в состояние 1. Такое

5 состояние триггер 16 будет сохранять до момента вызода информации о нем на выходы 11 устройства. Для оюго на вход 10 поступает сигнал высокого уровня, переключающий мультиплексор 13 на вывод ин0 формации с выходов мультиплексора 14. Если на этапе подобной проверки на выходе элемента ИЛИ 75 установлен сигнал уровня логического О (т.е., в данный момент из накопителя 1 считывается слово, не содер5 жащее ошибок), то на соответствующие выходы третьего мультиплексора 14 сигналы поступают с выхода триггера 16 ошибки. При этом, если триггер 15 находится в нулевом состоянии (т.е., с момента предшеству0 ющей проверки не были зарегистрированы ошибки в считанных словах данных), на выход мультиплексора 14 поступает код 0000. Таким образом, наличие кода 0000 на выходах мультиплексора 14 указывает на то, что

5 как на этапе предшествующей проверки, так и при данном конкретном обращении к накопителю 1 ошибки не были зарегистрированы.

Если ч риггер 16 установлен в состояние

0 логической 1 (т.е., за время, прошедшее с момента окончания предыдущей проверки, в считанны из накопителя словах была обнаружена по крайней мере одна ошибка), на ° выходы мультиплексора 16 поступает код

5 1111. При этом кодирующая матрица формирования контрольных разрядов всегда может быть выбрана для кода Хэмминга (12,8) такой, ч го при однократных ошибках код синдрома никогда не будет равен 1111.

0 Поэтому, если на этапе рассматриваемой проверки на выходах 11 устройства присутствует подобный код, зто однозначно указывает на отсутствие ошибки в выводимом из накопителя слове в данный момент и на

5 регистрацию ошибки (или ошибок) на предшествующем гтапе проверки,

Если при такой проверке на выходе элемента ИЛИ 15 появляется сигнал логической 1, следовательно, в счмтанном из накопителя 1 слове зарегистрирована

ошибка, и на выходы мультиплексора 14 поступают сигналы кода синдрома (вывод сигнала о состоянии триггера 16 в таком случае не будет сообщать кэкую- либо дополнительную полезную информацию, поскольку этим же сигналом уровня 1 элемента ИЛИ 15 триггер 16 будет установлен в состояние логической 1).

Установка триггера 16 ошибки происходит сигналом схемы ИЛИ 15 (в начале работы устройства он установлен в состояние логического О), а сброс осуществляется в конце каждого этапа проверки с помощью сигнала формирователя 17. который выделяет импульс требуемой длительности при поступлении фронта спада сигнала на управляющем входе 10 (такая проверка может занимать как один, так и несколько циклов обращения к накопителю 1).

Формула изобретения Оперативное запоминающее устройство с коррекцией ошибок, содержащее накопитель, первый мультиплексор, формирователь контрольных разрядов, формирователь синдрома, блок управляемых инверторов, причем входы информационных разрядов первой и второй групп накопителя являются информационными входами устройства и соединены с входами формирователя контрольных разрядов, адресные и управляющие входы накопителя являются одноименными входами устройства, а выходы информационных и контрольных разрядов подключены к входам формирователя синдрома, выходы блока управляемых инверторов являются информационными выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля состояния накопителя в

процессе эксплуатации, в устройст во введены второй и третий мультиплексоры, дешифратор, элемент ИЛИ, триггер и формирователь импульса, причем информа- 5 ционные входы перзой и второй групп пер- чого мультиплексора соединены соответственно с выходами формирователя контрольных разрядов и с информационными входами второй группы накопителя, вхо0 ды контрольных разрядов которого подключены ч выхоДам второго мультиплексора, выксдь1 формирователя синхрома сое- динены с входами элемента ИЛИ, с информационными входами первой группы

5 второго мультплехсора и с информационными входами дешифратора, управляющий вход которого является первым управляющим входом устройства, а выходы подключены к первым входам блока управляемых

0 инверторов, вторые входы которого соединены с выходами второго мультиплексора, информационные входы первой группы которого подключены к выходам информационных разрядов накопителя, одни

5 информационные входы второй группы второго мультиплексора соединены с выходами третьего мультиплексора, другие информационные входы второй груяггы подключены к выходам контрольных разрядов

0 накопителя, а управляющий вход второго мультиплексора является вторым управляющим входом устройства м соединен с управляющим входом первого мультиплексора и с входом формироаателя импульсов, выход

5 которого подключен к синхровходу триггера, информационный вход которого подключен к выходу элемента ИЛИ и к управляющему входу третьего мультиплексора, информационные входы второй груп0 пы которого соединены с выходом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1709396A1 |

| Оперативное запоминающее устройство с коррекцией ошибок и резервированием | 1989 |

|

SU1709397A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1985 |

|

SU1257709A1 |

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам со встречной коррекцией ошибок, и мохет быть использовано прл создании интегральных схем. Целью изобретения является расширение функциональных возможностей устройства за счет контроля состояния накопителя в процессе эксплуатации. Устройство содержит накопитель, формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов, первый, второй и третий мультиплексоры, элемент ИЛИ, триггер и формирователь импульса. Цель изобретения достигается тем, что в процессе эксплуатации сигнал ошибки, формируемый элементом ИЛИ по ненулевому синдрому, фиксируется в триггере. В режиме тестирования состояние триггера через второй и третий мультиплексоры выводится на информационные выходы для анализа. 1 ил.

| Патент США №4335459, кл | |||

| , 1982 | |||

| Патент США № 4561095 кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

Авторы

Даты

1991-04-23—Публикация

1988-11-24—Подача