Изобретение относится к вычислительной технике и может быть использовано в блоках синхронизации с адаптацией времени выдачи синхронизирующих сигналов

Цель изобретения - повышение надежности за счет сокращения времени коррекции временной диаграммы

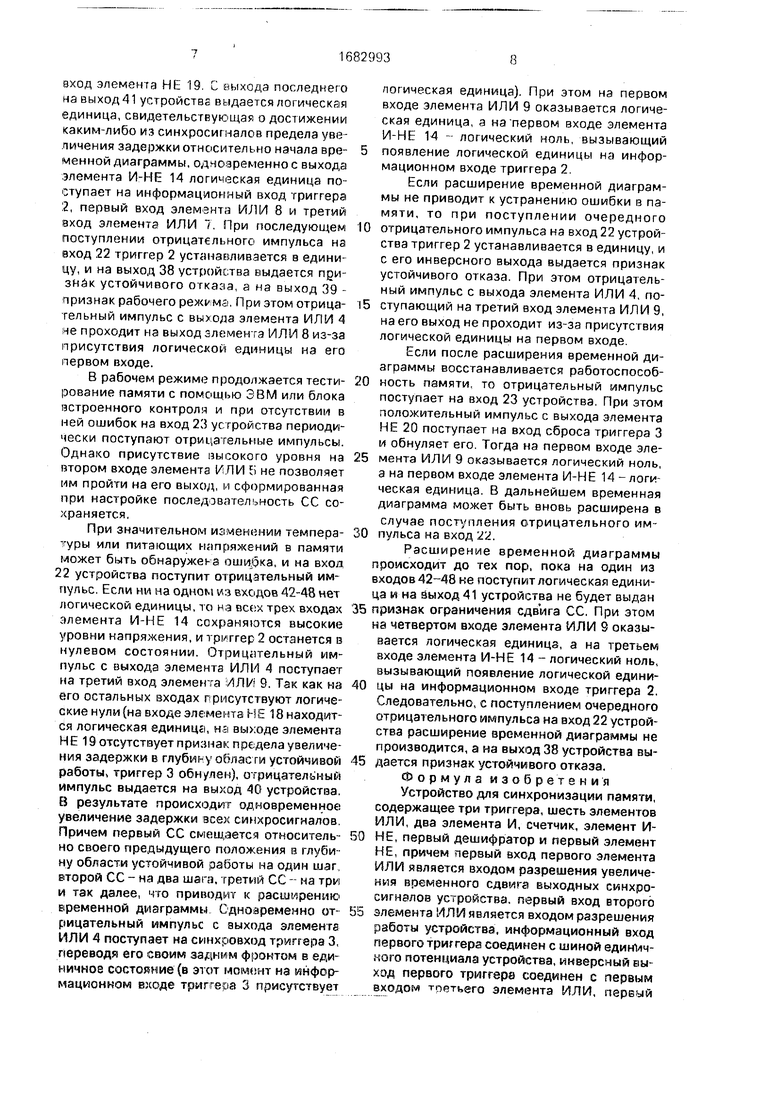

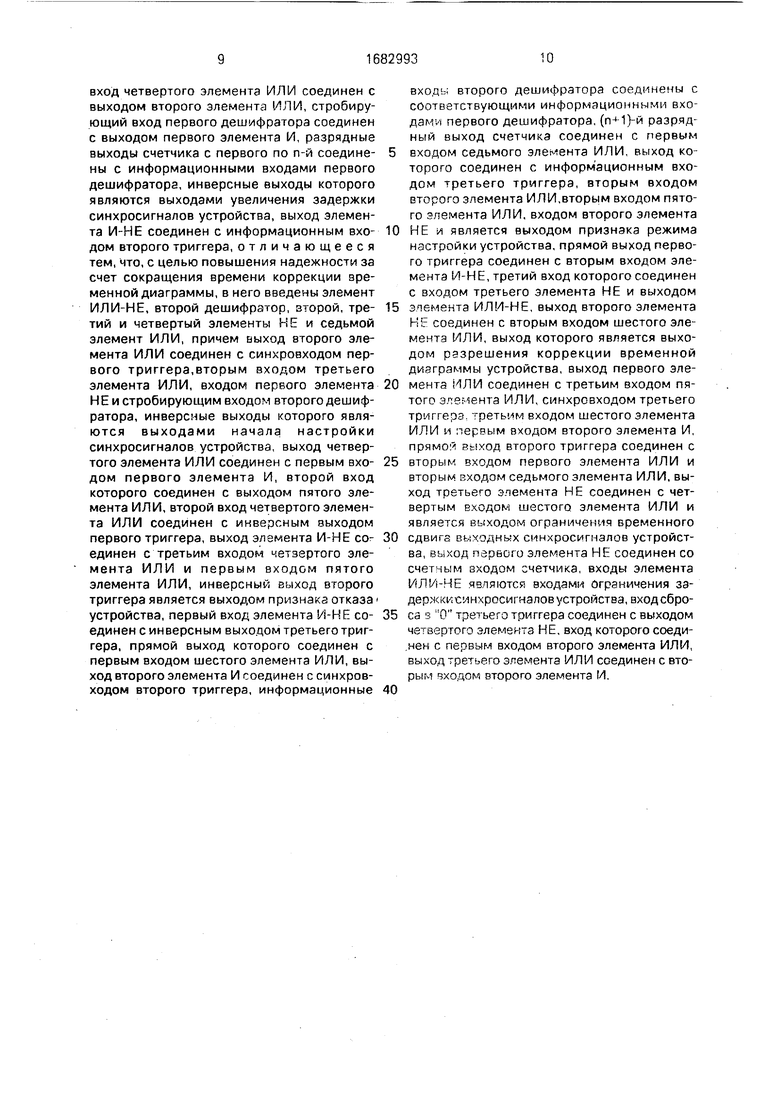

На чертеже представлена схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 триггеры, первый 4. второй 5, третий 6, четвертый 7, пятый 8, шестой 9 и седьмой 10 элементы ИЛИ, первый 11 и второй 12 элементы И, счетчик 13, элемент И-НЕ 14. первый 15 и второй 16 дешифраторы, первый 17, второй 18, третий 19 и четвертый 20 элементы НЕ и элемент И-НЕ 21, вход 22 разрешения увеличения временного сдвига выходных синхросигналов устройства, вход 23 разрешения работы устройства, выходы 24-30 увеличения задержки синхросигналов, выходы 31-37 начала настройки синхросигналов, выход 38 признака отказа, выход 39 признака режима

настройки, выход 40 разрешения коррекции временной диаграммы выход 41 ограничения временного сдвига выходных синхро сигналов, группу входов 42-48 ограничения задержки

Устройство работает следующим образом.

Вначале устройство приводится в исходное состояние путем обнуления триггеров 1 и 2 и счетчика 13 (цепь начальной установки на чертеже не показана) После этого устройство переходит в режим на- стоойки синхросигналов (СС), в процессе ко- торой с помощью ЭВМ или средств встроенного контроля проводится тестирование управляемого объекта, например оперативной памяти. При каждом обращении к ней формирователь синхросигналов выдает последовательность СС, время задержки между которыми определяется числом разделяющих их элементарных шагов, причем начальная последовательность СС устанавливается с достаточно большими временными интервалами между всеми синхросигналами.

in

о

00

ю ю ю со

что гарантирует надежную работу памяти, но не обеспечивает высокого быстродействия, для повышения быстродействия устройство выдает в формирователь синхросигналов управляющие сигналы, вы зывающие сдвиг СС. Настройка заканчивается установкой всех синхросигналов вблизи границы области устойчивой работы, на расстоянии, обеспечивающем надежную работу ОЗУ при небольших колебаниях температуры и питающих напряжений. По окончании настройки устройство переходит в рабочий режим, в течение которого производится запись и считывание из ОЗУ полезной информации.

В рабочем режиме в оперативной памяти возможно появление сбоев, например из-за значительных изменений температуры или питающих напряжений, вероятность которых возрастает с увеличением продолжительности работы ОЗУ. При этом установленных в режиме настройки интервалов между СС может оказаться недостаточно для надежного функционирования памяти в новых условиях. В последнем случае устройство формирует управляющие сигналы, вызывающие сдвиг СС в глубину области устойчивой работы на небольшое число элементарных шагов, повышая тем самым надежность работы ОЗУ без значительного снижения быстродействия.

Назначение входных и выходных сигналов устройства состоит в следующем.

Последовательность импульсов на каждом из выходов 24-30 вызывает постепенное увеличивание задержки соответствующего СС с шагом с. Импульс на каждом из выходов 31-37 означает переход к настройке соответствующего СС, вызывая его смещение к началу формирования временной диаграммы.

Выход 40 - разрешение коррекции (РК) - импульс на этом выходе вызывает расши рение временной диаграммы в рабочем режиме.

Выход 39 - низкий уровень - режим настройки, высокий - рабочий режим (РР)

Выход 38 - низкий уровень означает наличие в памяти устойчивого отказа (УО), независящего от ее временной диаграммы

Выход 41 - ограничение сдвига (ОС) высокий уровень указывает на невозможность дальнейшего увеличения задержки синхросигналов.

Входы 23 и 22 - конец тестирования (КТ) и ошибка (ОШ) - появление импульса на одном из этих входов означает соответст венно работоспособность и неработосгю собность памяти при данной временной диаграмме.

Входы 42-48 - высокие уровни указывают на невозможность дальнейшего увеличения задержки соответствующего СС.

Так как начальная последовательность

СС устанавливается формирователем синхросигналов с достаточно большими интервалами между всеми синхронизирующими сигналами, то при отсутствии в памяти неисправности ее тестирование закончится

0 успешно и на вход 23 устройства будет выдан отрицательный импульс. В дальнейшем он поступит на первый вход элемента ИЛИ 5 и вход элемента НЕ 20, пройдя который, обнулит триггер 3. Так как триггер 2 и счет5 чик 13 находятся в нулевом состоянии, на выходе элемента ИЛИ 10 и втором входе элемента ИЛИ 5 присутствует логический ноль (низкий уровень напряжения). В результате отрицательный импульс проходит

0 элемент ИЛИ 5 и поступает на стробирую- щий вход дешифратора 16. В этот момент на информационных входах дешифратора 16 присутствуют логические нули, поэтому отрицательный импульс появится на его пер5 вом выходе, с выхода 31 устройства он выдается в формирователь синхросигналов, что вызывает сдвиг первого СС с некоторого исходного положения в начало временной диаграммы. Одновременно отрицательный

0 импульс с выхода элемента ИЛИ 5 проходит элемент НЕ 17, при этом на суммирующем входе счетчика 13 появляется положительный импульс, который своим задним фронтом увеличивает его содержимое на

5 единицу и на информационных входах дешифраторов 15 и 16 оказывается код (001). Отрицательный импульс с выхода элемента ИЛИ 5 поступает также на второй вход элемента ИЛИ 6 и первый вход элемента ИЛИ

0 7, но на их выходы не проходит, так как триггер 1 обнулен и на первом входе элемента ИЛИ 6 и втором входе элемента ИЛИ 7 присутствуют логические единицы (высокие уровни напряжения).

5По заднему фронту отрицательного импульса на выходе элемента ИЛИ 5 триггер 1 переходит в единичное состояние и на первом входе элемента ИЛИ 6 и втором входе элемента ИЛИ 7 появляются логические ну0 ли. Логическая единица с прямого выхода триггера 1 псступает на второй вход элемента И-НЕ 14, на всех трех входах которого оказываются высокие уровни напряжения, логический ноль с его выхода поступает на

5 третий вход элемента ИЛИ 7. первый вход элемента ИЛИ 8 и информационный вход триггера 2.

Если смещение первого СС в начало временной диаграммы вызывает нарушение работоспособности памяти, отрицательный импульс поступает на вход 22 устройства, он проходит элемент ИЛИ 4 и поступает на третий вход элемента ИЛИ 8 и первый вход элемента И 12. С выхода последнего отрицательный импульс поступает на синхровход триггера 2, однако его состояние не изменится, поскольку на информационном входе присутствует низкий уровень напряжения. На первом и втором входах элемента ИЛИ 8 находятся логические нули, поэтому отрицательный импульс проходит на его выход и поступает на второй вход элемента И 11, а затем на строби- рующий вход дешифратора 15, поскольку на его информационных входах присутствует код (001), то отрицательный импульс выдается на выход 24 устройства, что вызывает увеличение задержки первого СС на один шаг Ј . При поступлении отрицательного импульса вновь на вход 22 процесс повторяется.

Постепенное наращивание числа шагов между началом временной диаграммы и первым СС происходит до тех пор, пока работоспособность памяти не восстанавливается и отрицательный импульс не поступит на вход 23 устройства. С выхода элемента ИЛИ 5 он проходит на первый вход элемента ИЛИ 7, поскольку на его втором и третьем входах присутствуют логические нули, то отрицательный импульс оказывается на первом входе элемента И 11 и далее поступает на стробирующий вход дешифратора 15, при этом обеспечивая дополнительный сдвиг первого СС на один шаг в глубину области устойчивой работы (успешное прохождение теста без такого сдвига может быть случайным). Одновременно отрицательный импульс с выхода элемента ИЛИ 5 поступает на стробирующий вход дешифратора 16. Так как на его информационных входах присутствует код (001), то отрицательный импульс выдается на выход 32 устройства, что приводит к смещению второго СС в начало временной диаграммы. Отрицательный импульс с выхода элемента ИЛИ 5 также поступает на вход элемента НЕ 17. На суммирующем входе счетчика 13 появляется положительный импульс, своим задним фронтом увеличивающий его содержимое на единицу, и на информационных входах дешифраторов 15 и 16 оказывается код (010).

Установка синхросигналов со второго по седьмой происходит аналогично.

При настройке седьмого СС на информационных входах дешифратора 15 присутствует код (111). По окончании настройки на вход 23 устройства поступает отрицательный импульс. Пройдя элемент ИЛИ 5, элемент ИЛИ 7, элемент И 11, дешифратор 15, он выдается на выход 30 устройства, вызывая дополнительный сдвиг седьмого СС на один шаг. Одновременно по заднему фрон- 5 ту положительного импульса на выходе элемента НЕ 17 содержимое счетчика 13 увеличивается на единицу. При этом на его первых разрядных выходах оказываются логические нули, а на последнем - логическая

10 единица, поступающая на первый вход элемента ИЛИ 10. В результате, на выход 39 устройства выдается признак рабочего режима, свидетельствующий о готовности памяти к работе. Логическая единица с выхода

5 элемента ИЛИ 10 также поступает на вход элемента НЕ 18, информационный вход триггера 3 и вторые входы элементов ИЛИ 5 и 8. Таким образом, прохождение последующих импульсов со входа 23 устройства

0 на выход элемента ИЛИ 5 блокируется логической единицей на его втором входе.

Если в памяти присутствует неисправность, не зависящая от ее временной диаграммы, то отрицательный импульс после

5 первого тестирования поступит на вход 22 устройства. В этот момент на втором входе элемента ИЛИ 4 присутствует низкий уровень напряжения, так как триггер 2 обнулен. Отрицательный импульс со входа 22 прохо0 дит на выход элемента ИЛИ 4 и, пройдя через элемент И 12, поступает на синхроо- ход триггера 2. На его информационном входе присутствует высокий уровень напряжения, поскольку триггер 1 находится в ну5 левом состоянии и на втором входе элемента И-НЕ 14 присутствует логический ноль. В результате триггер 2 переходит в единичное состояние и с его инверсного выхода на вход 38 устройства выдается при0 знак устойчивого отказа. Одновременно логическая единица с прямого выхода триггера 2 поступает на второй вход элемента ИЛИ 10, а затем на выход 39 как признак рабочего режима.

5 В случае, если при настройке какого-либо из синхросигналов в ОЗУ появилась неисправность, не зависящая от его временной диаграммы, to отрицательный импульс выдается на вход 22 устройства до

0 тех пор, пока на соответствующий вход 42- 48 не поступает логическая единица, причем на вход 42 логическая единица подается при достижении первым СС максимально возможной задержки, на вход 43 - при дости5 жении вторым СС максимально возможной задержки, которая меньше максимальной на один шаг, на вход 44 - на два шага и так далее. При этом на выходе элемента ИЛИ- НЕ 21 оказывается логический ноль, поступающий на третий вход элемента И-НЕ 14 и

вход элемента НЕ 19. С выхода последнего на выход 41 устройства выдается логическая единица, свидетельствующая о достижении каким-либо из синхросигналов предела увеличения задержки относительно начала временной диаграммы, одновременно с выхода элемента И-НЕ 14 логическая единица поступает на информационный вход триггера 2, первый вход элемента ИЛИ 8 и третий вход элемента ИЛИ 7. При последующем поступлении отрицательного импульса на вход 22 триггер 2 устанавливается в единицу, и на выход 38 устройства выдается признак устойчивого отказа, а на выход 39 - признак рабочего режима. При этом отрицательный импульс с выхода элемента ИЛИ 4 не проходит на выход элемента ИЛИ 8 из-за присутствия логической единицы на его первом входе.

В рабочем режиме продолжается тестирование памяти с помощью ЭВМ или блока встроенного контроля и при отсутствии в ней ошибок на вход 23 устройства периодически поступают отрицательные импульсы, Однако присутствие высокого уровня на втором входе элемента ИЛИ 5 не позволяет им пройти на его выход, и сформированная при настройке последовательность СС сохраняется.

При значительном изменении температуры или питающих напряжений в памяти может быть обнаружена ошибка, и на вход 22 устройства поступит отрицательный импульс. Если ни на одном из входов 42-48 нет логической единицы, то на всех трех входах элемента И-НЕ 14 сохраняются высокие уровни напряжения, и триггер 2 останется в нулевом состоянии. Отрицательный импульс с выхода элемента ИЛИ 4 поступает на третий вход элемента ИЛИ 9. Так как на его остальных входах присутствуют логические нули (на входе элемента НЕ 18 находится логическая единица, на выходе элемента НЕ 19 отсутствует признак предела увеличения задержки в глубину области устойчивой работы, триггер 3 обнулен), отрицательный импульс выдается на выход 40 устройства. В результате происходит одновременное увеличение задержки всех синхросигналов. Причем первый СС смещается относительно своего предыдущего положения в глубину области устойчивой работы на один шаг, второй СС - на два шага, третий СС - на три и так далее, что приводит к расширению временной диаграммы. Одновременно отрицательный импульс с выхода элемента ИЛИ 4 поступает на синхровход триггера 3, переводя его своим задним фронтом в единичное состояние (в этот момент на информационном входе триггера 3 присутствует

логическая единица). При этом на первом входе элемента ИЛИ 9 оказывается логическая единица, а на первом входе элемента И-НЕ 14 логический ноль, вызывающий

появление логической единицы на информационном входе триггера 2

Если расширение временной диаграммы не приводит к устранению ошибки в памяти, то при поступлении очередного

0 отрицательного импульса на вход 22 устройства триггер 2 устанавливается в единицу, и с его инверсного выхода выдается признак устойчивого отказа. При этом отрицательный импульс с выхода элемента ИЛИ 4, по5 ступающий на третий вход элемента ИЛИ 9, на его выход не проходит из-за присутствия логической единицы на первом входе.

Если после расширения временной диаграммы восстанавливается работоспособ0 ность памяти, то отрицательный импульс поступает на вход 23 устройства. При этом положительный импульс с выхода элемента НЕ 20 поступает на вход сброса триггера 3 и обнуляет его. Тогда на первом входе эле5 мента ИЛИ 9 оказывается логический ноль, а на первом входе элемента И-НЕ 14 - логи ческая единица. В дальнейшем временная диаграмма может быть вновь расширена в случае поступления отрицательного им0 пульса на вход 22.

Расширение временной диаграммы происходит до тех пор, пока на один из входов 42-48 не поступит логическая единица и на выход 41 устройства не будет выдан

5 признак ограничения сдвига СС. При этом на четвертом входе элемента ИЛИ 9 оказывается логическая единица, а на третьем входе элемента И-НЕ 14 - логический ноль, вызывающий появление логической едини0 цы на информационном входе триггера 2. Следовательно, с поступлением очередного отрицательного импульса на вход 22 устройства расширение временной диаграммы не производится, а на выход 38 устройства вы5 дается признак устойчивого отказа. Формула изобретения Устройство для синхронизации памяти, содержащее три триггера, шесть элементов ИЛИ, два элемента И, счетчик, элемент И0 НЕ, первый дешифратор и первый элемент НЕ, причем первый вход первого элемента ИЛИ является входом разрешения увеличения временного сдвига выходных синхросигналов устройства, первый вход второго

5 элемента ИЛИ является входом разрешения работы устройства, информационный вход первого триггера соединен с шиной единичного потенциала устройства, инверсный выход первого триггера соединен с первым входом тортцего элемента ИЛИ, первый

вход четвертого элемента ИЛИ соединен с выходом второго элемента ИЛИ, стробилу ющий вход первого дешифратора соединим с выходом первого элемента И рчзряднн выходы счетчика с первого по п л соедине ны с информационными входами первого дешифратора, инверсные выходы которого являются выходами увеличения задержки синхросигналов устройства, выход элемента И-НЕ соединен с информационным RVO дом второго триггера, отличающееся тем, что, с целью повышения надежнос м за счет сокращения времени коррекции чре менной диаграммы, в него введены элемемi ИЛ И-НЕ, второй дешифратор агорой тре тий и четвертый элементы KF и седьмой элемент ИЛИ, причем выход второго элемента ИЛИ соединен с синхровходом первого триггера,вторым входом треть ;го элемента ИЛИ, входом перрого элемента НЕ и стробирующим входом второго деши ь ратора, инверсные выходы которого являются выходами начала настройки синхросигналов устройства выход четрер того элемента ИЛИ соединен с первым вхо- дом первого элемента И, второй вход которого соединен с выходом пятого эле мента ИЛИ, второй вход четвертого элемен та ИЛИ соединен с инверсным дчходом первого триггера, выход элемента И НЕ со единен с третьим входом четвертого эле мента ИЛИ и первым влодом пятого элемента ИЛИ, инверсный выхо/1, триггера является выходом о1 кззч устройства, первый вход элемента I, Р1 ; - единен с инверсным выходом третьегэтииг гера, прямой выход которого соединен с первым входом шестого элемента ИЛИ RK-- ход второго элемента И гоединен с сип кров- ходом второго триггера, информационные

аход .: второго дешифратора соол мрмы г соответствующими информационными вхо дами первого дешифратора (rv 1)-и разряд ный выход счетчика соединен с первым входом седьмого элемента ИЛИ выход ко торого соединен с информационным вхо дом третьего триггера, вторым входом второго элемента ИЛИ.вторым входом пято го лемента ИЛИ. входом второго элемента НЕ и является выходом признака режима нлстройки устройства прямой выход первого триггера соединен с вторым входом элемента И-НЕ. третий вход которого соединен с входом третьего элемента НЕ и выходом пемента ИЛИ-НЕ выход второго элемента Г соединен с вторым входом шестого эле мента ИЛИ, выход которого является выходом разрешения коррекции временной диаграммы устройства выход первого элемента ИЛИ соединен с третьим входом пя того элемента ИЛИ синхрсвходом третьего триггера третьим входом шестого элемента ИЛИ и перрым входом второго элемента И, прямо второго триггера соединен с вторым входом первого элемента ИЛИ и вторым РХОДОМ седьмого элемента ИЛИ, выход третьего эпем°нта HF --оединен с четвертым вводом шестою элемента ИЛИ и является выходом ограничения гфеменного сдвига cbtvo/iHivx синхоосигнчлов устройства, выход Р рьсго ИГ соединен со счегчым входом счетчика входы элемента 1 ЛИ-НЕ явпяют -р в,идамм Огряиичения зэ- дер кисинхросипнапов устройства, вход сброса ч 0 третьргэ триггера соединен с выходом ча вэртого элемен-з НЕ вход которого соеди- ен с первым входом второго элемента ИЛИ, яылод третьего элемента ИЛИ соединен с вторым чходом второго элемента И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации памяти | 1988 |

|

SU1594516A1 |

| Устройство для управления синхронизацией памяти | 1987 |

|

SU1472893A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

| Устройство для синхронизации памяти | 1983 |

|

SU1169017A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Устройство для программного управления | 1989 |

|

SU1667005A1 |

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для подключения источника информации к магистрали | 1987 |

|

SU1481782A1 |

Изобретение относится к вычислительной технике и может быть использовано в блоках синхронизации с адаптацией времени выдачи синхронизирующих сигналов Цель изобретения - повышение надежности за счет сокращения времени коррекции временной диаграммы. Поставленная цель достигается тем, что в устройство введены дешифратор, элемент И, три элемента НЕ, элемент И-НЕ. Устройство позволяет осуществлять одновременно коррекцию задержек между всеми синхросигналами временной диаграммы 1 ил

| Авторское свидетельство СССР Nfc 1471893, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации памяти | 1988 |

|

SU1594516A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1989-07-14—Подача