Изобретение относится к автоматике и вычислительной технике и может быть использовано в сверхбыстродействующих устройствах обработки информации.

Целью изобретения является расширение области применения за счет выполнения умножения на два.

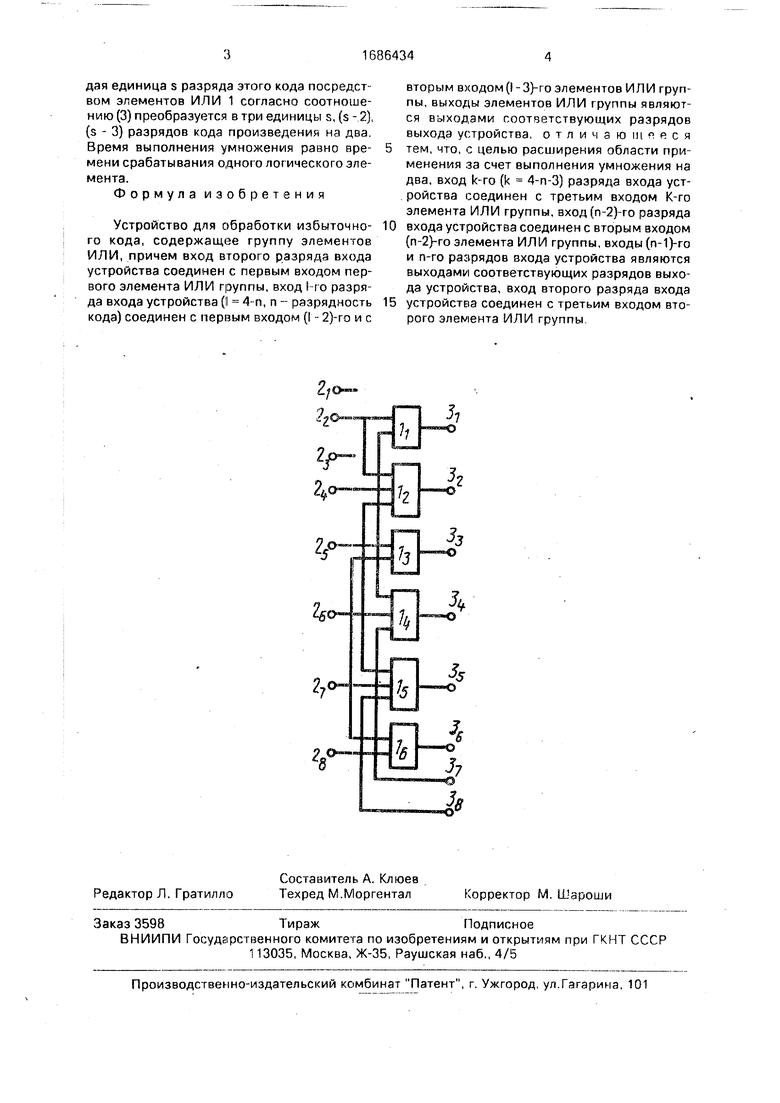

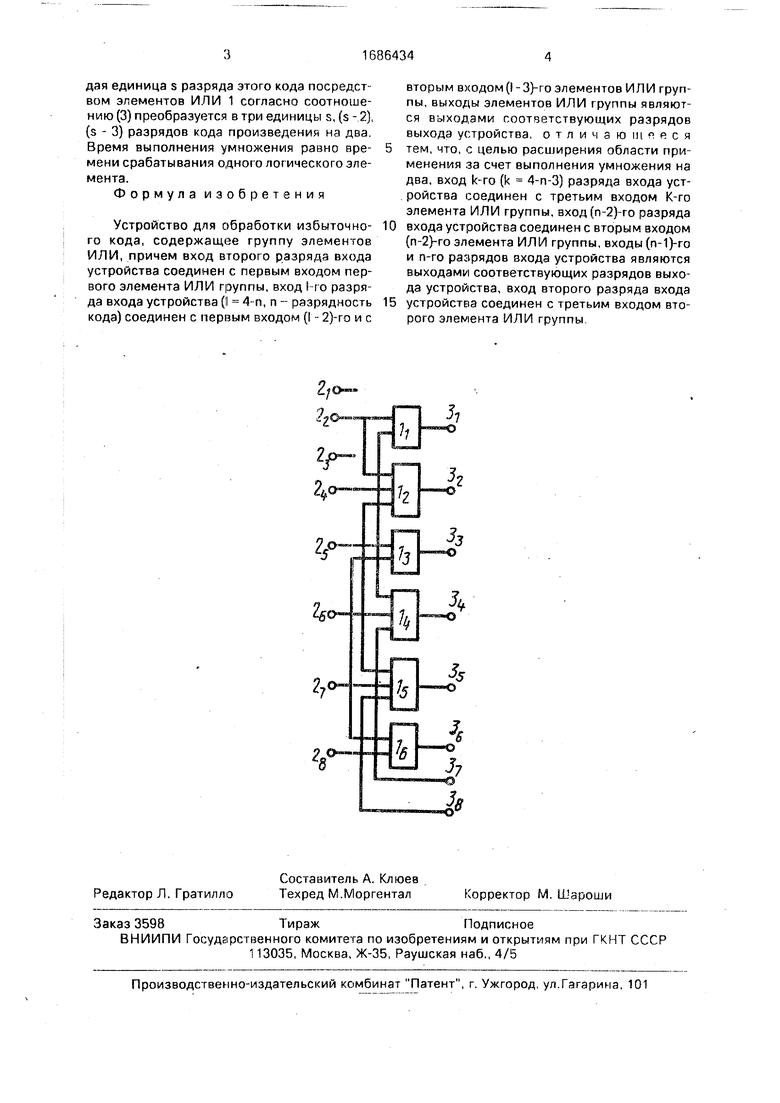

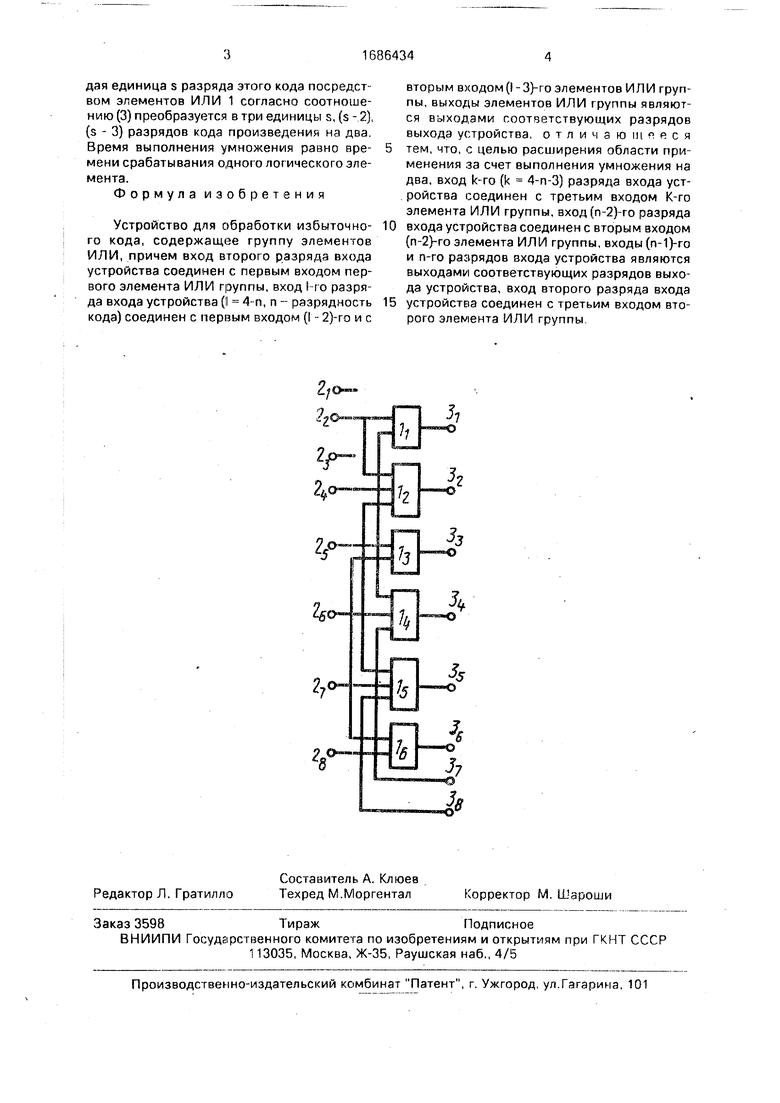

На чертеже представлена схема устройства для обработки избыточного кода (для п 8).

Устройство содержит группу элементов ИЛИ 1i-1e, входы 2i-2e разрядов входа устройства, выходы 3i-3e разрядов выхода устройства.

Устройство производит умножение на два минимальной формы (МФ) ti - системы счисления, причем значения на входах 2г2з всегда нулевые и поэтому при умножении не учитываются.

Натуральное n-разрядное число А представимо МФ в ti-системе счисления,

в виде многочлена А

-S

S-1

dsV(s)

1,(s) A

S dk V 0) V(s 1): Ч)

И 5 -И

О V (s) A

- $

voo.

dk

Ik s + 1

V(s) V(s-2) + Ц (s-3); i/4o) V0)1 (2)

Мощность МФ определяется величиной V(n+1), структура МФ: наличие в пяти соседних разрядах не более одной единицы.

Из соотношения (2) следует алгоритм умножения на два значащих цифр МФ

2 V(s) V(s) + V (s-2)+ V(s-3). (3)

Так как по условию (1) в МФ после каждой единицы разряда следует не менее четырех разрядов нулей, то перенос единицы в результате умножения на два в (s - 2) и (s - 3) разряды осуществляется без задержки.

Сущность изобретения заключается в технической реализации соотношения (3) с помощью элементов ИЛИ 1,

Устройство работает следующим образом.

При подаче на входы 2i-2s кода МФ, удовлетворяющего представлению (1), каж(Л

С

о

00

о N

СА)

N

дая единица s разряда этого кода посредством элементов ИЛИ 1 согласно соотношению (3) преобразуется в три единицы s, (s - 2), (s - 3) разрядов кода произведения на два. Время выполнения умножения равно времени срабатывания одного логического элемента.

Формула изобретения

Устройство для обработки избыточного кода, содержащее группу элементов ИЛИ, причем вход второго разряда входа устройства соединен с первым входом первого элемента ИЛИ группы, вход 1-го разряда входа устройства (I 4-n, n - разрядность кода) соединен с первым входом (I - 2)-го и с

5

вторым входом(I -3)-го элементов ИЛИ группы, выходы элементов ИЛИ группы являются выходами соответствующих разрядов выхода устройства, отличаю т°еся тем, что, с целью расширения области применения за счет выполнения умножения на два, вход k-ro (k 4-п-З) разряда входа устройства соединен с третьим входом К-го элемента ИЛИ группы. вход(п-2)-го разряда входа устройства соединен с вторым входом (п-2)-го элемента ИЛИ группы, входы (п-1)-го и п-го разрядов входа устройства являются выходами соответствующих разрядов выхода устройства, вход второго разряда входа устройства соединен с третьим входом второго элемента ИЛИ группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1989 |

|

SU1709299A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Устройство для умножения | 1988 |

|

SU1571574A1 |

| Преобразователь позиционного кода в код с большим основанием | 1987 |

|

SU1444959A1 |

| Преобразователь кодов | 1989 |

|

SU1762410A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

Изобретение относится к автоматике и вычислительной технике и можег быть использовано и в сверхбыстродействующих устройствах обработки информации. Целью изобретения является расширение области применения за счет выполнения умножения на два. Поставленная цель достигается тем, что устройство для обработки избыточного кода, содержащее группу 1 элементов ИЛИ, имеет новую организацию связей. 1 ил.

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь формы кода | 1987 |

|

SU1462491A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-23—Публикация

1989-12-25—Подача