(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для контроля сдвигателя | 1989 |

|

SU1672456A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

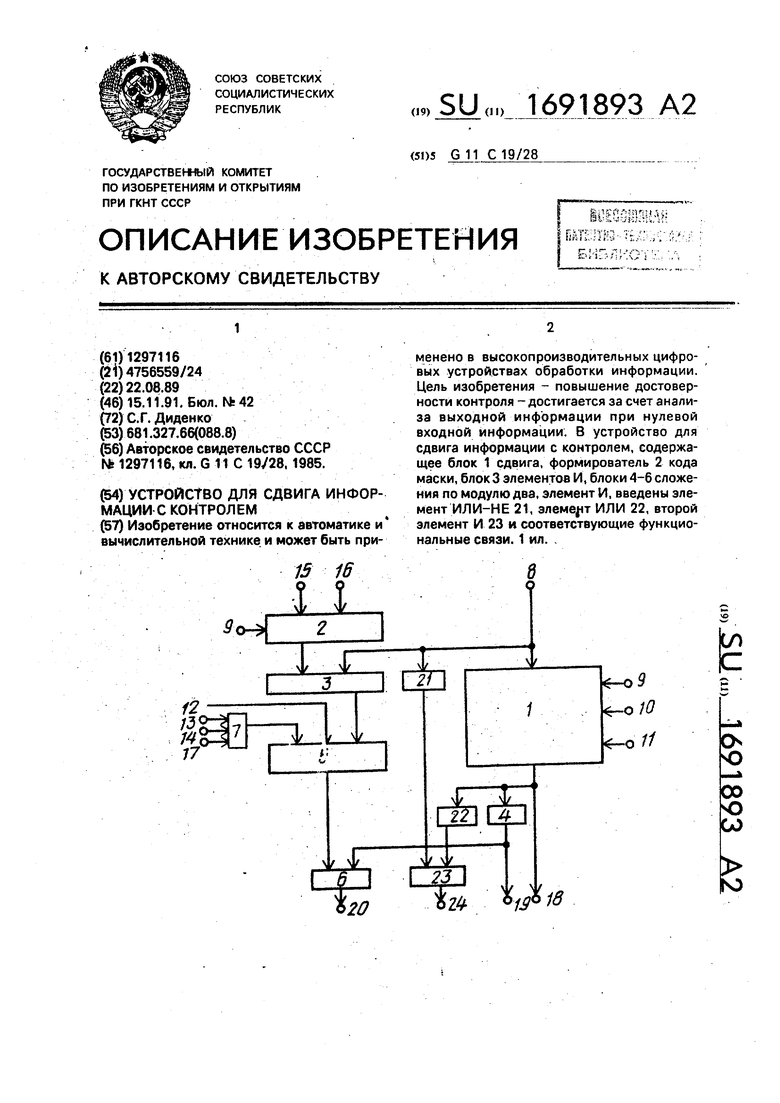

Изобретение относится к автоматике и вычислительной технике и может быть применено в высокопроизводительных цифровых устройствах обработки информации. Цель изобретения - повышение достоверности контроля - достигается за счет анализа выходной информации при нулевой входной информации. В устройство для сдвига информации с контролем, содержащее блок 1 сдвига, формирователь 2 кода маски, блок 3 элементов И, блоки 4-6 сложения по модулю два, элемент И, введены элемент ИЛИ-НЕ 21, элемент ИЛИ 22, второй элемент И 23 и соответствующие функциональные связи.1 ил.

$ #

Изобретение относится к автоматике и вычислительной технике, может быть применено в высокопроизводительных цифро4 иых устройствах обработки информации и касается усовершенствования устройства по авт. св. № 1297116.

На черте се приведена схема устройства.

Устройство содержит блок 1 сдвига формирователь2 кода масюя, блокЗ элементов И, первый, второй и третий блоки 4-6 сложения по модулю дв&, первый элемент Vi 7, вход 8 данных устройства, вход 9 количества сдвигов устройства, вход 10 направления сдвига устройства, вход 11 вида сдвига устройства, вход 12 контрольных разрядов устройства, старший разряд 13 данных устройства, младший разряд 14 количества сдвигов устройства, первым, второй и третий управляющие входы 15-17 устройства соответственно, выход 18 данных устройства, выход 19 дантрольннх разрядов устройства, первый выход 20 ошибки устройства, элемент ИЛИ-НЕ 21, элемент ИЛИ 22, второй элемент 1/1 23 и второй выход 24 ошибки устройства.

Первый управляющей вход формирователя 2 кода маски и первый управляющий вход с двигателя являются входом 9 количества сдвигов устройства, второй и третий управляющие входы формирователя 2 кода маски являются первым и вторым управляющими входами 15 и 16 устройства соответственно, выход .формирователя 2 кода маски соединен с первым входом блока 3 элементов И, второй вход которого соединен с информационным входом блока 1 сдвига, второй и третий управляющие входы блока 1 сдвига являются входами 10 и 11 направления и типа сдвига устройства соответственно, группа выходов блока 1 сдвига соединена с группой входов первого блока 4 сложения по модулю два и является выходом 18 данных устройства, группа выходов первого блока 4 сложения по модулю два соединена с первым входом третьего блока 6 сложения по модулю два и с оыходом 1Э контрольных разрядов устройства, вход 12 контрольных разрядов устройства соединен с первь л входом второго блока 5 сложения по модулю два, второй вход которого соединен с выходом блока 3 элементов И, а третий вход соединен с выходом первого элемента Л 7, первый вход 13 первого элемента И 7 является старшим разрядом входных данных устройства, второй вход 14 первого элемента И 7 является младшим разрядом числа сдвигов устройства, третий вход 17 первого элемента И 7 соединен с третьим управляющим входом 17 устройства, выход блока 5 сложения по модулю два соединен с вторым входом блока 6 сложения по модулю два, выход которого является первым выходом 20 ошибки устройства,

группа входов элемента ИЛИ 22 соединена с группой выходов блока 1 сдвига, выход элемента ИЛИ 22 соединен с вторым входом второго элемента И 23, выход которого является вторым выходом 24 ошибки устрой0 ства, первый вход второго элемента И 23 соединен с выходом элемента ИЛИ-НЕ, группа выходов которого соединена с информационным входом блока сдвига.

Устройство работает следующим обра5 зом.

На вход 8 данных устройства и вход блока сдвига поступает информация для выполнения в блоке сдвига логического, арифметического или циклического вида

0 сдвигов. На входы 9, 10, 11 устройства поступают сигналы, настраивающие блок сдвига на выполнение определенного количества сдвигов вправо или влево и вид сдвигов соответственно, Аналогичные сигналы

5 поступают на входы формирователя кода маски. По значению количества сдвигов на входе 9 устройства и по значению управляющих сигналов на входах 15 и 1 б устройства на выходе формирователя 2 образуется со0 ответствующий код, который далее в блоке 3 поразрядно логически перемножается с двоичным кодом входной информации блока 1 сдвига. В результате этого на выход блока 3 поступают только те разряды вход5 ной информации блока 1 сдвига, которые должны быть выдвинуты в результате выполнения в устройстве операции сдвига. При сдвиге на нуль разрядов, а также при циклическом сдвиге все разряды входной

0 информации устройства сохраняются, поэтому на выходе формирователь 2 кода маски, а следовательно, и на выходе блока 3 элементов И должен сформироваться двоичный код, состоящий из одних нулей. i

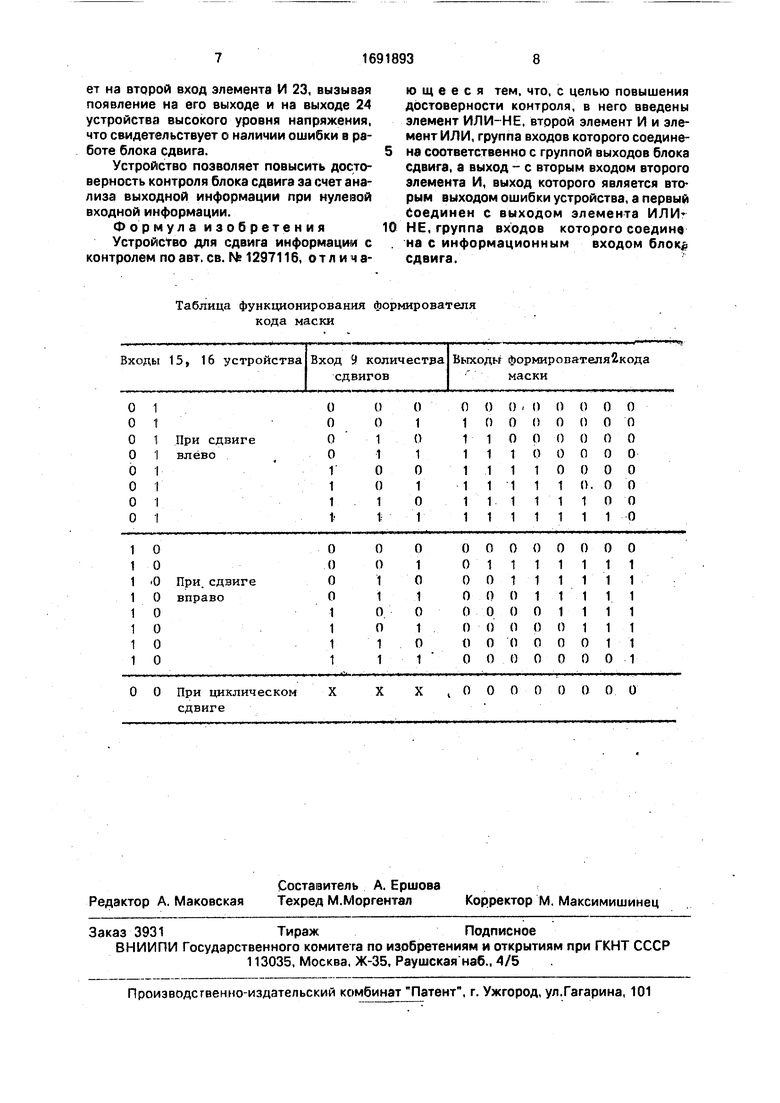

5 Формирователь 2 кода маски может быть реализован на ПЗУ по соответствующей таблице истинности. В этом случае входы 9, 15 и 16 устройства образуют адресный аход этого ПЗУ. Ниже приведена таблица,

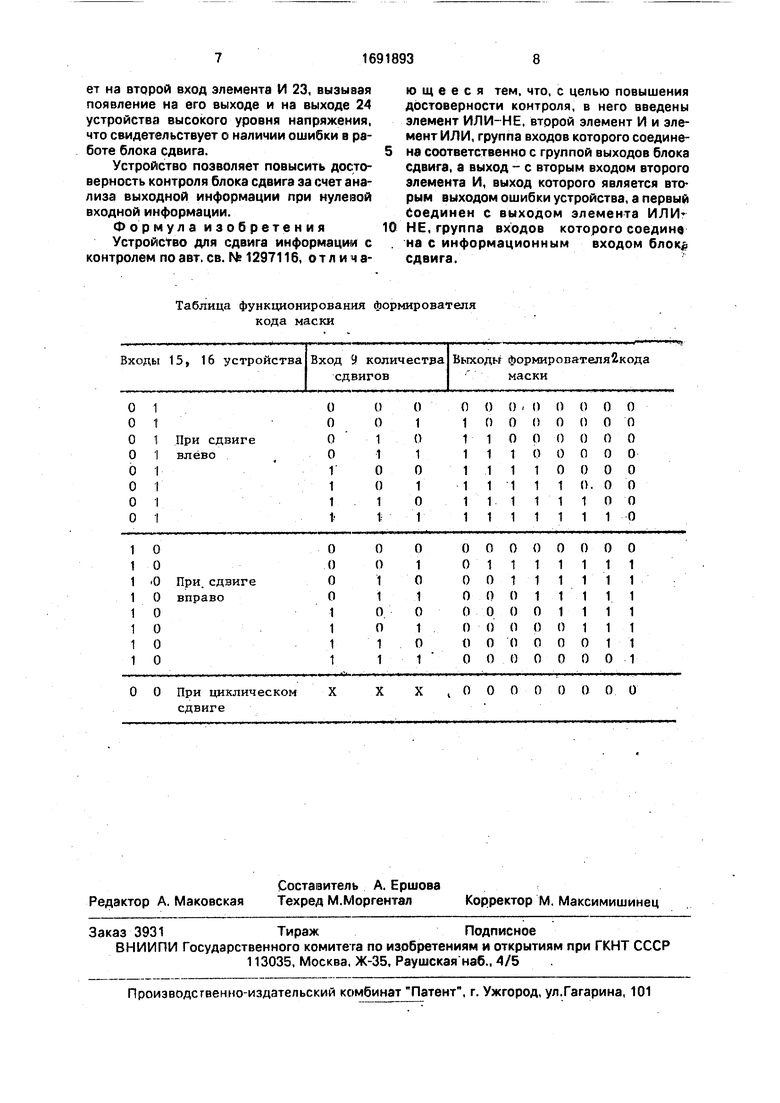

0 поясняющая функционирование формирователя 2 кода маски для случая . При этом предполагается, что при сдвиге влево на вход 9 устройства подается прямой код количества сдвигов, а при сдвиге вправо 5 дополнительный.

В блоке 5 осуществляется сложение по модулю два двух групп слагаемых. Первую группу слагаемых образуют разряды (четности), относящиеся к определенным группам разрядов (например, к байтам) входной информации устройства. Эта группа слагаемых подается на первый вход блока 5 с входа 12 устройства. Вторую группу слагаемых образуют значения выходов блока 3 элементов И (на эти выходы поступают значения тех разрядов входной информации устройства, которые должны быть выдвинуты в процессе выполнения в нем операции сдвига}. Вторая группа слагаемых подается на второй вход блока 5 с выхода блока 3 элементов. На третий вход блока S с зыхода первого элемента И 7 подается сигнал, учитывающий четность вдвигаемых единиц при выполнении в устройстве арифметического сдвига вправо. Этот сигнал равен единице только в том случае, когда в устройстве выполняется арифметический сдвиг вправо на нечетное число разрядов отрицательного числа (в этом случае на входах 13, 14 и 17 устройства присутствуют единичные сигналы), на выходе блока 5 образуется значение предсказываемой четности результата.

С помощью первого блока 4 сложения по модулю два осуществляется формирование фактических четностей для групп рэзря- дов (например, байтов) выходной информации блока 1 сдвига. Значения этих четностей подаются на выход 19 устройства в качестве контрольных разрядов результата. Эти же четности поступают в третий блок 6, где суммируются по модулю два между собой и со значением предсказанной четности результата и где проверяется их равенство. Когда значения фактической и поедсказанной четностей результата не совпадают, на выходе 20 устройства формируется сигнал ошибки.

Ниже приводится пример сдвига в устройстве байта информации А а132333435363738 с одним контрольным разрядом К, дополняющим ее до четности.

Пусть в устройстве необходимо выполнить арифметический сдвиг контролем информации А 31Э2аз34а5асЬ Зг на тр и разряда вправо в предположен что старший разряд 31 знаковый и .Для этого на вход 8 данных устройства подается значение A ai3233a ia5a6a7a8, на вход 2 контрольных разрядов устройства - значение контрольного разряда К, на вход 9 количества сдвигов - двоичный код 101, являющийся дополнением кода 011, на входы 10, 11 устройствэ поступают сигналы, настраивающие блок 1 на выполнение в нем арифметического сдвига вправо, на первый и второй управляющие входы 15 и 16 устройства подается код 10, настраивающий формирователь 2 на получение кода маски для сдвига информации вправо, на третий

КфН

управляющий вход 17 устройства подается сигнал логической единицы.

В результате этого на выходе блока 1 сдвига формируется значение

А1- Ша1Э23зэ4а5. которое и поступает на выход 1 а устройства в качестве его результата. Значение А1 используется в первом блоке 4 сложения по модулю два для формирования в соответствии с выражением Э I ©I ©31 ©32Фзз®34®а5 фактической четности результата Кф (знэчение Кф в качестве контрольного разряда результата подается на выход 19 устройствэ). На выходе формирователя 2 образуется код маски

5 00000111, а на выходе блока 3 элементов И формируется результат ОООООаеатэв, который равен значению группы выдвигаемых разрядов в исходной информации А. С помощью второго блока 5 сложения по модулю

0 два формируется значение предсказываемой четности результата Кп КФае©атФа8©1, где 1 отражает четность вдвигаемых при сдвиге вправо единиц (единица формируется на выходе первого элемента И 7). В третьем

5 блоке 6 сложения по модулю два осуществляется сравнение значения фактической четности Кф результата со значением предсказываемой четности Кп результата, нз основании чего на выходе 20 устройства вырабатывается или не

0 вырабатывается сигнзл ошибки.

Подобным обрззом может быть рассмотрена работа устройства и для тех случаев, когда информация, поступающая на вход 8 данных устройства, сопровождается не5 сколькими контрольными разрядами (например, каждый байт входной информации сопровождается своим контрольным разрядом).

Если на вход 8 данных устройства поступает для сдвига нулевая информация, то на

0 выходе элемента ИЛ1Л-НЕ21, выполняющего функцию дешифратора нулевого кода, появляется высокий уровень напряжения, который поступает нз первый вход второго элемента И 23. Если блок сдвига работает

5 правильно, то на его группе выходов (вне зависимости от сигналов на входах 9-11 устройства) появляется нулевая информзция, которая поступает на группу входов элемента ИЛИ 22, На выходе элемента ИЛИ 22

0 появляется низкий уровень напряжения, который поступает на второй вход элемента И 23, вызывая появление на его выходе и на выходе 24 устройства низкого уровня напряжения, что свидетельствует об отсутствии

5 сигнала ошибки, Если же блок сдвига работает неправильно и на его группе выходов появляется ненулевая информация в одном или нескольких разрядах, в этом случае на выходе элемента ИЛИ 22 появлчется высокий уровень напряжения, который поступает на второй вход элемента И 23, вызывая появление на его выходе и на выходе 24 устройства высокого уровня напряжения, что свидетельствует о наличии ошибки в работе блока сдвига.

Устройство позволяет повысить достоверность контроля блока сдвига за счет анализа выходной информации при нулевой входной информации.

Формула изобретения Устройство для сдвига информации с контролем по авт. св. № 1297116, отличаТаблица функционирования формирователя кода маски

О 0 При циклическом сдвиге

ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены элемент ИЛИ-НЕ, второй элемент И и элемент ИЛ И, группа входов которого соединена соответственно с группой выходов блока сдвига, а выход - с вторым входом второго элемента И, выход которого является вторым выходом ошибки устройства, а первый соединен с выходом элемента ИЛИ НЕ,группа входов которого соедине на с информационным входом блок сдвига.

00000000

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-15—Публикация

1989-08-22—Подача