Изобретение относится к автоматике и вычислительной технике и может быть применено в высокопроизводительных цифровых устройствах обработки информации.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения в нем, наряду с логическим, арифметического и циклического сди гов с контролем, а также упрощение устройства за счет организации в нем автономного контроля по четности, не требующего введения дополнительных связей с блоком сдвига.

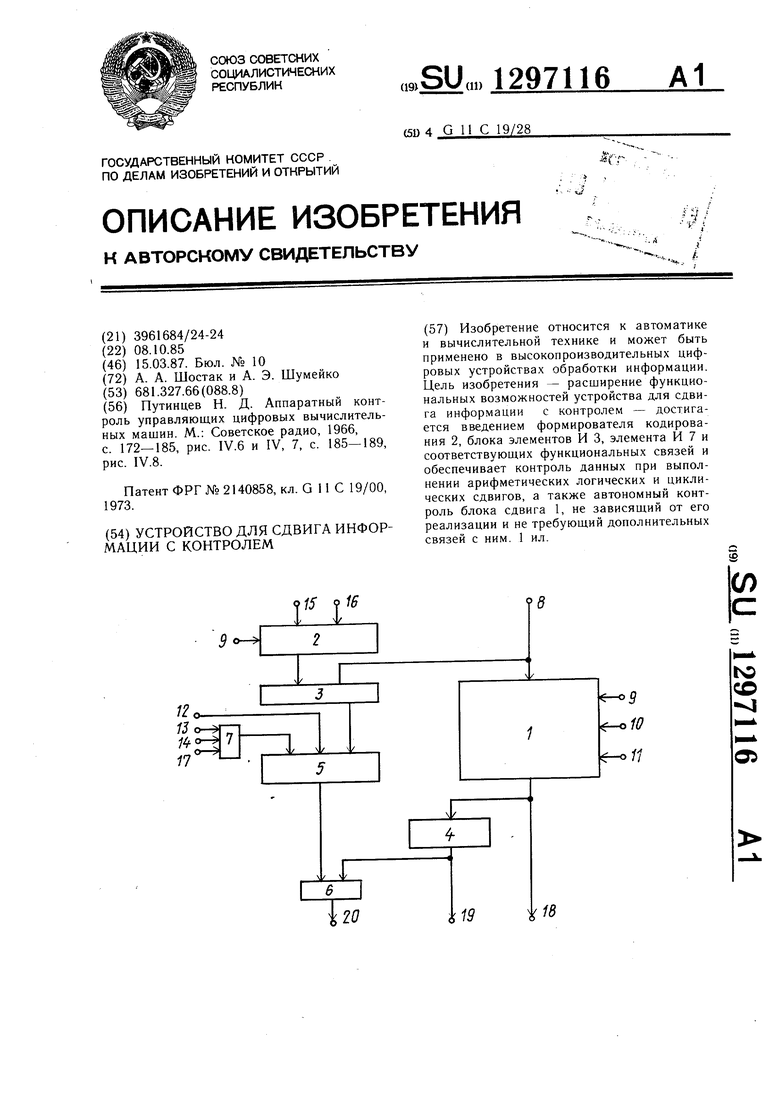

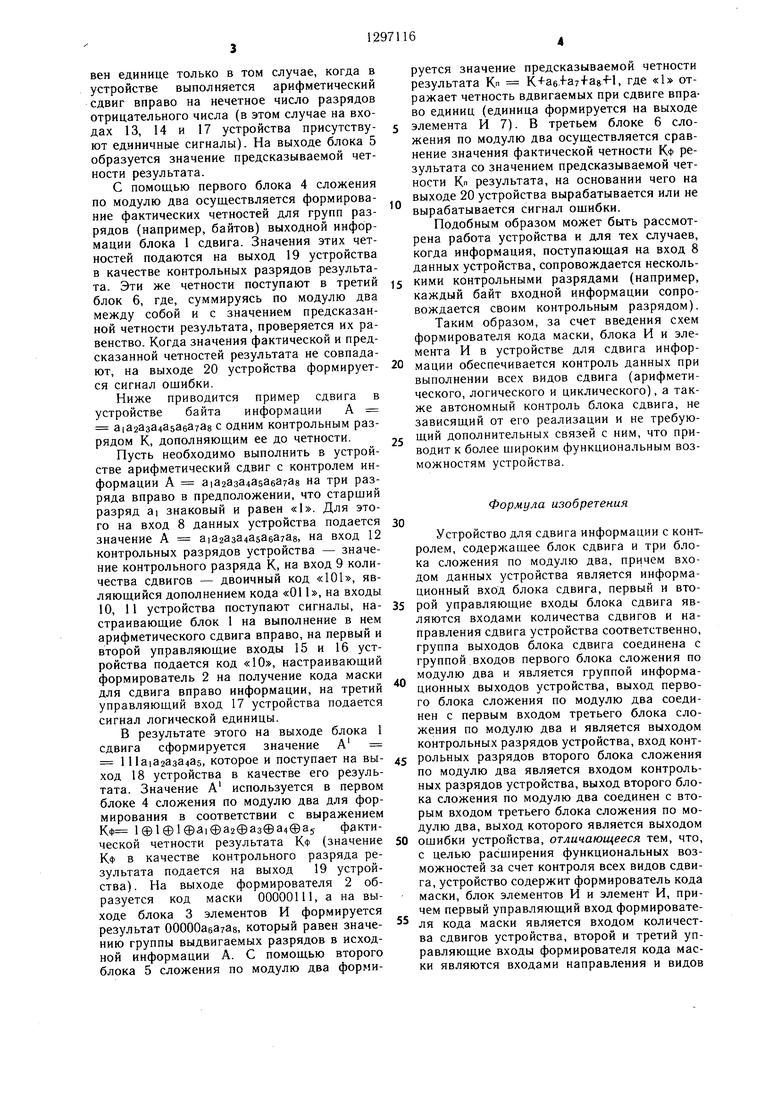

На чертеже приведена схема устройства для сдвига информации с контролем.

Устройство содержит блок 1 сдвига, формирователь 2 кода маски, блок 3 элементов И, первый, второй и третий блоки 4, 5 и 6 сложения по модулю два соответственно, элемент И 7, вход 8 данных устройства, вход 9 количества сдвигов устройства, вход 10 направления сдвига устройства, вход 11 вида сдвига устройства, вход 12 контрольных разрядов устройства, старший разряд 13 данных устройства, младщий разряд 14 количества сдвигов устройства, первый, второй и третий управляющие входы 15-17 устройства соответственно, выход 18 данных устройства, выход 19 контрольных разрядов устройства и выход 20 ошибки устройства.

Первый управляющий вход формирователя кода маски 2 и первый управляющий вход сдвигателя являются входом 9 количества сдвигов устройства, второй и третий управляющие входы формирователя кода маски 2 являются первыми и вторым управляющими входами 15 и 16 устройства соответственно, выход формирователя 2 кода маски соединен с первым входом блока 3 элементов И, второй вход которого соединен с информационным входом блока 1 сдвига, второй и третий управляющие входы блока 1 сдвига являются входами 10 и I 1 направления и типа сдвига устройства соответственно, группа выходов блока 1 сдвига соединена с группой входов первого блока 4 сложения по модулю два и является выходом 18 данных устройства, группа выходов первого блока 4 сложения по модулю два соединена с первым входом третьего блока 6 сложения по модулю два и с выходом 19 контрольных разрядов устройства, вход 12 контрольных разрядов устройства соединен с первым входом второго блока 5 сложения по модулю два, второй вход которого соединен с выходом блока 3 элементов И, а третий вход соединен с выходом элемента И 7, первый вход 13 элемента И 7 является старшим разрядом входных данных устройства, второй вход 14 элемента И 7 является младщим разрядом числа сдвигов устройства, третий вход 17 элемента И 7 соединен с третьим управляющим входом 17 устройства, выход блока 5 сложения по модулю два соединен со вторым

0

входом блока 6 сложения по модулю два, выход которого является выходом 20 ошибки устройства.

Устройство работает следующим образом. На вход данных 8 устройства и вход блока сдвига поступает информация для выполнения в блоке сдига логического, арифметического или циклического видов сдвигов. На входы 9-11 устройства поступают сигналы, настраивающие блок сдвигов на выполнение определенного количества сдвигов вправо или влево и вид сдвигов соответственно. Аналогичные сигналы поступают на входы формирователя кода маски. По значению количества сдвигов на вход 9 уст ройства и по значению управляющих сигналов на входах 15 и 16 устройства на выходе формирователя 2 образуется соответствующий маскирующий код, который далее в блоке 3 поразрядно логически перемножается с двоичным кодом входной информа0 ции блока 1 сдвига. В результате этого на выход блока 3 поступают только те разряды входной информации блока 1 сдвига, которые должны быть выдвинуты в результате выполнения в устройстве операции сдвига. При сдвиге на ноль разрядов, а также при циклическом сдвиге, все разряды входной информации устройства сохраняются, а поэтому на выходе формирователя 2 кода маски, а следовательно, и на выходе блока 3 элементов И должен сформироватьQ ся двоичный код, состоящий из одних нулей.

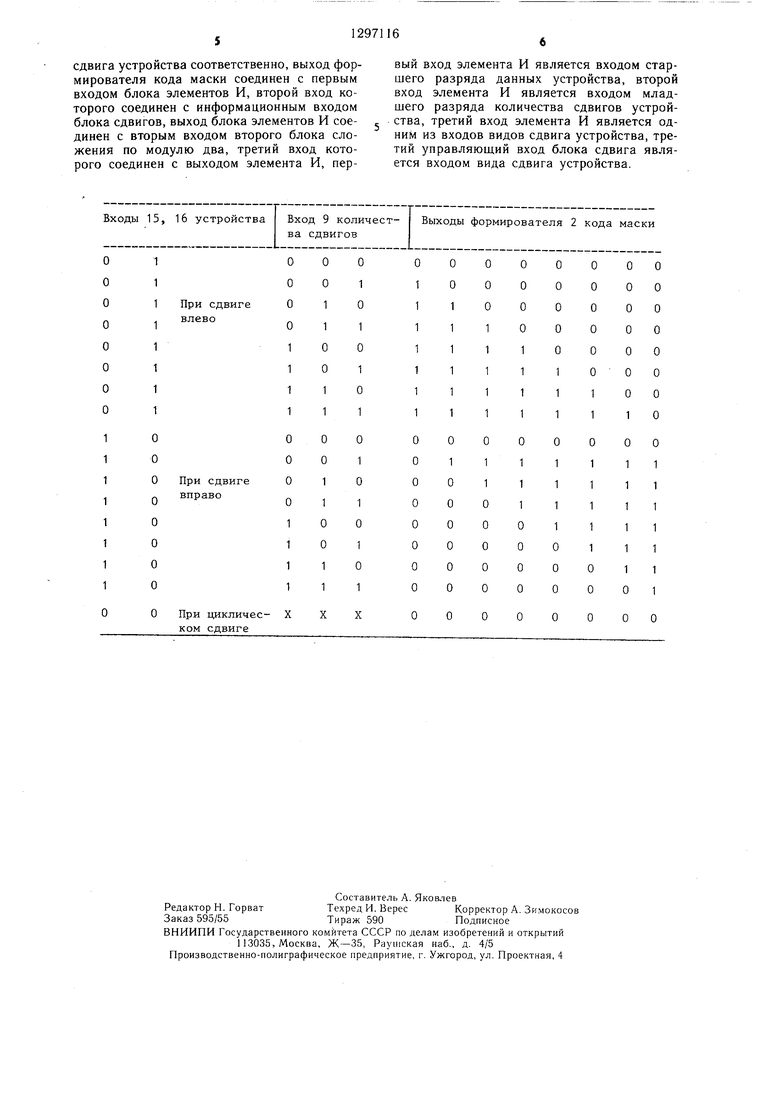

Формирователь 2 кода маски может быть реализован на ПЗУ по соответствующей таблице истинности. В этом случае входы 9, 15 и 16 устройства образуют адресный вход этого ПЗУ. Ниже приведена таблица, поясняющая функционирование формирователя 2 кода маски для случая п 8. При этом предполагается, что при сдвиге влево на вход 9 устройства подается прямой код количества сдвигов, а при сдвиге вправо - дополнительный.

В блоке 5 осуществляется сложение по модулю два двух групп слагаемых. Первую группу слагаемых образуют разряды (четности), относящиеся к определенным группам разрядов (например, к байтам) входной информации устройства. Эта группа слагаемых подается на первый вход блока 5 с входа 12 устройства. Вторую группу слагаемых образуют значения выходов блока 3 элементов И (на эти выходы поступают

0 значения тех разрядов входной информации устройства, которые должны быть выдвинуты в процессе выполнения в нем операции сдвига). Вторая группа слагаемых подается на второй вхд блока 5 с выхода блока 3 элементов И. На третий вход бло5 ка 5 с выхода элемента И 7 подается сигнал, учитывающий четность вдвигаемых единиц при выполнении в устройстве арифметического сдвига вправо. Этот сигнал равен единице только в том случае, когда в устройстве выполняется арифметический сдвиг вправо на нечетное число разрядов отрицательного числа (в этом случае на входах 13, 14 и 17 устройства присутствуют единичные сигналы). На выходе блока 5 образуется значение предсказываемой четности результата.

С помощью первого блока 4 сложения по модулю два осуществляется формирование фактических четностей для групп разрядов (например, байтов) выходной информации блока 1 сдвига. Значения этих четностей подаются на выход 19 устройства в качестве контрольных разрядов результата. Эти же четности поступают в третий блок 6, где, суммируясь по модулю два между собой и с значением предсказанной четности результата, проверяется их равенство. Когда значения фактической и предсказанной четностей результата не совпадают, на выходе 20 устройства формируется сигнал ошибки.

Ниже приводится пример сдвига в устройстве байта информации А а|а2аза4а5аба7а8 с одним контрольным разрядом К, дополняющим ее до четности.

Пусть необходимо выполнить в устройстве арифметический сдвиг с контролем информации А а1а2аза4а5аба7а8 на три разряда вправо в предположении, что старший разряд ai знаковый и равен «1. Для этого на вход 8 данных устройства подается значение А а1а2аза4а5аба7а8, на вход 12 контрольных разрядов устройства - значение контрольного разряда К, на вход 9 количества сдвигов - двоичный код «101, являющийся дополнением кода «011, на входы 10, 11 устройства поступают сигналы, настраивающие блок 1 на выполнение в нем арифметического сдвига вправо, на первый и второй управляющие входы 15 и 16 устройства подается код «10, настраивающий формирователь 2 на получение кода маски для сдвига вправо информации, на третий управляющий вход 17 устройства подается сигнал логической единицы.

В результате этого на выходе блока 1 сдвига сформируется значение А 111а1а2аза4а5, которое и поступает на выход 18 устройства в качестве его результата. Значение А используется в первом блоке 4 сложения по модулю два для формирования в соответствии с выражением КФ 1®1©1@а1®а2®аз®а4®а5 фактической четности результата Кф (значение Кф в качестве контрольного разряда результата подается на выход 19 устройства). На выходе формирователя 2 образуется код маски 00000111, а на выходе блока 3 элементов И формируется результат OOOOOaearag, который равен значению группы выдвигаемых разрядов в исходной информации А. С помощью второго блока 5 сложения по модулю два форми0

руется значение предсказываемой четности результата Кп K-f-ae-far-fag-f-l, где «1 отражает четность вдвигаемых при сдвиге вправо единиц (единица формируется на выходе элемента И 7). В третьем блоке 6 сложения по модулю два осуществляется сравнение значения фактической четности Кф результата со значением предсказываемой четности Кп результата, на основании чего на выходе 20 устройства вырабатывается или не вырабатывается сигнал ошибки.

Подобным образом может быть рассмотрена работа устройства и для тех случаев, когда информация, поступающая на вход 8 данных устройства, сопровождается несколь5 кими контрольными разрядами (например, каждый байт входной информации сопровождается своим контрольным разрядом). Таким образом, за счет введения схем формирователя кода маски, блока И и элемента И в устройстве для сдвига инфор0 мации обеспечивается контроль данных при выполнении всех видов сдвига (арифметического, логического и циклического), а также автономный контроль блока сдвига, не зависящий от его реализации и не требую5 Щий дополнительных связей с ним, что приводит к более широким функциональным возможностям устройства.

Формула изобретения

0

0

Устройство для сдвига информации с контролем, содержащее блок сдвига и три блока сложения по модулю два, причем входом данных устройства является информационный вход блока сдвига, первый и вто5 рой управляющие входы блока сдвига являются входами количества сдвигов и направления сдвига устройства соответственно, группа выходов блока сдвига соединена с группой входов первого блока сложения по модулю два и является группой информационных выходов устройства, выход первого блока сложения по модулю два соединен с первым входом третьего блока сложения по модулю два и является выходом контрольных разрядов устройства, вход конт5 рольных разрядов второго блока сложения по модулю два является входом контрольных разрядов устройства, выход второго блока сложения по модулю два соединен с вторым входом третьего блока сложения по модулю два, выход которого является выходом

0 ошибки устройства, отличающееся тем, что, с целью расщирения функциональных возможностей за счет контроля всех видов сдвига, устройство содержит формирователь кода маски, блок элементов И и элемент И, причем первый управляющий вход формирователя кода маски является входом количества сдвигов устройства, второй и третий управляющие входы формирователя кода маски являются входами направления и видов

5

сдвига устройства соответственно, выход формирователя кода маски соединен с первым входом блока элементов И, второй вход которого соединен с информационным входом блока сдвигов, выход блока элементов И соединен с вторым входом второго блока сложения по модулю два, третий вход которого соединен с выходом элемента И, первый вход элемента И является входом старшего разряда данных устройства, второй вход элемента И является входом младшего разряда количества сдвигов устройства, третий вход элемента И является одним из входов видов сдвига устройства, третий управляющий вход блока сдвига является входом вида сдвига устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для сдвига информации с контролем | 1989 |

|

SU1691893A2 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

Изобретение относится к автоматике и вычислительной технике и может быть применено в высокопроизводительных цифровых устройствах обработки информации. Цель изобретения - расширение функциональных возможностей устройства для сдвига информации с контролем - достигается введением формирователя кодирования 2, блока элементов И 3, элемента И 7 и соответствующих функциональных связей и обеспечивает контроль данных при выполнении арифметических логических и циклических сдвигов, а также автономный контроль блока сдвига 1, не зависящий от его реализации и не требующий дополнительных связей с ним. 1 ил. 8 (Л 05 1В

| Путинцев Н | |||

| Д | |||

| Аппаратный контроль управляющих цифровых вычислительных машин | |||

| М.: Советское радио, 1966, с | |||

| Приспособление для воспроизведения изображения на светочувствительной фильме при посредстве промежуточного клише в способе фотоэлектрической передачи изображений на расстояние | 1920 |

|

SU172A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| БОКОВАЯ ЧАСТЬ КУЗОВА АВТОМОБИЛЯ | 1998 |

|

RU2140858C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-08—Подача