«

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля дискретных объектов | 1987 |

|

SU1539781A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1667073A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

Изобретение относится к автоматике У вычислительной технике и может быть чс- пользов «о в автоматизированных системах для контроля и диагностики цифровых блоков s процессе их производства и эксплуатации. Целью изобретения является расширение области применения за счет обеспечение функционального кек-ог -« цифровых блоков с йэунапривлеки ;- f - . С этой цб-Еь г 1 устройетэр со -« щее блок задания тестов и анализа . генератор импульсов, блок регистров программируемых временных интервалов, коммутатор и группу элементов ИЛИ. введены счетчик и три блока памяти. 4 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах контроля для контроля и диагностики цифровых блоков в процессе их производства и эксплуатации.

Целью изобретения является расширение области применения за счет обеспечения функционального контроля цифровых блоков с двунаправленные обменом.

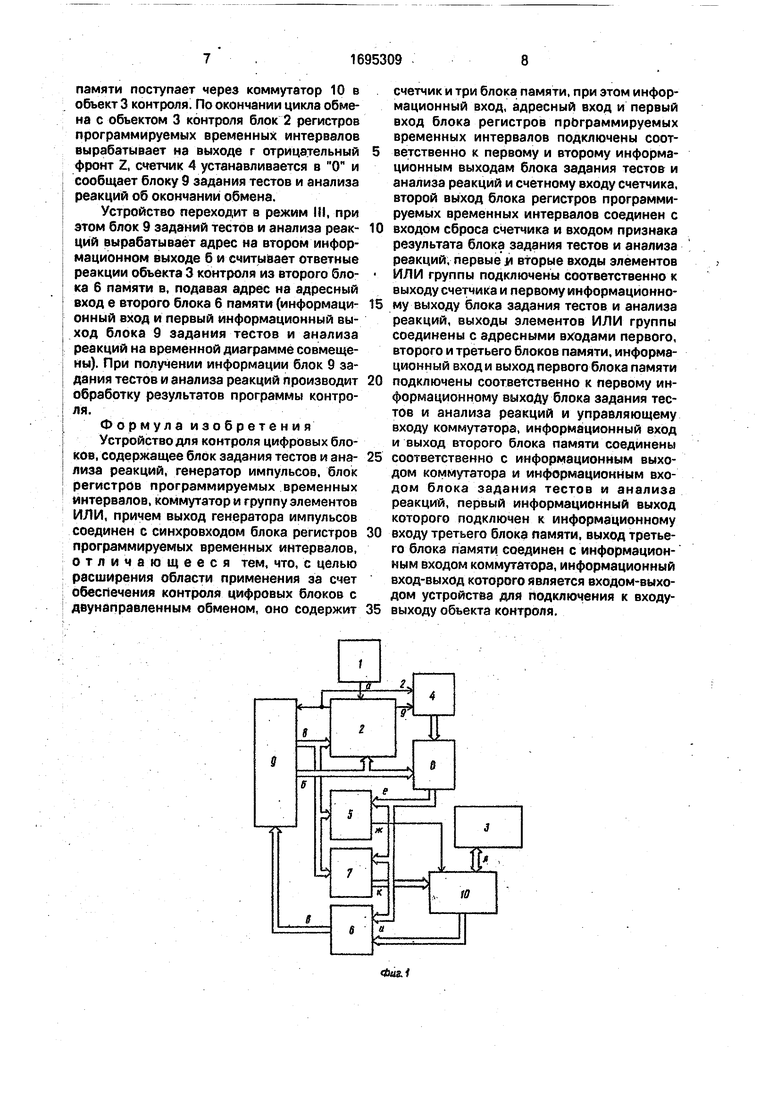

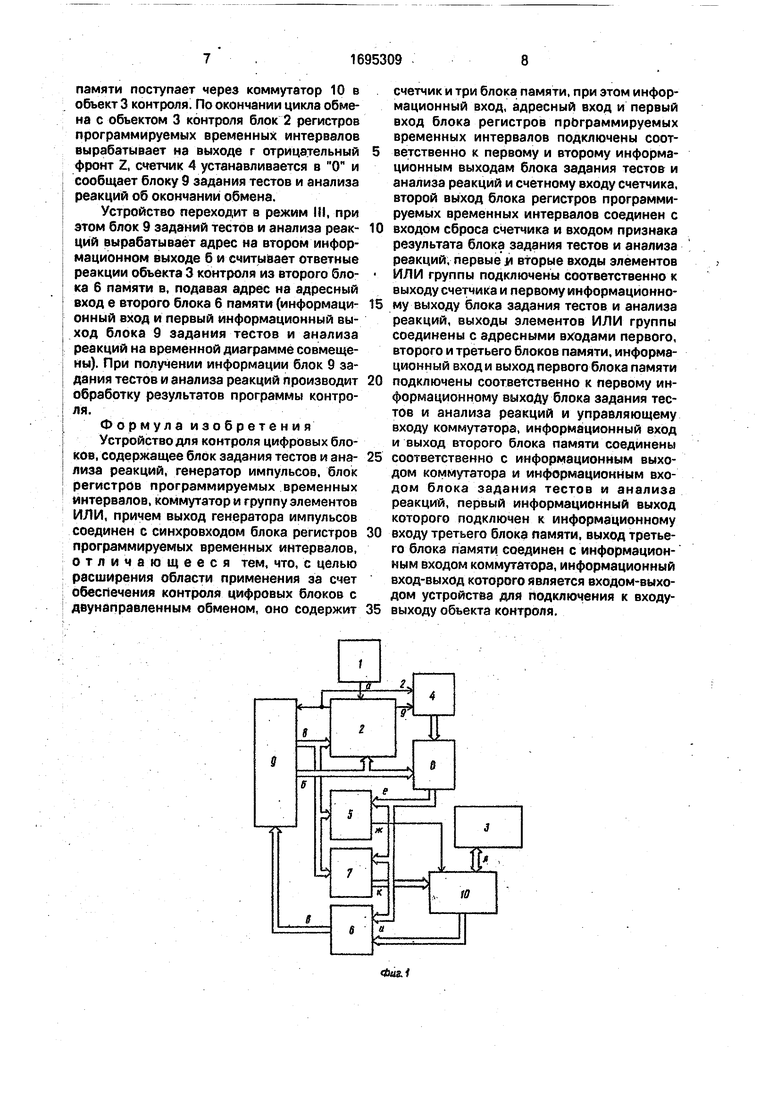

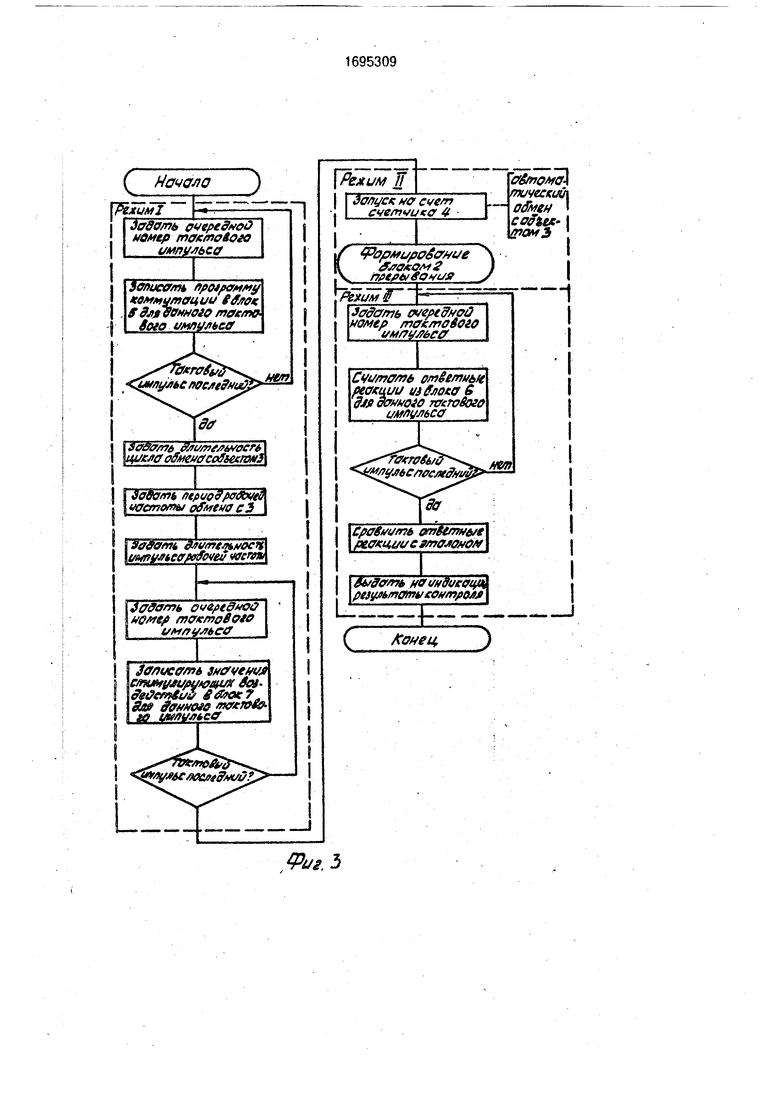

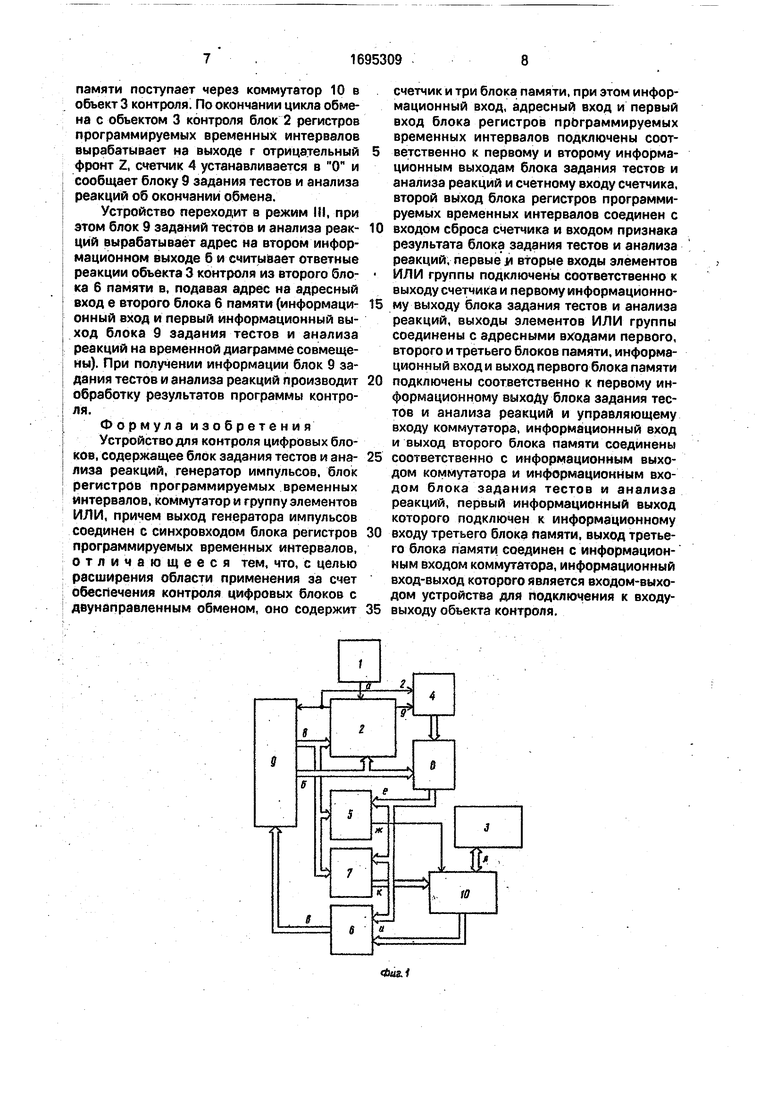

На фиг.1 представлена функциональная схеиа устройства для контроля цифровых блоков; на фиг.2 - функциональная схема блока регистров программируемых временных интервалов; на фиг.З - блок-схема алгоритма работы устройства для контроля цифровых блоков; на фиг.4 - временные диаграммы работы устройства для контроля цифровых блоков.

Устройство для контроля цифровых бло- scoa (фиг. 1) содержит генератор 1 импульсов

для выработки тактовых импульсов максимальной частоты, блок 2 регистров программируемых временных интервалов для программного задания частоты и длительности импульсов рабочей частоты, а также длительности временного интервала и сигнала окончания операции обмена информацией с объектом 3 контроля, счетчик 4 для задания адреса, поступающего на адресный . вход первого, второго и третьего блоков 5 памяти, группу 8 элементов ИЛИ, 3 задания тестов и анализа резкциг -н уп, равления программой контроля и коммутатор 10, предназначенный для программного подключения контактов объекта 3 контроля к второму блоку 6 памяти для приема ответных реакций и третьему блоку 7 памяти выдачи стимулирующих воздействий.

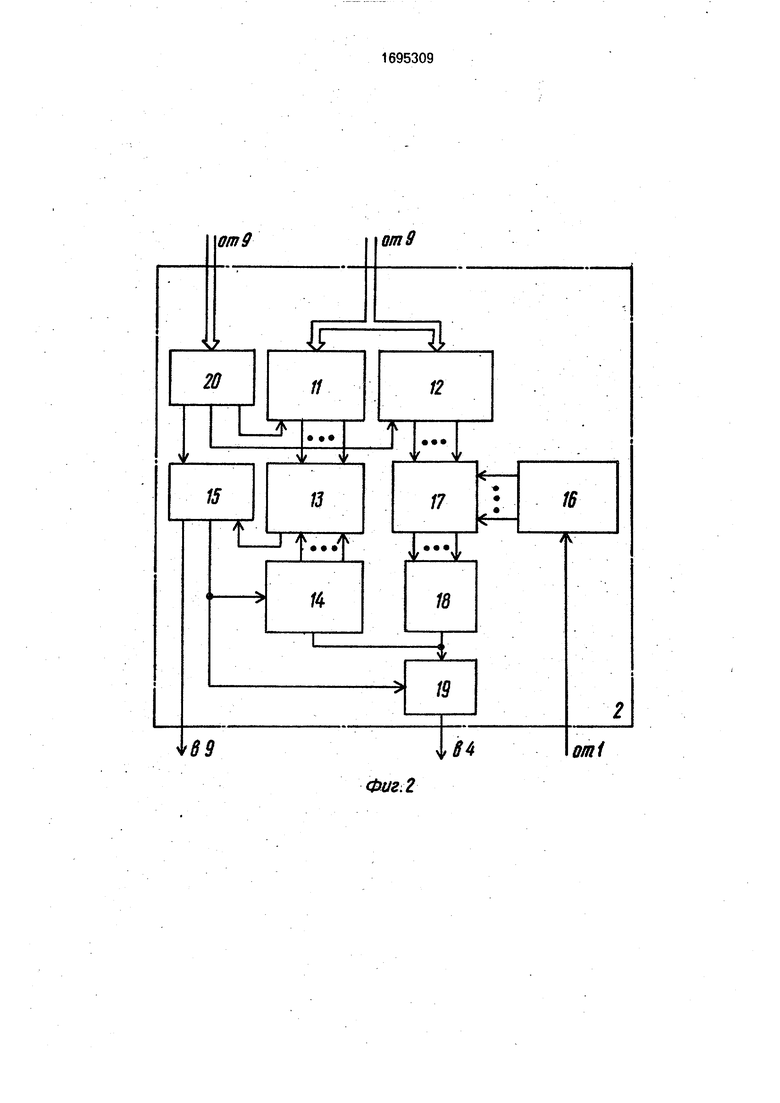

Блок 2 регистров программирую временных интервалов (фиг 2) содержит регистр 11 кода временного г чт-овала гч

s

(Л 00

о о

записи длительности интервала времени цикла обмена информацией с объектом 3 контроля, регистр 12 кода длительности импульса для задания параметров рабочей частоты, блок 13 поразрядного сравнения для сравнения регистра 11 и суммирующего счетчика 14, RS-триггер 15 для управления запуском счетчика и для выработки строба длительности цикла обмена, формирователь 16 сетки импульсов, группу 17 элементов И и элемент ИЛИ 18, предназначенные для выработки рабочей частоты, элемент И 19, а также дешифратор 20 для выработки управляющих сигналов в регистры 11 и 12 и RS-триггер 15.

Блок 13 поразрядного сравнения сравнивает попарно значения сигнала на выходе суммирующего счетчика 14 и сигнала на соответствующем выходе регистра 11 кода временного интервала. При равенстве значений сигналов во всех парах блок 13 вырабатывает сигнал 1.

Формирователь 16 сетки импульсов представляет собой делитель частоты, входная частота которого делится на первом выходе в 2 раза, на втором в 4 раз, на п-м выходе - в 2П раза.

Коммутатор 10 представляет собой блок, предназначенный доя приема и выдачи сигналов по двусторонним каналам. Каждый вход-выход работает на прием или выдачу в зависимости от значения сигнала на соответствующем контакте управляющего входа коммутатора.

Первый 5, второй 6 и третий 7 блоки памяти представляют собой запоминающее устройство статического типа, информация на выходе которого появляется после подачи адреса на его вход и сохраняется на выходе до снятия входного сигнала.

В качестве блока 9 задания тестов и анализа реакции может быть использована, например, персонально-профессиональная ЭВМ.

Устройство для контроля цифровых блоков работает следующим образом.

Объект 3 контроля до начала процесса обмена информацией подсоединяется к коммутатору 10, причем любой контакт коммутатора 10 может быть как входным, так и выходным, а в нерабочей состоянии на контакте устанавливается высокоимпедансное состояние. Все блоки устройства, подключаемые к блоку 9 задания тестов и анализа реакций, являются программно адресуемыми средствами блока 9.

В соответствии с блок-схемой алгоритма (фиг.З) до начала обмена информацией между объектом 3 контроля и блоком 9 задания тестов и анализа реакций производят

подготовительные операции, которые включают в себя следующее:

запись в первый блок 5 памяти программы коммутации процесса обмена; запись в блок 2 регистров программируемых временных интервалов:

а)длительности цикла обмена;

б)величины рабочей частоты обмена;

в)скважности рабочей частоты обмена; 0 запись в третий блок 7 памяти величины

стимулирующих воздействий программы контроля для объекта 3 контроля.

Запись в первый блок 5 памяти программы коммутации осуществляется следу5 ющим образом.

Адрес, определяющий номер тактового импульса процесса обмена, от блока 9 задания тестов и анализа реакций через группу 8 элементов ИЛИ поступает на адресный

0 вход первого блока 5 памяти. На выходе счетчика 4 в это время устанавливается код 00...0. Информация, содержащая данные, в каком режиме работает определенный канал коммутатора 10 в конкретный момент

5 времени обмена информацией с объектом 3 контроля, поступает от блока 9 задания тестов и анализа реакций на информационный вход первого блока 5 памяти и запоминается в нем.

0 Аналогично осуществляется запись величины стимулирующих воздействий программы контроля в третий блок 7 памяти.

Запись в блок 2 регистров программируемых временных интервалов длительно5 сти цикла обмена осуществляется путем передачи от блока 9 задания тестов и анализа реакций соответствующего кода на информационный вход регистра 11 кода временного интервала и записи кода при

0 поступлении на информационный вход дешифратора 20 от блока 9 задания тестов и анализа реакций адреса регистра 11. Величина рабочей частоты тактовых импульсов обмена и их скважность записывается ана5 логично в регистр 12 кода длительности импульсов.

Процесс обмена информацией с объектом 3 контроля начинается с момента подачи на дешифратор 20 адреса, вырабатывающего

0 на входе RS-триггера 15 лог. 1, который, в свою очередь, вырабатывает сигнал, разрешающий счет, на R-вход суммирующего счетчика 14 и управляющий сигнал на первый вход элемента И 19, разрешающий про5 хождение рабочей частоты тактовых импульсов. Синхроимпульсы от генератора 1 импульсов поступают в формирователь 17 сетки импульсов, который работает в режиме делителя частоты, и при помощи группы 17 элементов И, регистра 12 кода длительности импульса и элемента ИЛИ 18 рабочая частота тактовых импульсов с выхода элемента ИЛИ 18 поступает на второй (информационный) вход элемента И 19 и выдается на счетный вход счетчика 4. Тактовые импульсы с выхода элемента ИЛИ 18 поступают также в суммирующий счетчик 14. который начинает считать, и при достижении кода, равного длительности цикла обмена, блок 13 поразрядного сравнения выдается в RS-триггер 15 импульс на R-вход, При этом RS-триггер 15 формирует сигнал, запрещающий выдачу рабочей частоты тактовых импульсов, и сигнал прерывания, сообщающий блоку 9 задания тестов и анализа реакции об окончании цикла обмена и устанавливающий счетчик 4 в нулевое положение.

Процесс обмена с объектом 3 контроля осуществляется следующим образом.

Счетчик 4 через группу 8 элементов ИЛИ выдает код, соответствующий номеру тактового импульса в серии импульсов рабочей частоты программы контроля и соответствующий адресу, по которому первый 5 и третий 7 блоки памяти выдают, а блок 6 принимает информацию. При этом первый блок 5 памяти устанвливает на выходе код, определяющий, в каком режиме (прием или выдача) работает каждый канал, коммутатора 10, второй блок 6 памяти записывает значения ответных реакций на тех контактах объекта 3 контроля, которые определены программой контроля в данный момент времени как выходные, а третий блок 7 памяти через коммутатор 10 выдает на объект 3 контроля значения стимулирующих воздействий. При следующем такте блок 2 регистров программируемых временных интервалов счетчик 4 изменяет код на выходе на единицу и по новому адресу аналогично происходит обмен с объектом 3 контроля.

После окончания обмена информацией с объектом 3 контроля при получении сигнала прерывания блок 9 задания тестов и анализа реакций считывает информацию с второго блока 6 памяти, сравнивает ее с эталонной информацией, хранящейся в памяти блока 9 задания тестов и анализа реакций, и выдает на индикацию результат процесса контроля.

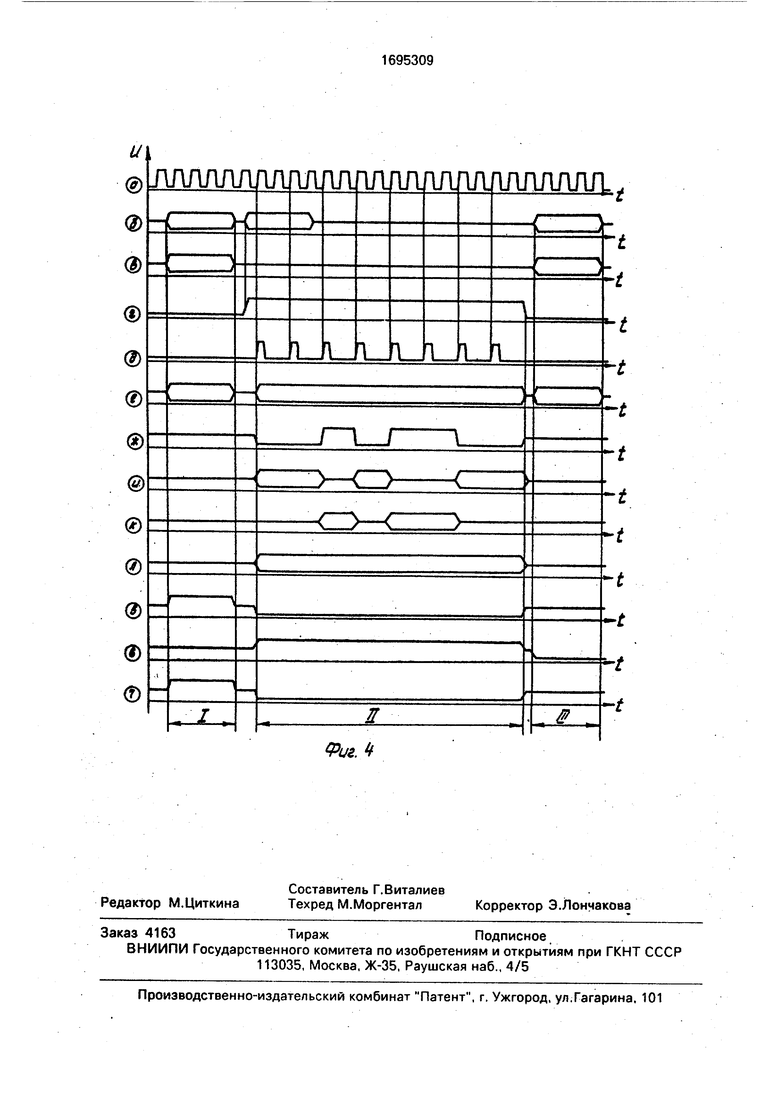

Временная диаграмма (фиг.4) поясняет более подробно работу устройства для контроля цифровых блоков. Устройство имеет три режима работы: I - запись программы контроля, II - обмен с объектом 3 контрбля, III - обработка результатов обмена.

В режиме I блок 9 задания тестов и анализа реакций формирует адрес б и данные в, которые поступают соответственно на второй вход группы 8 элементов ИЛИ и информационный вход первого блока 5 памяти, при этом на входе сбросат счетчика 4

устанавливается О, а по адресному входу е в первый блок 5 памяти записывается программа коммутации.

Режим записи первого блока 5 памяти на временной диаграмме 5 указан условно

0 в виде 1. Затем на адресном б и информационном в входах блока 2 регистров программируемых временных интервалов блок 9 задания тестов и анализа реакций устанавливает иформацию о параметрах рабо5 чей частоты тактовых импульсов, которая записывается в блок 2 регистров программируемых временных интервалов, при этом на выходе б вырабатывается О. В режиме I также формируется информация, содержа0 щая значение стимулирующих воздействий, которая поступает на информационный вход третьего блока 7 памяти по адресам, выдаваемым группой 8 элементов ИЛИ на адресный вход е третьего блока 7 памяти, и

5 записывается в нем (временная диаграмма 7). В режиме I на управляющем входе ж коммутатора 10 устанавливается третье состояние (средний уровень на временной диаграмме), при этом на двусторонних связях

0 л объекта 3 контроля (как и на линия и и к)

устанавливается также третье состояние и

обмен с объектом 3 контроля не происходит.

В режиме II при поступлении адреса б в

блок 2 регистров программируемых времен5 ных интервалов блок 2 устанавливает на выходе г лог. 1, которая разрешает счет импульсов, поступающих на счетный вход д счетчика 4. Счетчик 4 вырабатывает адрес на адресный вход е первого 5, второго 6 и

0 третьего 7 блоков памяти. В режиме II первый 5 и третий 7 блоки памяти работают в режиме выдачи (соответственно на временных диаграммах 5 и 7 указан О), а второй блок 6 памяти - в режиме записи (времен5 ная диаграмма 6 в состоянии 1). Первый блок 5 памяти на управляющем входе ж коммутатора 10 устанавливает сигнал О, если соответствующий канал коммутатора 10 должен работать в режиме приема, или 1

0 - в режиме выдачи информации. При установке управляющего входа ж в состояние О информация с объекта 3 контроля посредством линий л поступает через коммутатор 10 на информационный вход и второго

5 блока 6 памяти и записывается в нем по адресу, выдаваемому с выхода е группы 8 элементов ИЛИ. Если соответствующий канал коммутатора 10 устанавливается в режим выдачи, т.е. на входе ж лог. 1. то информация с выхода к первого блока 5

памяти поступает через коммутатор 10 в объект 3 контроля. По окончании цикла обмена с объектом 3 контроля блок 2 регистров программируемых временных интервалов вырабатывает на выходе г отрицательный фронт Z, счетчик 4 устанавливается в О и сообщает блоку 9 задания тестов и анализа реакций об окончании обмена.

Устройство переходит в режим HI, при этом блок 9 заданий тестов и анализа реакций вырабатывает адрес на втором информационном выходе б и считывает ответные реакции объекта 3 контроля из второго блока 6 памяти в, подавая адрес на адресный вход е второго блока 6 памяти (информационный вход и первый информационный выход блока 9 задания тестов и анализа реакций на временной диаграмме совмещены). При получении информации блок 9 задания тестов и анализа реакций производит обработку результатов программы контроля.

Формула изобретения Устройство для контроля цифровых блоков, содержащее блок задания тестов и анализа реакций, генератор импульсов, блок регистров программируемых временных интервалов, коммутатор и группу элементов ИЛИ, причем выход генератора импульсов соединен с синхровходом блока регистров программируемых временных интервалов, отличающееся тем, что, с целью расширения области применения за счет обеспечения контроля цифровых блоков с двунаправленным обменом, оно содержит

счетчик и три блока памяти, при этом информационный вход, адресный вход и первый вход блока регистров программируемых временных интервалов подключены соответственно к первому и второму информационным выходам блока задания тестов и анализа реакций и счетному входу счетчика, второй выход блока регистров программируемых временных интервалов соединен с

входом сброса счетчика и входом признака результата блока задания тестов и анализа реакций, первые я вторые входы элементов

ИЛИ группы подключены соответственно к выходу счетчика и первому информационному выходу блока задания тестов и анализа реакций, выходы элементов ИЛИ группы соединены с адресными входами первого, второго и третьего блоков памяти, информационный входи выход первого блока памяти

подключены соответственно к первому информационному выходу блока задания тестов и анализа реакций и управляющему входу коммутатора, информационный вход и выход второго блока памяти соединены

соответственно с информационным выходом коммутатора и информационным входом блока задания тестов и анализа реакций, первый информационный выход которого подключен к информационному

входу третьего блока памяти, выход третьего блока памяти соединен с информационным входом коммутатора, информационный вход-выход которого является входом-выходом устройства для подключения к входувыходу объекта контроля.

Фиг. 2

( Начало )

Задо/пь очередной

номер т0кто&ого

импульса

yornxff/пь программу

коммутации fffffot

f длв еонного так/поioto импульсу

1

PexuM П

Запуск не cvemvu

(

К

Формир

ffjra

PextjM

I

Задать о номер т

.

(давать гнрио&реЯяев частоты с 5

ISffffffmt &n/ffTtJfb#ocw t/ wwbeffpoffo tei/ WCWQ

ЈА/З&/ГН результа

С

Jfffltxfffftb SHffvewJ CftwHi/jNjpuHHiitjx 4oi- ffe&ef tu& S&OK,. Saff ffffttMOio ffwexfte

го sjtfffyjftcff

Pus. 3

}

0SMOAfO

mwecKtAh обмен co/tex- томЗ

Формиробо ние

ffjra ofli2 i7/ e0&6QvtJff

)

гдд r,,, . ,

Задать очередной номер тсгк/побого

.l/M/ yJbC0

Cvt/mff/пб отёелмые реакции tu footer 6 дл дамою тестового

i/AfflWbCCf

yfai, щмумсюсмд

нет

Сро6мть ответные реакции с у/полоном

ЈА/З&/ГН, наиндикоцц результату контроле

Конец,

)

(D

-O

-

, i

Фиг. t

t

t t

t -t

-t t -t

t

t -t

-t

@

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1988-02-08—Подача