Изобретение относится к вычислительной технике и может быть использовано при. построении запоминающих устройств.

Целью изобретения является упрощение контроля работоспособности устройства.

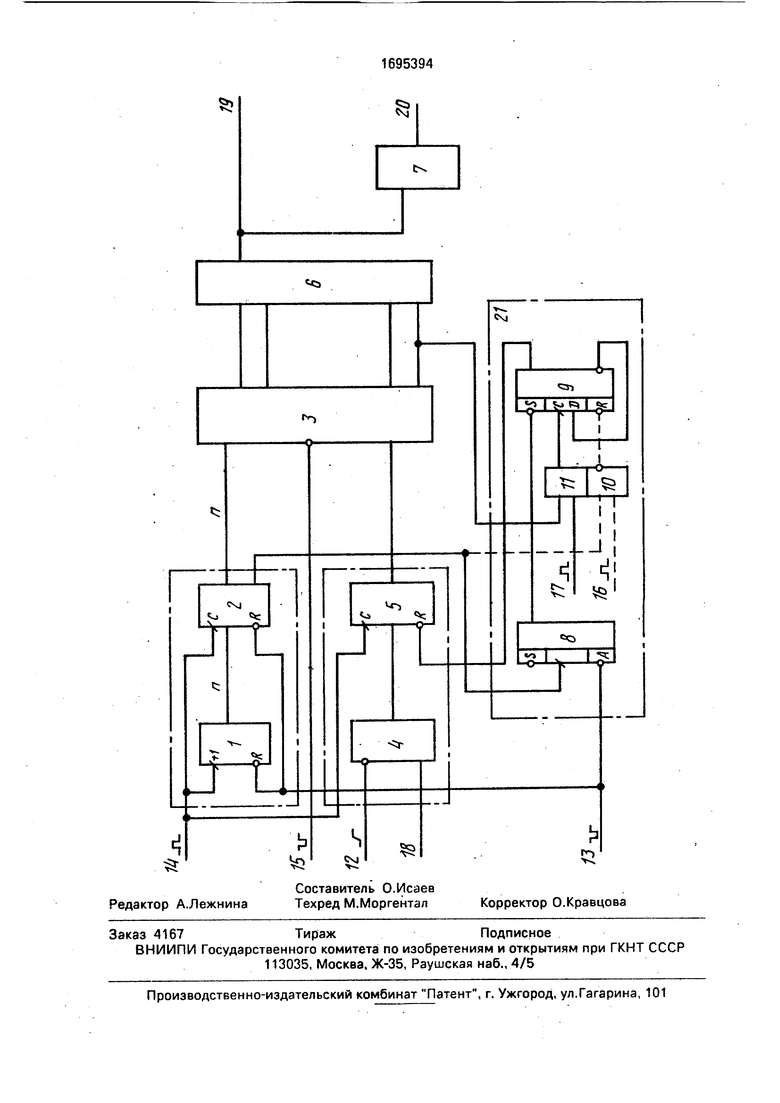

На чертеже представлена схема запоминающего устройства с тестовым самоконтролем.

Устройство содержит счетчик 1 адреса, регистр 2 адреса, накопитель 3, входные усилители 4, регистр 5 числа, выходной регистр 6, блок 7 контроля, первый 8 и второй 9 триггеры, элемент И-НЕ 10, элемент И-11, входы 12 задания режима, пуска 13, синхронизации 14, записи 15, сброса 16 и строби- рования 17 устройства, информационные входы 18 и выходы 19, а также выход 20 признака ошибки устройства.

Элементы 8, 9, 10 и 11 образуют задат- чик21 проверочных кодов.

Самоконтроль устройства осуществляется тестом Дождь по следующему алгоритму:

1.Подать положительный потенциал Проверка на вход 12. При этом на выходах усилителей 4 устанавливается третье состояние, оно эквивалентно логической единице.

2.Пропустить отрицательный импульс Пуск по входу 13. При этом происходит обнуление счетчика 1 и регистра 2 и установка в состояние 1 с помощью триггера 8 триггера 9.

3.На вход 14 приходит положительный импульс, по переднему фронту которого происходит перезапись нулевого кода адреса со счетчика 1 в регистр 2 и по его окончании переброс счетчика 1 в следующее состояние, а также установ по заднему фронту в состояние 1 регистра 5. Затем с помощью отрицательного импульса, прихоО

5 О СО

: ь

ящего на вход 15, происходит запись 1 о нулевому адресу в накопитель 3. Таким бразом, запись 1 происходит по первоу, второму и т.д. адресам до переброса К-разряда регистра 2 в состояние 1.

4.После переброса К-разряда регистра в 1 происходит переброс триггера 8 в остояние 1 и снятие отрицательного поенциала с входа S триггера 9 с помощью положительных импульсов, поступающих на вход 16, вырабатываются отрицательные импульсы элементов И-НЕ 10, устанавливающее триггер 9 в нулевое состояние; прием

читанного кода из накопителя 3 в триггер , с помощью положительного импульса, поступающего на вход 17, запись кода в регистр 5 и далее в накопитель 3.

Таким образом, происходит считывание/запись (регенерация) ранее записанной информации - всех 1.

При этом с помощью блока 7 контроля происходит контроль считанной информации. Режим Считывание-запись 1 происходит до переброса в О К-разряда регистра 2.

5.После переброса в О К-разряда прекращается выработка импульсов элементом И-НЕ 10, устанавливающих в О триггер 9, и он начинает работать как счетчик-сумматор по модулю 2 значений предыдущего и последующего состояний кодов накопителя 3, генерируя проверочные последовательности, с помощью усилителей 4 и регистра 5. Эти последовательности в виде равномерно чередующихся 1 и О, хорошо наблюдаются на выходах триггера 9, регистра 5, накопителя 3, выходного регистра 6 и блока 7 контроля. Таким образом, происходит непрерывная запись в накопитель 3 различных числовых последовательностей динамического кода Дождь. Она продолжается до переброса в 1 К-разряда регистра 2.

6.После переброса К-разряда в 1 повторяется п.4, но при этом многократно считывается-записывается (регенерируется) последняя комбинация динамического кода, образованная согласно п.5.

7.Повторение пп.5 и 6 и так далее.

В случае сбоя (нет по всем разрядам 1 или О) на выходе блока 7 контроля появляется сигнал ошибки.

Таким образом, использование предлагаемого устройства позволяет отказаться от

сложного стендового оборудования при изготовлении ЗУ и проверочного оборудования изделий, использующих ЗУ. Это позволяет уменьшить стоимость изготовления и эксплуатации ЗУ.

Формула изобретения Запоминающее устройство с тестовым самоконтролем, содержащее счетчик адреса, синхровход которого соединен с синхровходами регистра адреса и регистра числа и является входом синхронизации устройства, вход сброса счетчика адреса подключен к входу сброса регистра числа и является входом пуска устройства, выходы

счетчика адреса соединены с информационными входами регистра адреса, выходы группы которого подключены к адресным входам накопителя, выходы которого соединены с входами выходного регистра, выходы которого являются информационными выходами устройства и подключены к входам блока контроля, выход которого является выходом признака ошибки устройства, информационные входы накопителя соединены с выходами регистра числа, информационные входы которого подключены к выходам входных усилителей, информационные входы которых являются информационными входами устройства, вход записи

накопителя является входом записи устройства, отличающееся тем, что, с целью упрощения контроля работоспособности запоминающего устройства, в него введен задатчик проверочных кодов, содержащий

первый и второй триггеры, элемент И и элемент И-НЕ, причем R-вход первого триггера подключен к входу пуска устройства, a D- вход является входом логической единицы устройства, С-вход первого триггера соединен с выходом регистра адреса и первым входом элемента И-НЕ, второй вход которого является входом сброса устройства, а выход подключен к R-входу второго триггера, D-вход и инверсный выход которого объединены, а С-вход подключен к выходу элемента И, первый вход которого соединен с одним из выходов накопителя, а второй вход является входом стробирования устройства, S-вход второго триггера подключен к выходу первого триггера, прямой выход второго триггера соединен с входом сброса регистра числа, управляющие входы входных усилителей являются входом задания режима устройства.

s

§

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Устройство для программного управления намоточным станком | 1990 |

|

SU1784942A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Целью изобретения является упрощение контроля работоспособности устройства. Устройство содержит счетчик адреса, регистр адреса, накопитель, входные усилители с выходом на три состояния, регистр числа, выходной регистр, блок контроля, за- датчик проверочных кодов, включающий первый и второй триггеры, элемент И-НЕ и элемент И. Цель изобретения достигается тем, что для генерации теста используются только блоки, непосредственно входящие в состав устройства, а также тем, что результаты контроля могут визуально наблюдаться на экране осциллографа. 1 ил.

Г)

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Самофалов К.Г., Корнейчук В.И., Город- ний А.В | |||

| Структурно-логические методы повышения надежности ЗУ, М,: Машиностроение, 1976, с.33-63. | |||

Авторы

Даты

1991-11-30—Публикация

1988-12-27—Подача