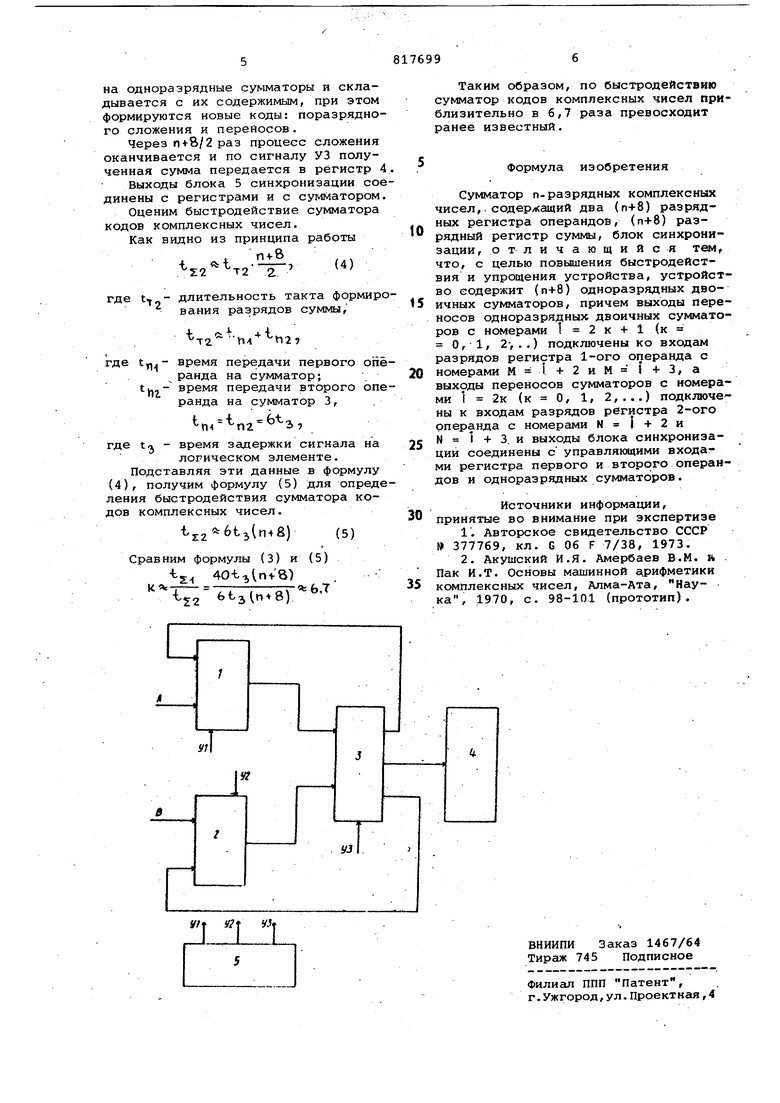

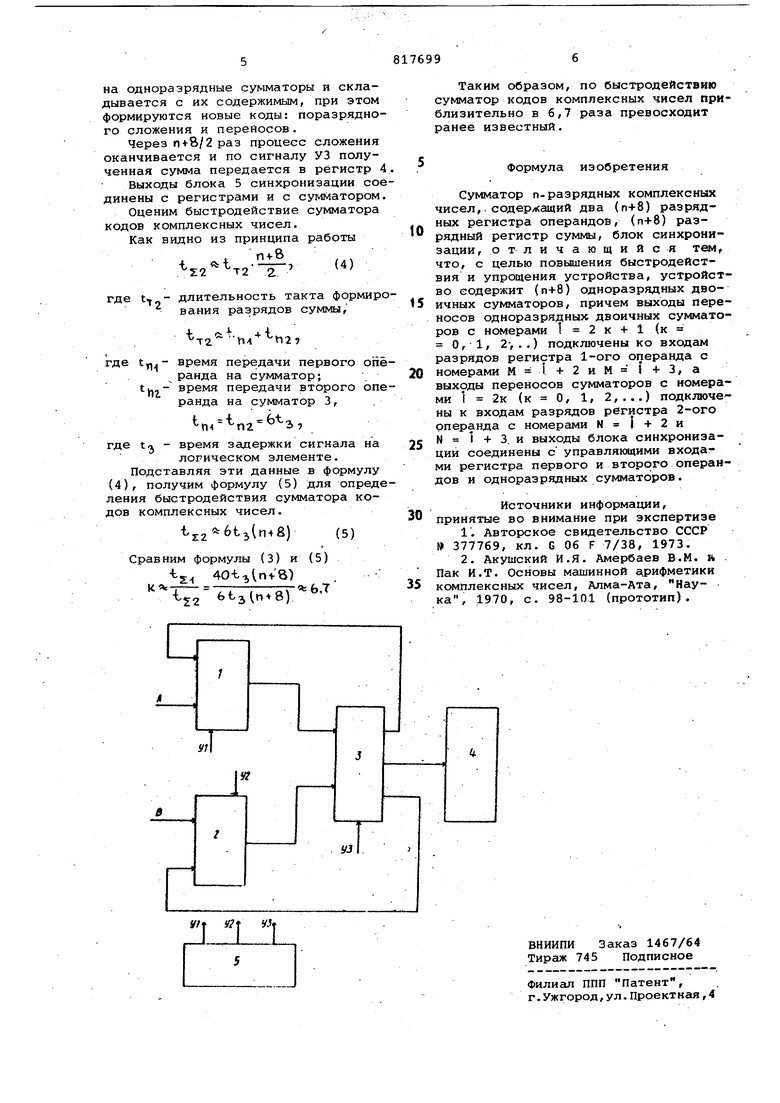

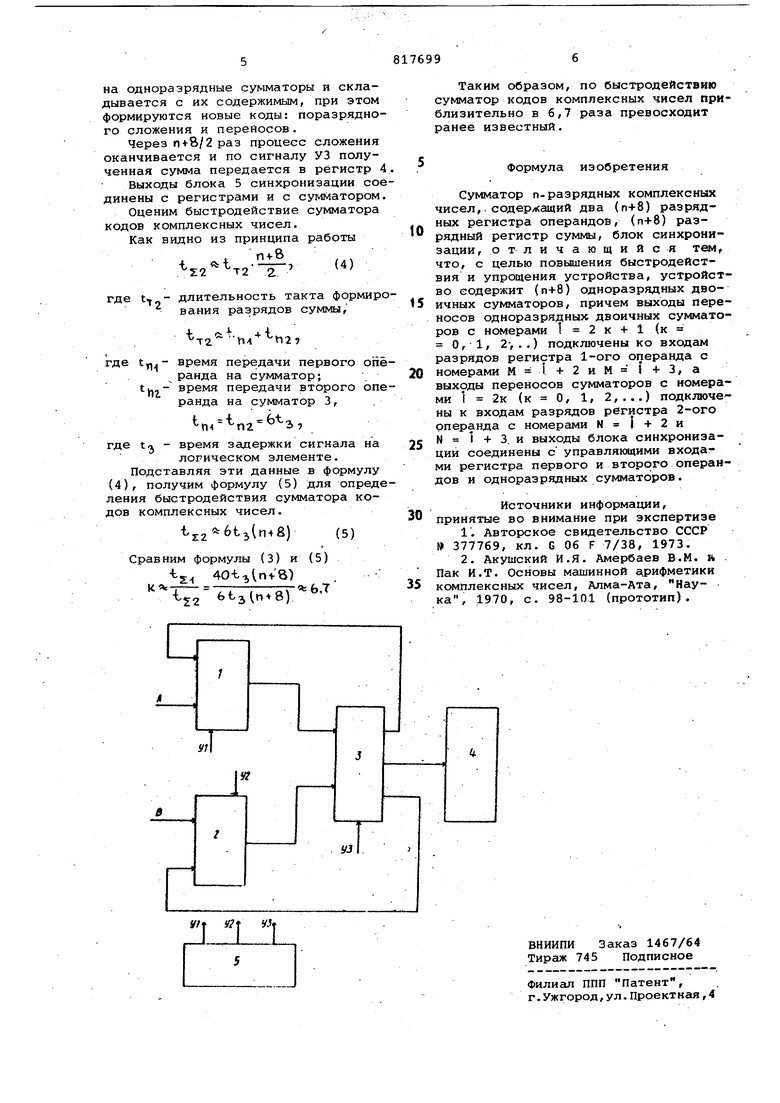

Изобретение относится к вычислительной технике и может быть исполь зовано в вычислительных машинах и комплексах. Известны сумматоры кодов комплек ных чисел, содержащие два регистра .операндов,- ком чутатор, два двоичных сумматора, регистр результатов ij . Наиболее близким по технической .сущности к предлагаемому является сумматор, содержащий регистр 1-ого операнд, регистр 2-ого операнда,ре гистр общего переноса, схему анализа наличия нулевого цикла (НЦ),схему формирования общего переноса при наличии НЦ,схему формирования общего переноса при отсутствии НЦ, коммутатор переносов, схему формирования разрядов сумглы при наличии НЦ, схему формировани разрядов суммы при отсутствии НЦ, коммутатор разрядов суммы, регистр суммы, схему определения момента окончания сложения и синхронизатор И Алгоритм сложения кодов комплексных чисел, положенньШ в основу работы данного устройства, основан на последовательном принципе формирования разрядов суммы. Перед началом такта формирования i-того разряда суммы разряды с номерами i,i +1, i +2 обоих операндов и общего переноса анализируются на наличие НЦ. При наличии НЦ формируются г-и, i + 1-й, i + 2-й разряды суммы и общий перенос в следующие разряды. При отсутствии НЦ формируется i-и разряд суммы и общий перенос в следующие разряды. Операнды и общий перенос сдвигаются в сторону младших разрядов на 3 разряда при наличии НЦ, на 1 разряд при отсутствии НЦ. Процесс формирования разрядов повторяется до получения суммы. На основании описанного алгоритма сложения комплексных чисел время сложения определяется по формуле Ч. 1Ц--Ь2), 1) где t t-r (-5) длительность процедуры сложения операндов вида НЦ.НЦ.НЦ.НЦ.НЦ.НЦ. 111111111111111111 - i-ай операнд 011011011011011011 - 2-ой операнд 000000000000000000 - сумма; t2 t-r (n+S) - длительность процедуры сложения при отсутствии НЦ на протяжении всей операции; ж - множитель, указывающий на ра новероятное появление обоих видов комбинаций операндов; t-f - длительность такта формиро вания разрядов суммы. П9дставляя эти данные в формулу (1), получаем формулу (2) для определения времени сложения Ч.) (2) В такте формирования разрядов суммы, основные временные затраты приходлтся на формирование общего переноса в старшие разряды Ч.Ч, где tun 6t« - время анализа разр дов операндов на н личие нц; сюп 30ta - время формирования переноса , t,, - время перекоммутации ; teu 6ta время занесения в регистр общего пер носа 3; еле время сдвига инфор мации в регистрах 1-4; ta - Время задержки на одном логическом элементе. Суммируя, получаем время t форм рования общего переноса . Тогда общая формула для определе ния времени сложения выглядит следующим образом t 40-t3-tn+B) Основным недостатком известных сукматоров кодов комплексных чисел является низкая скорость работы и большие затраты в оборудовании. Цель изобретения - повьоиение быс родейстВИЯ и упрощение устройства. Поставленная цель достигается т что сумматор п разрядных комплексны чисел, содержащий два (п+8) разряд ных регистра операндов, (п+8) раз рядный регистр суммы, блок синхрон зации, содержит (п+8) одноразрядны двоичных сумматоров, причем выходы переносов одноразрядных двоичных сумматоров с номерами I - 2 к + + 1 (к О, 1, 2,4..) подключены к входам разрядов регистра 1-ого 9Де ранда с номерами М 1 + 2 и М i+ а выходы переносов сумматоров с но - рами I « 2к (,1,2...) подключен входам разрядов регистра 2-ого опеанда с номерами N I + 2 и N 1 + 3 и выходы блока синхронизации оединены с управлянвдими входами реистрации первого и второго операнов и одноразрядных сумматоров. На чертеже представлена функциональная схема сумматора п разрядных омплэксных чисел. Устройство содержит регистр 1 перого операнда, регистр 2 второго операнда, (п+8) одноразрядных двоичных сумматоров 3, входы которых подключены к выходам соответствующих азрядов регистров операндов, а выходы суммы ко входам соответствующих разрядов регистров суммы. При выполнении операции сложения из операндов формируется двоичный код, значения разрядов которого являются суммой по модулю два разрядов операндов, и переносы при поразрядном суммировании. Два младших разряда полученного двоичного кода являются истинными младшими разрядами суммы. Переносы группируются в два кода, в зависимости от номера одноразрядного двоичного сумматора, из которого они возникли (переносы из нечетных одноразрядных сумматоров в первый код, переносы из четных во второй). Двоичные коды, сформированные из переносов, и код, полученный в результате.поразрядного сложения, участвуют в формировании следующей пары разрядов суммы, при этом получается новый код поразрядного сложения и коды переносов.(младшие разряды кода поразрядного сложения являются следующими разрядами суммы). Пара разрядов суммы, полученная в очередном такте суммирования, в следующем такте не используется. Процесс повторяется до получения полной суммы кодов комплексных чисел, т.е.. П4-8/2 раз. Разрядность регистров операндов, регистра суммы, а также количество одноразрядных двоичных сумматоров равна (п+8), так как для данной системы счисления (р -1 + j - основание системы счисления) разрядность результата максимум (п+8). Устройство работает следующим образом. После приема первого и второго операндов на регистры 1 и 2 соответ.ственно по сигналу У1 разряды первого операнда подгшзтся на соответствующие им одноразрядные сумматоры 3, по сигналу У2 разряд второго операнда поступают на соответствующие им одноразрядные сумматоры 3, где формируется код поразрядного сложения. На регистрах 1 и 2 формируются коды переносов из нечетных и четных одноразрядных сумматоров соответственно. По следующей паре сигналов У1 и У2 содержимое регистров 1 и 2 подается

на одноразрядные сумматоры и складывается с их содержимым, при этом формируются новые коды: поразрядного сложения и переносов.

Через п+8/2 раз процесс сложения оканчивается и по сигналу УЗ полученная сумма передается в регистр 4

выходы блока 5 синхронизации соединены с регистрами и с сумматором.

Оценим быстродействие сумматора кодов комплексных чисел.

Как видно из принципа работы

t.-t,. (4)

Т2 2

где t - длительность такта формиро2 вания разрядов суммы,

.г-)

-.- времяпередачи первого опеtрандана сумматор; tt.- времяпередачи второго операндана сумматор 3,

:6t

37

где ta - время задержки сигнала на

логическом элементе. Подставляя эти данные в формулу (4), получим формулу (5) для опредления быстродействия сумматора кодов комплексных чисел.

-za t-bin- S) (5) Сравним формулы (3) и (5)

)

2:

:fe.7

i

Таким образом, по быстродействию сумматор кодов комплексных чисел приблизительно в 6,7 раза превосходит ранее известный.

формула изобретения

Сумматор п-разрядных комплексных чисел, содержащий два (п-ь8) разрядных регистра операндов, (п-ь8) разрядный регистр суммы, блок синхронизации, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, устройство содержит (п+8) одноразрядных двоичных сумматоров, причем выходы переносов одноразрядных двоичных сумматоров с номерами I 2 к + 1 (к О, 1, 2..) подключены ко входам разрядов регистра 1-ого операнда с номерами М ; 1 + 2 и М I + 3, а выходы переносов сумматоров с комарами I 2к (к О, 1, 2,...) подключены к входам разрядов регистра 2-ого операнда с номерами N j + 2 и К 1 + 3. и выходы блока синхронизации соединены с управляющими входаг ми регистра первого и второго операндов и одноразрядных сумматоров.

ИСТОЧНИКИ информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 377769, кл. G 06 F 7/38, 1973.

2.Акушский И.Я. Амербаев В.М. к Пак И.Т. Основы машинной арифметики

комплексных чисел, Алма-Ата, Наука, 1970, с. 98-101 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Процессорный элемент | 1980 |

|

SU881757A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

Авторы

Даты

1981-03-30—Публикация

1979-05-24—Подача