i

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1989 |

|

SU1762410A1 |

| Преобразователь кодов | 1988 |

|

SU1501279A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Устройство для аналого-цифрового преобразователя | 1988 |

|

SU1594687A1 |

| Преобразователь напряжение-код | 1988 |

|

SU1508343A1 |

| Цифровая система программного управления | 1987 |

|

SU1460713A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

Изобретение относится к автоматике, информационно-измерительной и вычислительной технике. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования двоичного кода в код с основанием √2. В преобразователь кодов, содержащий регистр 1 и блок умножения 2, дополнительно введены группа элементов ИЛИ 3, элемент И-НЕ 4, расширитель 5, выходной регистр 6, а расширитель 5 содержит первую и вторую группы элементов И. 1 з.п.ф-лы, 2 ил.

сл ю

сд

00

Изобретение относится к автомати- ке, информационнр-измернтельной и вычислительной технике и может быть использовано для преобразования двоич ноге кода в код ,с основанием v2.

Целью изобретения является расширение класса решаемых задач путем обеспечения преобразования в код с основанием VJ.

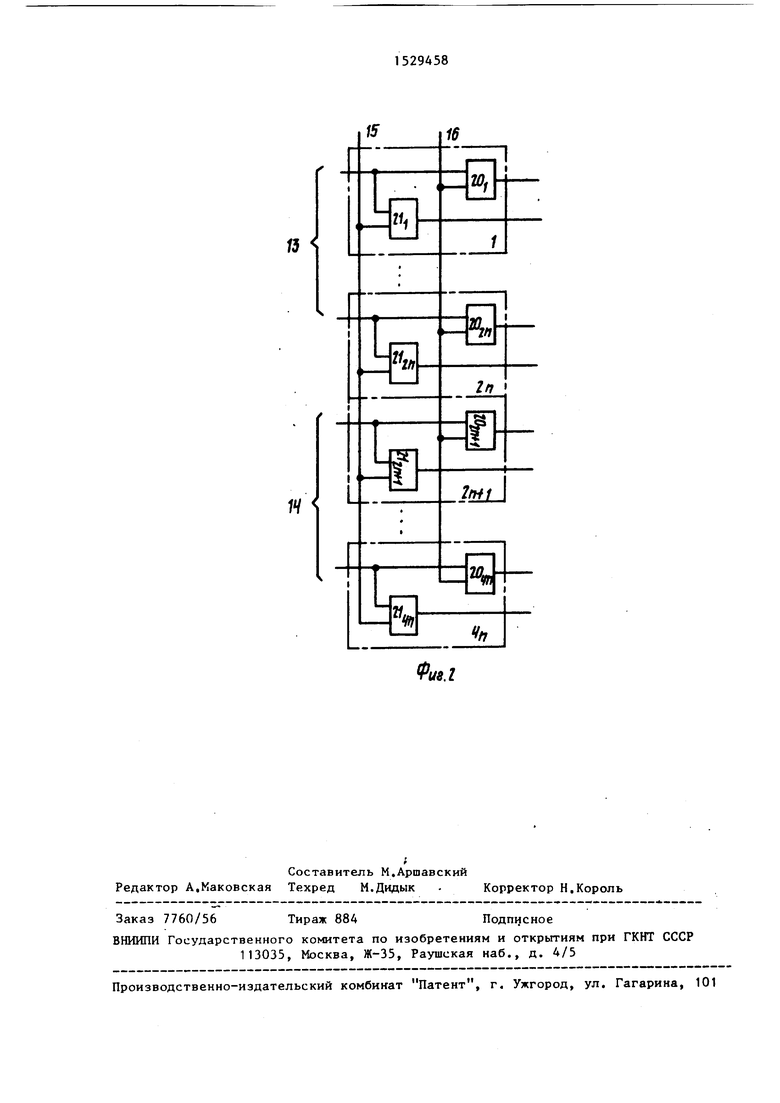

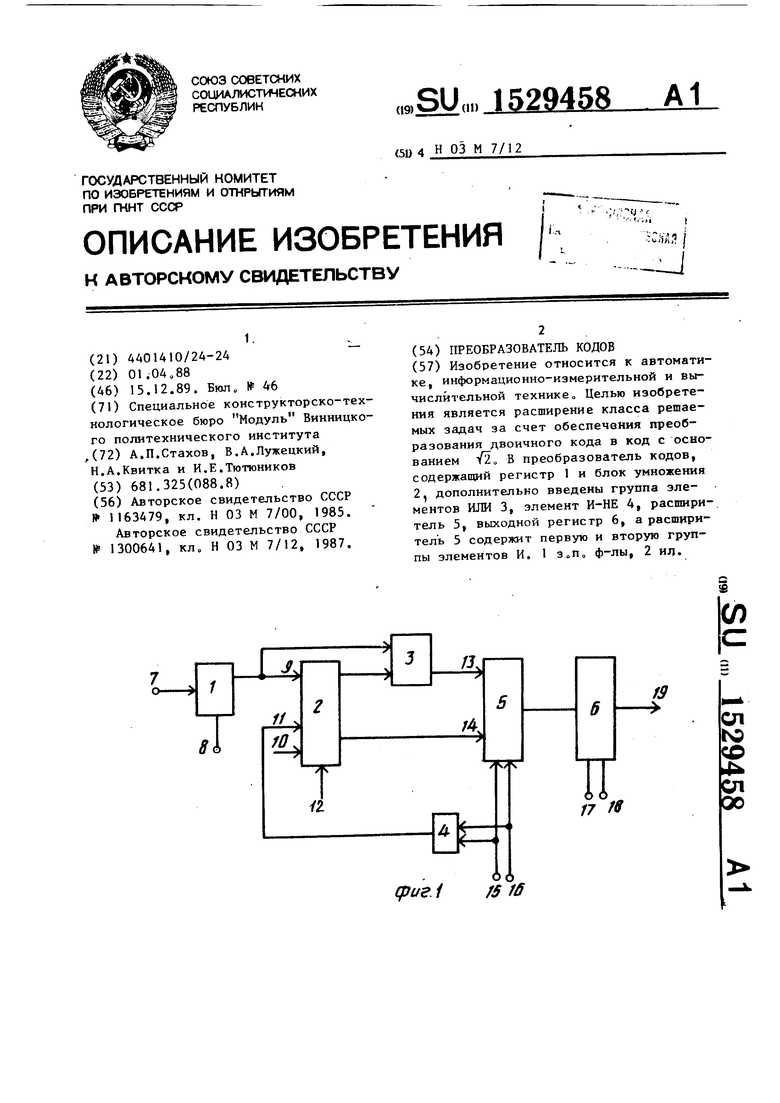

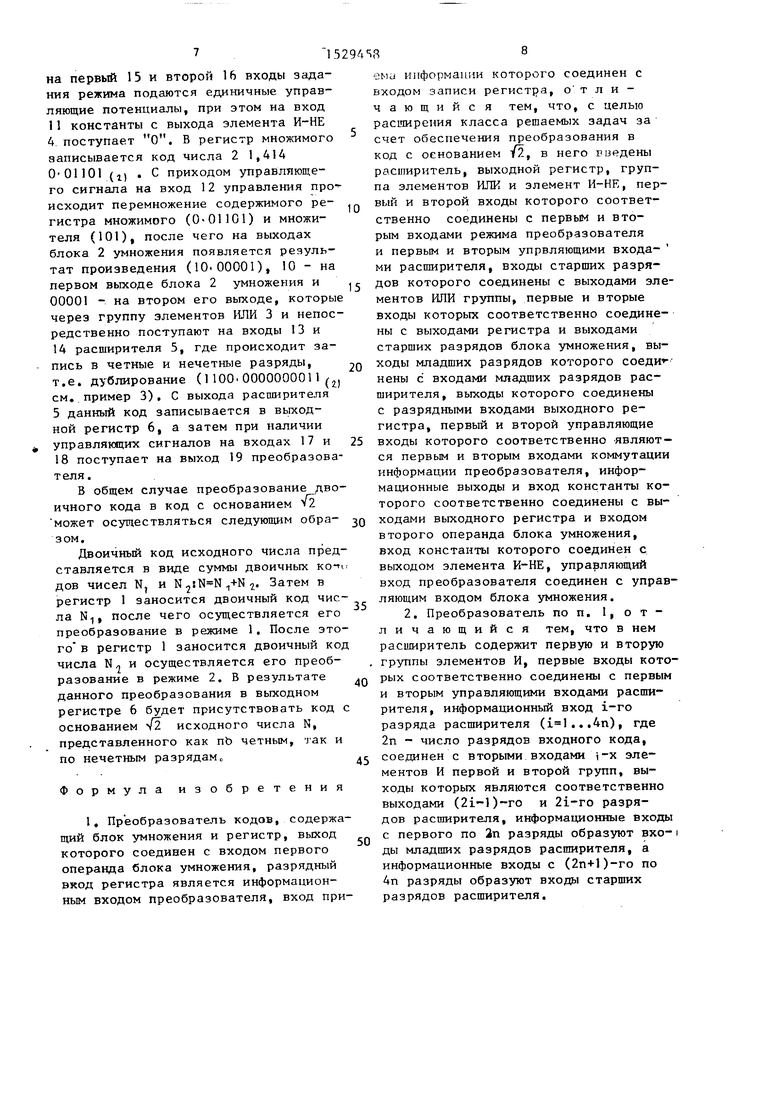

На фиг,1 приведена структурная схема предлагаемого преобразователя; на фиг.2 - функциональная схема расширителя (5) о

Преобразователь (фиг.)) содержит регистр 1, блок 2 умножения (БУ). группу элементов ИЛИ 3, элемент .И-НЕ А, расширитель 5, выходной регистр 6, информационный вход 7 преобразователей, вход 8 выдачи информации, вхо- ды первого 9 и второго 10 операндов блока 2 умножения, вход 11 константы блока умножения, вход 12 управления преобразователя, входы младших 13 и старших 14 разрядов расширителя, nepвьй 15 и второй 16 входы режима преобразователя, первый 17 и второй 18 входы вьщачи информации, выход 19 пре 1образователя „

Расширитель 5 (фиг.2) содержит первую группу элементов И 20, вторую группу элементов И 21. Каждая из груп элементов И 20, 21 содержит по четы ре элемента

В основу построения предлагаемого преобразователя положено следующее.

Число N, представленное в 2п-раз, рядном коде с основанием -/2, имеет вид

2n-t

,,, ( /2) -.а,„., ( /2)

Ih-Z

-ba(V2)...-t-a(V2)%a,(/2) +

+ ao(V2)

(1)

V Веса разрядов кода с основанием 2 составляют последовательность

.„J6 /2, 16, 8 V2, 8, 4 /2, 4,

2 /2, 2, -/2, 1(2)

Из выражения (2) следует, что четные степени являются весами разрядов двоичного кода, а нечетные - ве- сами двоичного кода, умноженными на

, С учетом этого код числа N, представленный выражением (1), запишем в виде

-/2 Z: а.2 тг ы

гп-г

+ Z а-2 J-

J/

(3)

где а;, а. е i О, 1 } и являются цифрами двоично-кодированной системы счисления с основанием /2, а i, j для 2п-разрядных чисел принимают значения:

i е Г1,3,5,...,2п-1 I J е 0,2,)

5 0 5

0

5

0

5

0

,

Первый член формулы (3) составляет сумму нечетных разрядов кода NJ а второй - сумму четных разрядов этого же кода о Выражение (3) содержит две двоичные части

Произвольное число N в системе счисления с основанием представляется неоднозначным, так как его можно произвольно разбить на два числа N и . При этом число N, можно представить в коде с основанием /2 по нечетным разрядам, а N - по четным, и наоборот Число способов разбиения числа N на N и N определяется разрядной сеткой исходного числа о

Рассмотрим три варианта такого представления, каждому из которых соответствует свой режим преобразования „

Вариант 1. Представление исходного числа N только по четным разрядам, при этом нечетные разряды заполняются нулями, т.е. /см.формулу (3)),

(1)

Пример 1-, , . 101 01000Ц.

Вариант 2„ Представление числа N только по нечетным разрядам, при этом четные разряды заполняются нулями, т.е„ а; 0 (см. формулу (3)).

Пример 2. (1 ЮЮ « .4000 (, -949(,,, .

Алгоритм преобразования следующий. Исходное число N, представленное в двоичном коде согласно формуле (3), умножается на двоичный эквивалент числа т2, после чего происходит сдвиг результата произведения на один разряд в сторону младших разрядов. Это соответствует записи результата произведения в соответствующие разряды. Затем производим расширение полученного результата, т„е, после каждого разряда произведения будет находиться разряд, содержащий нуль, а общее число разрядов удваивается.

p. N.5,..1000,,,

101(г, с 1 11

Приме А-949(10) .

/2-1-01 101(11

/2-N(t, 1 -01101 (, 00001 (1,.

После сдвига на один разряд вправо: 11 -1000001 (71 .

После расширения полученного результата: 1010 100000000010 (Yi).

Таким образом, ::i 1 010-1000 у)«

Вариант 3, Представление числа N по четным и нечетным разрядам совместно. Алгоритм преобразования следую-

N,,N(/2-1.) (V2 + 1 )M(V2-H )N(yj,, (4)

где -() N 0,414,

Тое„ исходное число N, представленное

ра 1 через группы элементов ИЛИ 3 ступает на вход 13 расширителя 5, происходит его пространственное р ширение (пример: )010001). С вых расширителя 5 данный код записывае ся в выходной регистр 6, а затем п ступает на вход 19 преобразователя при наличии управляющего сигнала н входе 17„

Преобразование двоичного кода в код с основанием -/2 по нечетным разрядам,

В исходном состоянии на первый 5 и второй 16 входы режима преобразо теля поданы нулевые управляющие потенциалы Двоичный код исходного числа (101) заносится а регистр I. С приходом управляющего сигнала на

10

в двоичном коде, умножается на двоич- 20 вход 8 выдачи информации двоичный ный эквивалент числа (-1). Затем

код исходного числа с выхода регис ра 1 поступает на вход 9 первого о ранда блока 2 умножения, после чег выдача информации из регистра 1 пр кращается путем подачи на вход 8 н левого потенциала„ Затем на первый 15 и второй 16 входы режима подают управляющие потенциалы О и 1 с ветственно ,при этом на вход М кон

производится расширение полученного результата К, Тое„ после каждого разряда прризведения будет.находиться разряд, содержащий нуль, а общее 25

число разрядов удваивается. Затем производим сдвиг полученного кода на один разряд в сторону стйрших разрядов и сложение полученного кода с кодом

до сдвига. Данные операции эквивалент-Ю станты с выхода элемента И-НЕ 4 пены умножению числа на (/2-ь1) (см. фор- ступает 1, а на входе второго oneкод исходного числа с выхода регистра 1 поступает на вход 9 первого операнда блока 2 умножения, после чего выдача информации из регистра 1 прекращается путем подачи на вход 8 нулевого потенциала„ Затем на первый 15 и второй 16 входы режима подаются управляющие потенциалы О и 1 соот ветственно ,при этом на вход М кон 5,)

мулу (4)). в

Пример 3. N

V2-1 O Ol 101 (2,

N-(2-1) 101(г,- O OllOl (J, 10 «00001(,.

Необходимо отметить,что последние три операции расширения, сдвиг и сложение соответствуют операции представления каждой цифры разряда двумя идентичными цифрами, что и реализовано в преобразователе.

Предлагаемый преобразователь работает следующим образом

Рассмотрим его работу в трех режимах о

Преобразование двоичного кода в код с основанием V2 по четным разрядам.

В исходном состоянии на первый

15 и второй 16 входы режима поданы управляющие потенциалы 1 и О соответственно. Блок 2 умножения в работе не участвует„ Двоичный код исход ного числа заносится в регистр 1. С приходом управляющего сигнала на вход В выдачи информации двоичный код исходного числа с выхода регистра 1 через группы элементов ИЛИ 3 поступает на вход 13 расширителя 5, где происходит его пространственное расширение (пример: )010001). С выхода расширителя 5 данный код записывается в выходной регистр 6, а затем поступает на вход 19 преобразователя при наличии управляющего сигнала на входе 17„

Преобразование двоичного кода в код с основанием -/2 по нечетным разрядам,

В исходном состоянии на первый 15 и второй 16 входы режима преобразователя поданы нулевые управляющие потенциалы Двоичный код исходного числа (101) заносится а регистр I. С приходом управляющего сигнала на

вход 8 выдачи информации двоичный

код исходного числа с выхода регистра 1 поступает на вход 9 первого операнда блока 2 умножения, после чего выдача информации из регистра 1 прекращается путем подачи на вход 8 нулевого потенциала„ Затем на первый 15 и второй 16 входы режима подаются управляющие потенциалы О и 1 соответственно ,при этом на вход М конранда 10 блока 2 умножения присутствует двоичный код числа V2 -1«0,А14 -0-01 101 ( . Информация с входов 10

и I1 записьтается в регистр множимого С приходом сигнала на вход 12 управления происходит перемножение со- ; держимого регистра множимого (1 xOllOl) и множителя (101) и сдвиг результата произведения на один разряд вправо, после чего на выходах блока 2 умножения появляется результат произведения (11-100001), 10 - на первом выходе блока 2 умножения и О ЮООГ --

на втором его выходе, которые через группу элементов ИЛИ 3 и непосредственно поступают на входы 13 и 14 расширителя 5, где происходит запись в нечетные разряды и расширение (lOlOx

1000 (У5;), см. пример 2). С выхода расширителя 5 данный код записывается в выходной регистр 6, а затем при цаличии управляющего сигнала на входе 18 поступает на выход 19 преобразова- теля.

Преобразование двоичного кода в од с основанием /2 по четным и нечетым разрядам совместно отличается т описанного вьппе режима тем, что

на первый 15 и второй 16 входы задания режима подаются единичные управляющие потенциалы, при этом на вход 11 константы с выхода элемента И-НЕ 4. поступает О. В регистр множимого записывается код числа 2 1,414 О 01101 (i) . С приходом управляющего сигнала на вход 12 управления про исходит перемножение содержимого регистра множимого (0-01101) и множителя (101), после чего на выходах блока 2 умножения появляется результат произведения (10-00001), 10 - на первом выходе блока 2 умножения и 00001 - на втором его выходе, которые через группу элементов ИЛИ 3 и непосредственно поступают на входы 13 и 14 расширителя 5, где происходит запись в четные и нечетные разряды, т.е. дублирование (1 ЮО ООООООООП (, см, пример 3). С выхода расширителя 5 данный код записывается в выходной регистр 6, а затем при наличии управляющих сигналов на входах 17 и 18 поступает на выход 19 преобразова- т еля.

В общем случае преобразование двоичного кода в код с основанием V2 может осуществляться следующим обра- зом.

Двоичный код исходного числа представляется в виде суммы двоичных ко-и дов чисел N, и N2iN Ni+N2. Затем в регистр 1 заносится двоичный код числа N, после чего осуществляется его преобразование в режиме 1. После этого в регистр 1 заносится двоичный код

числа N, и осуществляется его преобразование в режиме 2, В результате данного преобразования в выходном регистре 6 будет присутствовать код с основанием V2 исходного числа N, представленного как пЬ четным, так и по нечетным разрядам

Формула изобретения

1, Преобразователь кодов, содержащий блок умножения и регистр, выход которого соединен с входом первого операнда блока умножения, разрядный вход регистра является информационным входом преобразователя, вход при8

0

5

0

0

5

35

40

45

50

ема информации которого соединен с входом записи регистра, о т л и - чающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения преобразования в код с основанием /2, в него введены расширитель, выходной регистр, группа элементов ИЛИ и элемент И-НЕ, первый и второй входы которого соответственно соединены с первым и вторым входами режима преобразователя и первым и вторым упрвляющими входа- ми расширителя, входы старших разрядов которого соединены с выходами элементов ИЛИ группы, первые и вторые входы которых соответственно соединены с выходами регистра и выходами старших разрядов блока умножения, выходы младших разрядов которого соеди - нены с входами младших разрядов расширителя, выходы которого соединены с разрядными входами выходного регистра, первый и второй управляющие входы которого соответственно являются первым и вторым входами коммутации информации преобразователя, информационные выходы и вход константы которого соответственно соединены с выходами выходного регистра и входом второго операнда блока умножения, вход константы которого соединен с выходом элемента К-НЕ, управляющий вход преобразователя соединен с управляющим входом блока умножения.

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-01—Подача