второго процессоров, информационный выход мультиплексора адреса соединен с адресным входом блока оперативной памяти, информационный вход-выход которого соединен с первым информационным входом- выходом первого шинного формирователя, второй информационный вход-выход которого соединен с входом-выходом данных первого процессора устройства, выход триггера соединен с управляющим входом мультиплексора адреса и с входом разрешения первого шинного формирователя, первый информационный вход-выход второго шинного формирователя соединен с информационным входом-выходом блока оперативной памяти, второй информационный вход-выход второго шинного формирователя соединен с входом-выходом данных второго процессора устройства, выход запроса которого соединен с инверсным входом сброса триггера, инверсный вход установки которого соединен с выходом запроса от первого процессора устройства, выход управления чтением-записью от первого процессора которого соединен с управляющим входом первого шинного формирователя и первым информационным входом первой группы мультиплексора управления оперативной памятью, второй информационный вход первой группы которого соединен с выходом управления обменом от первого процессора устройства, выход управления чтением-записью от второго процессора устройства соединен с управляющим входом второго шинного формирователя и первым информационным входом второй группы мультиплексора управления оперативной памятью, второй информационный вход в горой группы которого соединен с выходом управления обменом от второго процессора устройства, первый информационный выход мультиплексора управления оперативной памятью соединен с входом управления чтением-записью блока оперативной памяти, вход управления обменом которого соединен с вторым информационным выходом мультиплексора управления оперативной памятью, вход управления которого соединен с выходом триггера, входом подтверждения запроса от первого процессора устройства и входом элемента НЕ, выход которого соединен с выходом разрешения второго шинного формирователя и входом подтверждения запроса второму процессору устройства.

Недостатком устройства-прототипа является низкая оперативность обмена, которая обусловлена следующим,

В устройстве-прототипе осуществляется двусторонний обмен информацией между общей памятью и каждым из сопрягаемых с ней процессоров. Первый (второй) процессор, выставив запрос на доступ к общей памяти и получив разрешение на обмен

данными, обеспечивает обмен массивом слов данных между общей памятью и своей памятью. При этом второй (первый) процессор, выставив запрос на доступ к общей памяти, непроизводительно простаивает,

0 ожидая окончания обмена данными между общей памятью и первым процессором. Доступ к общей памяти второй (первый) процессор получает только в момент обмена последним словом данных из массива пере5 даваемой информации между первым (вторым) процессором. В этом случае снижается оперативность обмена данными, т.к. время доступа процессора к общей памяти будет равно сумме времен передачи всех слов

0 данных из массива передаваемой информации между другим процессором ч общей памятью. В устройстве-прототипе отсутствуют технические средства, позволяющие обеспечить очередное обслуживание двух

5 процессоров в режиме передачи одиночных слов данных между процессорами и общей памятью, Невозможность быстрого доступа к общей памяти существенно понижает оперативность обмена данными в многопро0 цессорных вычислительных системах.

В связи с этим целью изобретения является повышение оперативности обмена информацией.

Поставленная цель достигается тем, что

5 в устройство для сопряжения двух процессоров через общую память, содержащее блок оперативной памяти, первый и второй шинные формирователи, мультиплексор адреса, мультиплексор управления, первый

О триггер, элемент НЕ, причем первый и второй информационные входы мультиплексора адреса соединены соответственно с входами устройства для подключения к шипам адреса первого и второго процессоров,

5 выход мультиплексора адреса соединен с адресным входом блока оперативной памяти, информационный вход-выход которого соединен с первыми информационными входами-выходами первого и второго шинных

0 формирователей, вторые информационные входы-выходы которых являются входами- выходами устройства для подключения к шинам данных первого и второго процессоров, входы установки и сброса первого триг5 гера являются входами устройства для подключения соответственно к выходам запроса доступа первого и второго процессоров, первые управляющие входы первого и второго шинных формирователей являются входами устройства для подключения соответственно к выходам чтения/записи первого и второго процессоров и соединены с первыми информационными входами мультиплексора управления, вторые информационные сходы которого являются входами устройства для подключения к выходам управления обменом соответственно первого и второго процессоров, выход элемента НЕ соединен со вторым управляющим входом второго шинного формирователя и является выходом устройства для подключения ко входу разрешения доступа второго процессора, первый и второй выходы мультиплексора управления соединены соответственно со входами чтения/записи и обмена блока оперативной памяти, дополнительно введены второй триггер, с первого по четвертый элементы И, элемент ИЛИ, причем первый и второй входы первого элемента И объединены соответственно со входами установки и сброса первого триггера, выход первого элемента И соединен с первыми входами второго, третьего и четвертого элементов И, второй вход второго элемента И является синхровходом устройства, а выход - соединен со счетным входом второго триггера, выход которого соединен со вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, выход первого триггера соединен со вторым входом четвертого элемента И, выход которого соединен со вторым входом элемента ИЛИ 12, выход которого соединен с управляющими входами мультиплексоров адреса и управления, со входом элемента НЕ, со вторым управляющим входом первого шинного формирова1еля и является выходом устройства для подключения ко входу разрешения доступа первого процессора.

Сущность изобретения состоит в повышении оперативности обмена информацией путем обеспечения возможности поочередного пословного обмена данными между общей памятью и каждым из сопрягаемых с ней процессоров. Параллельное обслуживание одновременных запросов на обмен данными существенно повышает оперативность обмена данными между процессорами и общей памятью. При одновременном поступлении запросов на обмен информацией устройство предоставляет общую память каждому из процессоров на время передачи одного слова данных. После обмена одним словом данных между одним из процессоров и общей памятью устройство с моментом прихода на сход ус- тройстса очередного тактового импульса обеспечивает возможность обмена одним словом данных между другим процессором и общей памятью. С приходом очередного

тактового импульса устройство переключается на соседний процессор и так далее до момента передачи последних слов данных из массива информации. Таким образом, совмещенное обслуживание двух процессоров при доступе к общей памяти существенно повышает оперативность обмена.

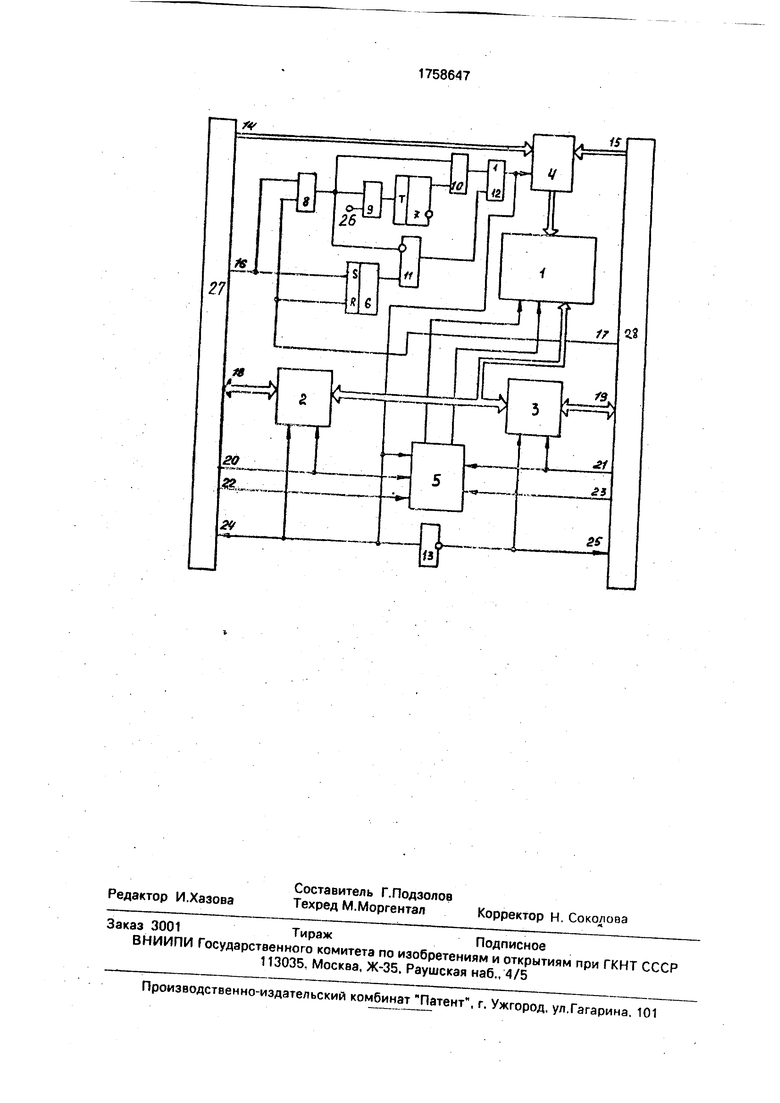

На чертеже представлена функциональ0 ная схема устройства.

Устройство для сопряжения двух процессоров через общую память содержит блок оперативной памяти 1, первый 2, и второй 3 шинные формирователи, мульти5 плексор адреса 4, мультиплексор управления 5, первый триггер 6, второй триггер 7, первый 8. второй 9, третий 10, четвертый 11 элементы И, элемент ИЛИ 12, элемент НЕ 13, входы 14 и 15 для подключения к шинам

0 адреса, входы 16 и 17 для подключения к выходам запроса, входы-выходы 18 и 19 для подключения к шинам данных, входы 20 и 21 для подключения к выходам чтения/записи, входы 22 и 23 для подключения к вы5 ходам управления обменом, выходы 24 и 25 для подключения ко входу разрешения доступа соответственно первого 27 и второго 28 процессоров, синхровход 26 устройства, первый 27 и второй 28 процессоры.

0Первый и второй информационные входы мультиплексора 4 адреса соединены соответственно с входами 14 и 15 устройства для подключения к шинам адреса первого 27 и второго 28 процессоров, выход мульти5 плексора 4 адреса соединен с адресным входом блока 1 оперативной памяти, информационный вход-выход которого соединен с первыми информационными входами-выходами первого 2 и второго 3 шинных форми0 рователей, вторые информационные входы-выходы первого 2 и второго 3 шинных формирователей соединены с входами-выходами 18 и 19 устройства для подключения к шинам данных соответственно первого 27

5 и второго 28 процессоров, входы установки и сброса первого триггера 6 соединены с входами 16 и 17 устройства для подключения соответственно к выходам запроса доступа первого 27 и второго 28 процессоров,

0 первые управляющие входы первого 2 и второго 3 шинных формирователей соединены соответственно с входами 20 и 21 устройства для подключения к выходам чтения/записи первого 27 и второго 28 процессоров, а также

5 с первыми информационными входами мультиплексора 5 управления, вторые информационные входы которого соединены соответственно с входами 22 и 23 устройства для подключения к выходам управления обменом соответственно первого 27 и второго

28 процессоров, выход элемента НЕ 13 соединен со вторым управляющим входом второго 3 шинного формирователя и входом 25 устройства для подключения ко входу разрешения доступа второго 28 процессора, первый и второй выходы мультиплексора 5 управления соединены соответственно с входами чтением-записью и обмена блока 1 оперативной памяти, первый и второй входы первого элемента И 8 соединены соответственно со входами устройства и сброса первого триггера 6, выход первого элемента И 8 соединен с первыми входами второго 9, третьего 10 и четвертого 11 элементов И, синхровход 26 устройства соединен с вторым входом второго элемента 9, выход которого соединен со счетным входом второго триггера 7, выход которого соединен со вторым входом третьего элемента И 10, выход которого соединен с первым входом элемента ИЛИ 12, выход первого триггера 6 соединен со вторым входом четвертого элемента И 11. выход которого соединен со вторым входом элемента ИЛИ 12, выход которого соединен с управляющими входами мультиплексора адреса 4 и управления 5, со входом элемента НЕ 13, со вторым управляющим входом первого шинного формирователя 2 и входом 24 устройства для подключения ко входу разрешения доступа первого 27 процессора.

Назначение основных функциональных элементов устройства состоит в следующем.

Блок 1 оперативной памяти предназначен для хранения программ и данных многопроцессорной вычислительной машины

Шинные формирователи 2 и 3 служат для управления двунаправленной передачей данных между процессорами 27 и 28 и блока 1 оперативной памяти.

Мультиплексор 4 адреса предназначен для коммутации кодов адреса, поступающих от процессоров устройства.

Мультиплексор 5 управления служит для коммутации управляющих сигналов, обеспечивающих управление режимами работы блока 1 оперативной памяти.

Триггер 6 предназначен для управления работой устройства в режиме одиночного доступа к оперативной памяти.

Триггер 7 предназначен для формирования управляющих сигналов в режиме группового доступа.

Элементы И 8, И 9, И 10, И 11, элемент ИЛИ 12 и элемент НЕ 13 предназначены для формирования управляющих сигналов во всех режимах функционирования устройства.

Работа устройства для сопряжения двух процессоров через общую память возможна в двух режимах: режим одиночного доступа к оперативной памяти; режим группового

доступа к оперативной памяти,

В исходном состоянии триггеры 6, 7 устройства находятся в нулевом состоянии. Цепи установки исходного состояния условно не показаны.

0 Работа устройства в режиме одиночного доступа к оперативной памяти.

Работа устройства в этом режиме начинается с момента выдачи одним из процессоров сигнала запроса доступа к

5 оперативной памяти на вход 16 или 17 устройства. Процессор, обращающийся к оперативной памяти, формирует сигнал запроса доступа на входе 16 устройства, обеспечивая переключение триггера 6 в

0 единичное состояние и разрешая прохождение адреса процессора 27 по входу 14 устройства через мультиплексор 4 адреса на адресный вход блока 1 оперативной памяти Одновременно обеспечивается включение в

5 работу первого шинного формирователя 2 и коммутация мультиплексора 5 управления. Следует отметить, что единичный и нулевой сигналы на выходе элемента ИЛИ 12 обеспечивают прохождение кода адреса через

0 мультиплексор 4 адреса соответственно от первого и второго процессоров. При поступлении с входов 16 и 17 устройства соответственно единичного и нулевого сигналов на входы элемента И 8 на выходе элемента И 8

5 формируется нулевой сигнал, поступающий на инверсный вход элемента И 11. Нулевой сигнал на инверсном входе элемента И 11 разрешает прохождение единичного сигнала с выхода триггера 6 через элемент И 11 и

0 элемент ИЛИ 12 на управляющий вход мультиплексора 4 адреса.

Процессор 27, получив сигнал разрешения доступа с выхода 24 устройства, формирует сигнал на входах 20, 22 устройства,

5 выбирая направление коммутации первого шинного формирователя 2 и обеспечивая управление режимом работы блока 1 оперативной памяти (записью или считыванием информации). Единичный сигнал на

0 управляющем входе мультиплексора 5 управления обеспечивает прохождение управляющих сигналов с выходов 20, 33 через мультиплексор 5 управления на входы чтения-записи и обмена блока 1 оперативной

5 памяти. По завершении цикла работы с блоком 1 оперативной памяти процессор 27 снимает сигнал со входа 16 запроса доступа к блоку 1 оперативной памяти. Устройство готово к обслуживанию запросов от любого процессора.

При обращении к блоку 1 оперативной памяти второго процессора 28 устройство функционирует аналогично. Триггер 6 пере- оодится в нулевое состояние (или подтверждает нулевое состояние). Нулевой сигнал на инверсном входе элемента И 11 обеспечивает прохождение нулевого сигнала с выхода триггера 6 через элементы И 11 и ИЛИ 12 на управляющие входы мультиплексора 4 адреса и мультиплексора 5 управления. При этом на выходе элемента НЕ 13 формируется единичный сигнал, который включает в работу шинный формирователь 3.

Работа устройства в режиме группового доступа к оперативной памяти.

При одновременном поступлении сигналов запросов доступа на входах 16 и 17 устройства к блоку 1 оперативной памяти на выходе элемента ИЛИ 12 поочередно формируются нулевые и единичные сигналы одновременно с поступлением на синхровход 26 устройства тактовых импульсов. На выходе элемента И 8 формируется единичный сигнал, запрещающий прохождение сигналов с выхода триггера 6 через элемент И 11 и разрешающий прохождение сигналов с выхода триггера 7 через элемент И 10, а также тактовых импульсов с синхровхода 26 устройства через элемент И 9 на счетный вход триггера 7. Состояние триггера 7 определяет очередность пословного обмена данными между процессорами. Изменение состояния триггера 7 происходит с очередным поступлением тактового импульса на синхровход 26 устройства. Настройка на работу мультиплексора 4 адреса, мультиплексора 5 управления, шинных формирователей 2 и 3 осуществляется аналогично режиму одиночного доступа. Таким образом, обеспечивается одновременный обмен данными двух процессоров с блоком 1 оперативной памяти.

После передачи массива данных одним из процессоров устройство переходит в режим одиночного доступа к оперативной памяти.

Формула изобретения

Устройство для сопряжения двух процессоров через общую память, содержащее блок оперативной памяти, первый и второй шинные формирователи, мультиплексор адреса, мультиплексор управления, первый триггер, элемент НЕ, причем первый и второй информационные входы мультиплексора адреса соединены соответственно с входами устройства для подключения к шинам адреса первого и второго процессоров,

выход мультиплексора адреса соединен с адресным входом блока оперативной памяти, информационный вход-выход которого соединен с первыми информационными

входами-выходами первого и второго шинных формирователей, вторые информационные входы-выходы которых являются входами-выходами устройства для подключения к шинам данных первого и второго

процессоров, входы установки и сброса первого триггера являются входами устройства для подключения соответственно к выходам запроса доступа первого и второго процессоров, первые управляющие входы первого

и второго шинных формирователей являются входами устройства для подключения соответственно к выходам чтения-записи первого и второго процессоров и соединены с первыми информационными входами

мультиплексора управления, вторые информационные входы которого являются входами устройства для подключения к выходам управления обменом соответственно первого и второго процессоров, выход элемента

НЕ соединен с вторым управляющим входом второго шинного формирователя и является выходом устройства для подключения к входу разрешения доступа второго процессора, первый и второй выходы мультиплексорауправления соединены соответственно с входами чтения-записи и обмена блока оперативной памяти, отличающееся тем, что, с целью повышения оперативности обмена информацией, в него введены второй триггер, с первого по четвертый элементы И, элемент ИЛИ, причем первый и второй входы первого элемента И объединены соответственно с входами установки и сброса первого триггера, выход первого элемента

И соединен с первыми входами второго, третьего и четвертого элементов И, второй вход второго элемента И является синхров- ходом устройства, а выход соединен со счет- ным входом второго триггера, выход

которого соединен с вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, выход первого триггера соединен с вторым входом четвертого элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с управляющими входами мультиплексоров адреса и управления, с входом элемента НЕ с вторым управляющим входом первого шинного

формирователя и является выходом устройства для подключения к входу разрешения доступа первого процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух процессоров | 1991 |

|

SU1784983A1 |

| Устройство для сопряжения двух процессоров через общую память | 1987 |

|

SU1515172A1 |

| Устройство для обмена данными двух процессоров через общую память | 1990 |

|

SU1778759A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных машин. Цель изобретения состоит в повышении оперативности обмена информацией путем обеспечения возможности поочередного пословного обмена данными между общей памятью и каждым из сопрягаемых с ней процессоров. Параллельное Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных машин. Известно устройство, содержащее блок памяти, мультиплексор, триггер, шинный формирователь. Недостатком указанного аналога является ограниченные функциональные возможности, вызванные отсутствием средств двустороннего обмена информацией между оперативной памятью и каждым из сопрягаемых с ней процессоров. обслуживание одновременных запросов на обмен данными существенно повышает оперативность обмена данными между процессорами и общей памятью. При одновременном поступлении запросов на обмен информацией устройство предоставляет общую память каждому из процессоров на время передачи одного слова данных. После обмена одним словом данных между одним из процессоров и общей памятью устройство с моментом перехода на вход устройства очередного тактового импульса обеспечивает возможность обмена одним словом данных между другим процессором и общей памятью. С приходом очередного тактового импульса устройство переключается на соседний процессор и так далее до момента передачи последних слов данных из массивов информации. Устройство содержит блок оперативной памяти, первый и второй шинные формирователи, мультиплексор адреса, мультиплексор управления, первый и второй триггеры, элемент НЕ, четыре элемента И, элемент ИЛИ. 1 ил. Из известных устройств наиболее близким к изобретению по технической сущности и достигаемому положительному эффекту является устройство для сопряжения двух процессоров через общую память, содержащее блок оперативной памяти, мультиплексор адреса, первый шинный формирователь, триггер, второй шинный формирователь, мультиплексор управления оперативной памятью и элемент НЕ. причем первый и второй информационные входы мультиплексора адреса соединены с адресными выходами соответственно первого и СП ел 00 о 4

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух процессоров через общую память | 1987 |

|

SU1515172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-30—Публикация

1990-10-15—Подача