1

Изобретение относится к области вычислительной техники и может быть использовано в устройствах обработ ки массивов чисел.

Целью изобретения является сокрещение аппаратурных затрат в ас социативном суммирующем устройстве.

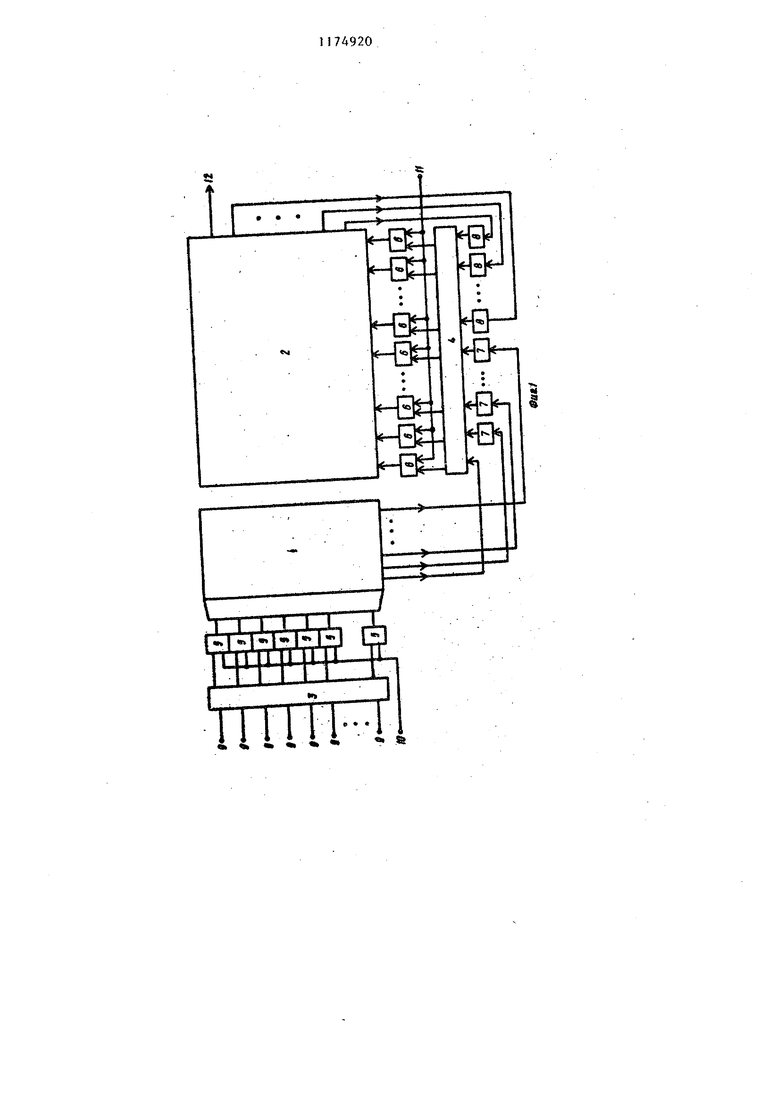

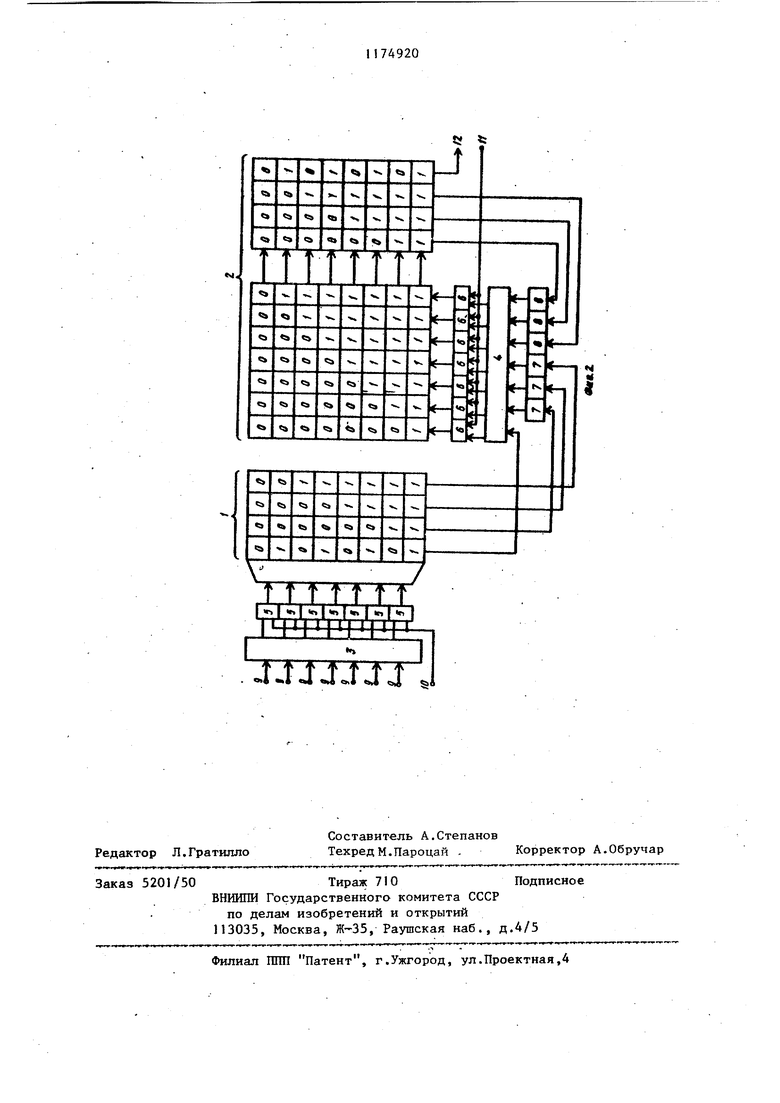

На фиг.1 представлена структурная схема ассоциативного суммирующего устройства; на фиг.2 - размв щение информации в постоянном и ассоциативном запоминающих блоках для случая суммирования семи операндов .

Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, преобразовател 3 и 4 двоичного кода в уплотненный код, группы элементов И и 6, группы элементов 7 и 8 задержки, ин-формационные входы 9, входы 10 и П синхронизации и выход 12 суммы.

Устройство работает следующим образом.

На входы 9 поступают однотмен-ные разряды всех слагаемых, начиная с младших разрядов. Преобразователь 3 преобразует поступающий на его входы двоичный код в уплотненный код, который через элементы И 5 поступает на адресный вход запоми-нающего блока 1 в течение тактового импульса по входу 10. Считанное из блока 1 слово является частью ассо-циативного признака для ассоциативного запоминающего блока 2. Второй частью признака являются, все , кроме первого, разряды кода, считанного из блока 2. Обе части признака поступают на преобразователь двоичного код в уплотненный код 4 через элементы 7 и 8 задержки, причем младший разряд слова, считанного из блока 1 , поступает на преобра,- зователь 4 без задержки. Сформированный на выходе преобразователя 4 признак дополнительно синхронизи- руется импульсом по входу 11 с помощью элементов И 6. Такая сиихро низация исключает влияние неидеальиости элементов 7 и 8 задерж-- . ки. На выходе 12 формируется очередной разряд суммы,, Общее число такто вычисления суммы равно

n

m

где п -разрядность слагаемых; Н - количество слагаемых.

49202

Пусть необходимо просуммировать следующие семь слагаемых: 010110; 101011; 011011; 111111 ; 101110; 110011 ; lOlOiO. Обрабатьюаемые срезы иа входе преобразователя 3 имеют вид 0111010; 1111111; 1001100;0111101; 1011010; 0101111.

На выходе преобразователя 3 обрабатьгоаемые срезы имеют вид 0001111; 1111111; 0000111;0011111; 00011 И; 0011111 .

В течение первого тактового импульса, поданного на вход 10 синхронизации, на адресный вход блока 1 подаются с выхода преобразователя 3 младшие разряды слагаемых, т.е. адрес 00011П..

По указанному адресу из блока 1 считывается в том же такте слово ООП, первый разряд которого без задержки подается на первый вход преобразователя 4, а остальные через элементы 7 задержки - на соответствующие входы того же преобразователя. Так как в первом такте из блока 2 ничего не считывается, то к приходу первого испульса по входу 1I синхронизации на все входы преобразователя

0 4 подаются нули.

Сформированный признак с выхода преобразователя 4 кода - ООООООО, с приходом тактового импульса по входу 1. поступает на признаковые входы

5 блока 2. Следовательно, в первом такте из блока 2 считывается слово 0000, первый разряд которого О является младшим разрядом искомой суммы.

В течение второго импульса, подан0 кого на вход 10 синхронизации, на вход адреса 1 с выхода преобразователя 3 подается второй разрядный срез слагаемых, т.е. адрес 1111111. По указанному адресу из блока 1

5 считывается слово 1111. На входе преобразователя 4 формируется слово 1011000 соответственно на его выходе 0000111, которое по приходу импульса по входу 11 поступает на признаковые входы блока 2, из которого считьшается слово ООП, первый разряд которого 1 является вторым разря- дом искомой суммы.

В течение третьего импульса, поданного на вход 10 синхронизации, на вход адреса блока 1 с выхода преобразователя 3 подается третий обрабатываемый срез 0000111.

По указанному адресу из блока 1 считывается слово 1001. На входе преобразователя 4 формируется слово 1I11001, соответственно на его выходе 0011111 , которое при приходу импульса по входу 11 поступает на признаковый вход блока 2, из которого считьтается слово 0111, первый

11749204

разряд которого 1 является третьим разрядом искомой суммы.

Аналогичным образом предлагаемое устройство продолжает работу до получения десятого разряда суммы. Код суммы при этом 100-100110. В восьмом и девятом тактах на вход преобразователя 3 поступают нулевые коды.

ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1987 |

|

SU1495784A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

АССОЦИАТИВНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО, содержащее ассоциативный запоминающий блок, постоянный запоминающий блок, первую и вторую группы элементов И, первую и вторую груп пы элементов задержки, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И первой группы, первые входы которых подключены к первому входу синхронизации устройства, первый разрядный выход ассоциативного запоминающего блока соединен с выходом суммы устройства, а остальные разрязные выходы подключены к входам соответствующих эле ментов задержки первой группы, выходы элементов И второй группы подключены к соответствующим входам опроса ассоциативного запоминающего блока, первые входы элементов И второй группы соединены с вторым входом синхронизации устройства, разрядные выходы постоянного запоминающед о блока, кроме выхода младшего разря да, соединены с входами соответствующих элементов задержки второй группы, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит первый и второй преобразователи двоичного кода уплотненный код, причем входы первого преобразователя (Л двоичного кода, уплотненный код соединен -с входами слагаемых устройства , а выходы подключены к вторым входам соответствующих элементов И первой группы, входы второго преобразователя двоичного кода в уплотненный код соединены соответственно с выходом младшего разряда постоянно4;: го запоминающего блока, с выходами СО ND элементов задержки первой группы и с выходами элементов задержки второй группы, а выходы подключены к .вторым входам соответствующих элементов И второй группы.

J ,1.1 J .1 .JT

1Э6НЭЭЭ

Ml и 11 11 tL

I

11 I I II- V I

«te Ч

дллзхи

iSEEEEEIEj

ттутругдт

I1 .

. O.IJJJJJJ ,

N I

| Кохонен Т | |||

| Ассоциативная память | |||

| М: Мир , 1980, с.20, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-23—Публикация

1983-08-12—Подача