Изобретение относится к вычислительной технике и может быть использовано для построения систем памяти повышенной надежности.

Известно устройство, содержащее два модуля памяти, дешифратор и два элемента. 2 И 1. Запись информации производится одновременно в оба модуля памяти, что обеспечивает идентичность хранимой в них информации. Считывается информация только из одного модуля памяти. При ее отказе считывание производится из второго модуля памяти. Недостатком устройства является отсутствие встроенных средств контроля, что требует дополнительного времени на проверку истинности считанной информации и переключения на другой модуль памяти в случае выявления ошибки.

Наиболее близким к предложенному устройству является устройство, содержащее два модуля памяти, блоки контроля, коммутатор, входные шины, выходные шины, выходную шину сигнала ошибки, причем выходы модулей памяти соединены с выходной шиной через коммутатор, управляемый блоками контроля 2.

В указанном устройстве осуществляется запись входной информации в оба модуля памяти параллельно. Считывание производится с выхода одного из модулей памяти через коммутатор. В случае обнаружения блоком контроля ошибки в данном модуле памяти коммутатор переключает выходную шину на второй накопитель, а на выходной шине сигнала ошибки появляется соответствующий сигнал.

О (Я 41

го

Недостатком этого устройства является то, что при возникновении отказа локализация неисправности в нем затруднена вследствие невозможности раздельной проверки модулей памяти, а также невозможности проверки средств контроля.

Целью изобретения является повышение достоверности диагностирования резервированного запоминающего устройства за счет обеспечения независимого тестирования всех элементов системы.

Указанная цель достигается тем, что в устройство, содержащее первый и второй модули памяти, входы адреса, данных и управления записью - чтением которых соеди- нены соответственно с общими для них входными шинами адреса, данных и управления записью-чтением, информационные выходы первого и второго модулей памяти являются входами соответственно первого и второго блоков контроля и соответственно первым и вторым информационными входами коммутатора, выходом которого является выходная информационная шина, введены дешифратор и блок управления коммутацией, причем первый и второй входы дешифратора соединены соответственно с первым и вторым выходами шины управления режимами работы устройства, первый, второй и третий выходы дешифратора являются соответственно первым, вторым и третьим входами блока управления коммутатором, четвертый выход дешифратора соединен со входами управления блоков контроля, выходы которых соединены с четвертым и пятым входами блока управления коммутацией, первый и второй выходы которого являются управляющими входами коммутатора, третий выход блока управления коммутатором является выходом сигнала ошибки устройства,

Сопоставительный анализ с прототипом показывает, что данное устройство отличается наличием новых блоков: дешифратора и блока управления коммутатором и их связями с остальными элементами схемы. Таким образом, данное устройство соответствует критерию новизна.

Сравнение заявляемого решения с другими техническими решениями показывает, что предложенное устройство обладает новым техническим свойством, заключающимся в повышении достоверности диагностирования резервированного запоминающего устройства за счет раздельной проверки накопителей и средств самоконтроля. Следовательно, данное техническое решение соответствует критерию существенные отличия.

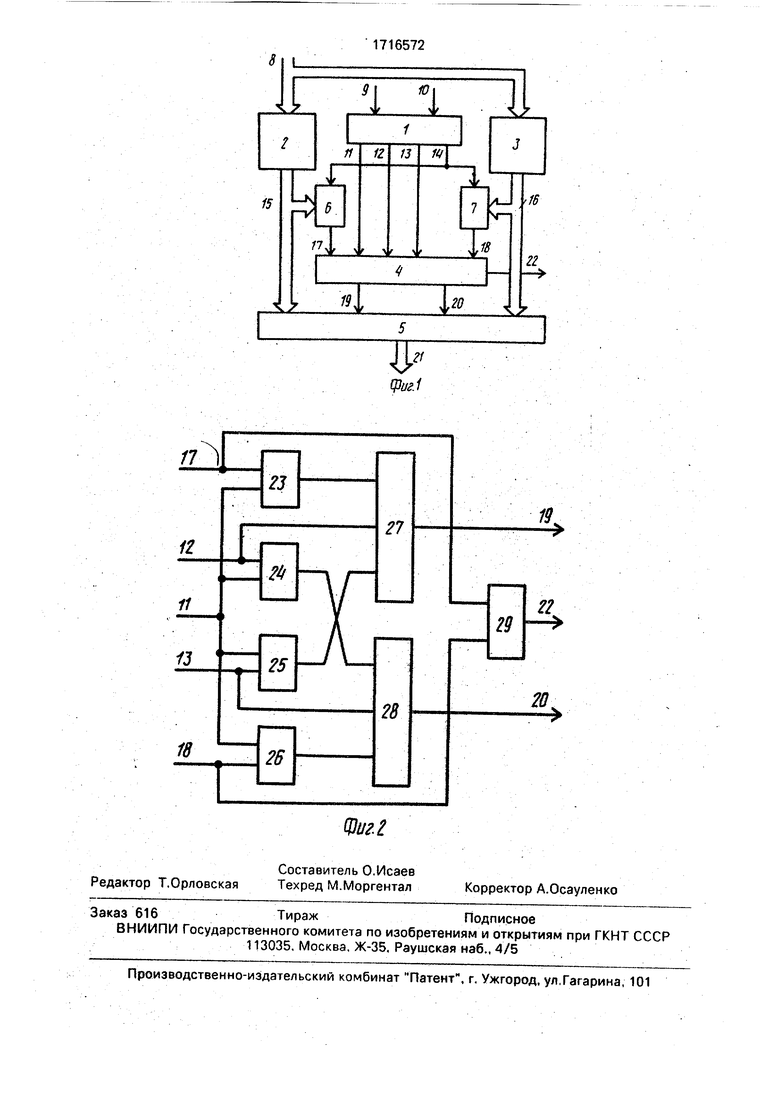

На фиг.1 изображена схема резервированного запоминающего устройства; на фиг.2 - пример реализации блока управления коммутатором.

Устройство (фиг.1) содержит дешифратор 1, первый и второй модули памяти 2,3, блок управления л коммутатором, коммутатор 5, первый и второй блоки контроля 6,7, входную информационную, адресную и уп0 равляющую шину записи - чтения 8, первый 9 и второй 10 входы управления режимами работы, первый - четвертый 11-14 выходы дешифратора, выходные шины 15,16 первого и второго модулей памяти, выходы 17,18

5 первого и второго блоков контроля, первый и второй выходы 19,20 блока управления коммутатором, выходную шину 21 устройства, выход 22 сигнала ошибки.

Блок управления 4 коммутатором (фиг.2) (

0 содежит элемент 2 ИЛИ 23, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24,25, элемент 2ИЛИ 26, два элемента ЗИ 27,28, элемент 2И 29. Блок управления коммутатором по входам 11,12,13 подключен к первому, второму и

5 третьему выходам дешифратора 1, по входам 17, 18 - к выходам первого и второго блоков 6,7, по выходам 19,20 - к входам управления коммутатора 5, по выходу 22 - к выходу сигнала ошибки устройства.

0

Устройство работает в четырех режимах в зависимости от сигналов на входах управления 9,10 режимами работы устройства. Запись информации в модули памяти во

5 всех четырех режимах происходит следующим образом. По шине 8 в устройство посту- ; пает адрес и управляющая информация, а также данные, которые записываются параллельно в оба модуля памяти. Процедура

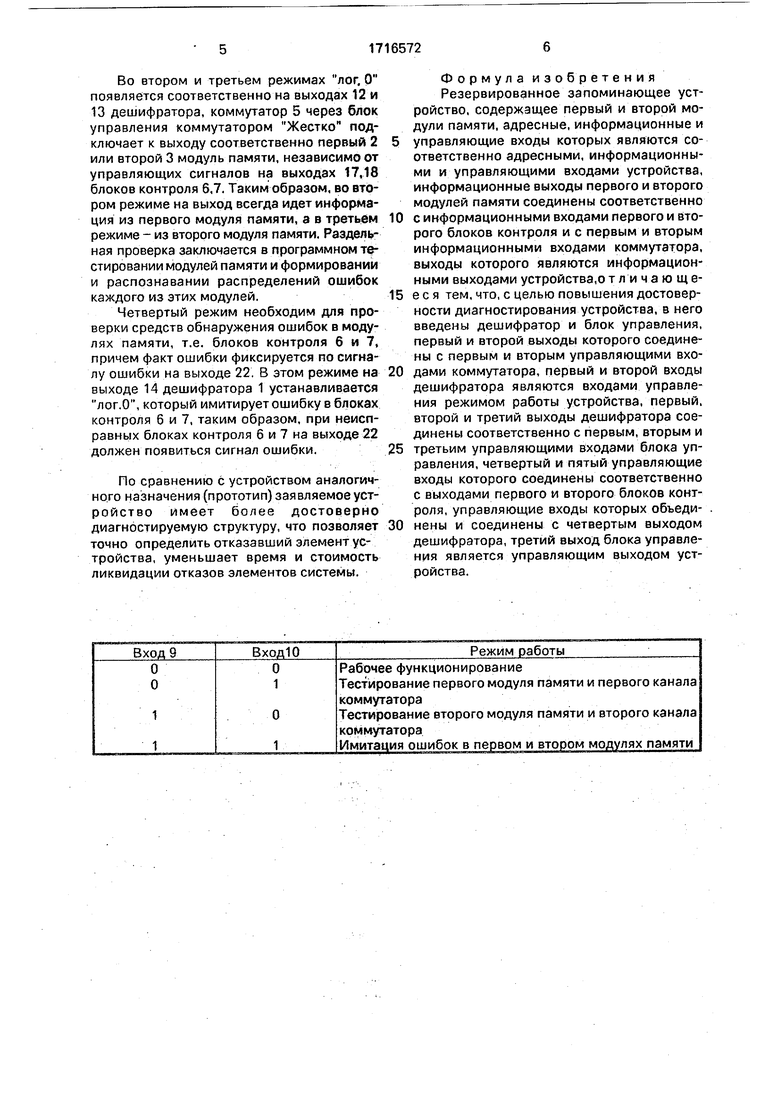

0 считывания зависит от режима, в котором работает устройство. Списывание режимов работы приведено в таблице.

В первом режиме на выходе 11 дешифратора 1 устанавливается лог.О и блок уп5 равления 4 коммутатором пропускает через элементы 23,27 и 26,28управляющие сигналы от блоков контроля 6,7 на входы 19,20 коммутатора. При появлении ошибки в одном из модулей на выходе соответствующе0 го ему блока контроля появится сигнал ошибки (уровень лот. Ч). Если сигнал ошибки пришел от блока контроля того модуля, который подключен к выходу 21 устройства, то коммутатор подключит к выходу

5 устройства другой модуль памяти, В случае ошибки в неподключенном модуле переключения не происходит. При одновременной ошибке в обоих модулях памяти на выходе 22 элемента 2И 29 появится сигнал ошибки (уровень лог.1).

Во втором и третьем режимах лог. О появляется соответственно на выходах 12 и 13 дешифратора, коммутатор 5 через блок управления коммутатором Жестко подключает к выходу соответственно первый 2 или второй 3 модуль памяти, независимо от управляющих сигналов на выходах 17,18 блоков контроля 6,7. Таким образом, во втором режиме на выход всегда идет информация из первого модуля памяти, а в третьем режиме - из второго модуля памяти. Раздельная проверка заключается в программном тестировании модулей памяти и формировании и распознавании распределений ошибок каждого из этих модулей.

Четвертый режим необходим для проверки средств обнаружения ошибок в модулях памяти, т.е. блоков контроля 6 и 7, причем факт ошибки фиксируется по сигналу ошибки на выходе 22. В этом режиме на выходе 14 дешифратора 1 устанавливается лог.О, который имитирует ошибку в блоках контроля 6 и 7, таким образом, при неисправных блоках контроля 6 и 7 на выходе 22 должен появиться сигнал ошибки.

По сравнению с устройством аналогичного назначения (прототип) заявляемое устройство имеет более достоверно диагностируемую структуру, что позволяет точно определить отказавший элемент устройства, уменьшает время и стоимость ликвидации отказов элементов системы.

Формула изобретения Резервированное запоминающее устройство, содержащее первый и второй модули памяти, адресные, информационные и управляющие входы которых являются соответственно адресными, информационными и управляющими входами устройства, информационные выходы первого и второго модулей памяти соединены соответственно с информационными входами первого и второго блоков контроля и с первым и вторым информационными входами коммутатора, выходы которого являются информационными выходами устройства,о т л и ч а ю щ е- е с я тем, что, с целью повышения достоверности диагностирования устройства, в него введены дешифратор и блок управления, первый и второй выходы которого соединены с первым и вторым управляющими входами коммутатора, первый и второй входы дешифратора являются входами управления режимом работы устройства, первый, второй и третий выходы дешифратора соединены соответственно с первым, вторым и третьим управляющими входами блока управления, четвертый и пятый управляющие входы которого соединены соответственно с выходами первого и второго блоков контроля, управляющие входы которых объединены и соединены с четвертым выходом дешифратора, третий выход блока управления является управляющим выходом устройства.

I 1 1 it

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для диагностирования троированных дискретных схем автоматики | 1990 |

|

SU1772783A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения систем памяти повышенной надежности. Целью изобретения является повышение достоверности диагностирования резервированного запоминающего устройства за счет обеспечения независимого тес- тирования всех элементов системы. Устройство содержит дешифратор 1. первый 2 и второй 3 модули памяти, блок управления 4 коммутатором, коммутатор 5, первый б и второй 7 блоки контроля. Цель изобретения достигается тем, что в схему резервированного запоминающего устройства вводятся дешифратор и блок управления коммутатором, с помощью которых становится возможным раздельное тестирование каждого из модулей памяти, а также проверка встроенных блоков контроля. 2 ил., 1 табл,

fl

15

-V

Г7,

5 Л

#v

12

13

It/

rhJ

16

18

22

w.

О

&

фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Огнев И.В., Сарычев К.Ф | |||

| Надёжность запоминающих устройств | |||

| М.: Радио и связь, 1988, с.153 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1001174A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-02-28—Публикация

1989-12-19—Подача