VI 00 00

низации, а адресные входы мультиплексора и обоих блоков памяти данных - к соответствующим адресным выходам программируемого контроллера 10. В цикле опроса входов программируемого контроллера 10 при каждом очередном адресе вначале производится считывание информации из обоих блоков памяти данных и фиксация ее в соответствующих запоминающих элементах. Затем производится запись в оба блока памяти данных информации с выхода мультиплексора, причем во второй блок памяти данных запись происходит лишь при условии совпадения

новой информации с информацией, записанной в первый блок памяти данных в предыдущем цикле опроса входов. В противном случае во втором блоке памяти данных остается прежняя запись и она будет выдана на вход данных программируемого контроллера 10. Новым в устройстве является наличие элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, а также их связей между собой и с другими элементами схемы, что исключает прохождение как отдельных, так и периодически повторяющихся сигналов длительностью меньше двух циклов опроса. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Программируемый контроллер | 1988 |

|

SU1583921A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| ЦИФРОВОЕ КОММУТАЦИОННОЕ ПОЛЕ | 1991 |

|

RU2012153C1 |

Изобретение касается автоматического управления производственным оборудованием. Цель изобретения - повышение надежности работы устройства за счет снижения его чувствительности к помехам. Устройство для опроса входов программируемого контроллера содержит мультиплексор 1, первый 2 и второй 4 блоки памяти данных, первый 3 и второй 5 запоминающие элементы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ б и элемент И 7. Информационные входы мультиплексора через элементы 8 согласования соединены с датчиками сигналов объекта 9 управления. Входы записи обоих запоминающих элементов, входы выборки обоих блоков памяти данных и один вход элемента И подключены к выходам синхросо с

Изобретение относится к регулирующим системам, к автоматике и вычислитель- ной технике и предназначено для использования в программируемых контроллерах, управляющих производственным оборудованием.

Известно устройство для опроса входов, содержащее мультиплексор, информационные входы которого через элементы согласования (входной формирователь) подключены к информационным входам устройства, адресные входы подключены к ад- ресным выходам программируемого контроллера, а выход соединен с входом данных последнего. Устройство работает в составе программируемого контроллера. При опросе входов поступающие с адресных выходов контроллера адреса вызывают соединение соответствующих опрашиваемых входов с выходом мультиплексора, откуда информация о состоянии входов поступает на вход данных программируемого контроллера. Защита от помех осуществ- лятся элементами согласования, в основном, путем гальванического разделения внутренних цепей устройства от источников сигналов объекта 1.

Однако такая защита во многих случаях является недостаточной. Применение же для входов индивидуальных, достаточно эффективных фильтров делает устройство слишком громоздким и дорогим.

Наиболее близким по технической сущности к предлагаемому является устройство для опроса входов в составе программируемого контроллера, содержащее мультиплексор, информационные входы которого через элементы согласования подключены к информационным входам устройства, первый блок памяти данных (первый канал ЗУ), информационный вход которого соединен с выходом мультиплексора, первый запоминающий элемент (первый канал регистра

памяти), информационный вход которого соединен с выходом первого блока памяти данных, второй блок памяти данных (второй канал ЗУ), адресные входы которого соединены с соответствующими входами первого блока памяти данных и соответствующими адресными входами мультиплексора и подключены к соответствующим адресным выходам программируемого контроллера,

второй запоминающий элемент (второй канал регистра памяти), информационный вход которого соединен с выходом второго блока памяти данных, первый выход синхронизации программируемого контроллера

подключен к входам выборки первого и второго блоков памяти данных, второй выход соединен с входом записи первого и второго запоминающих элементов, а третий выход синхронизации подключен к входу

управления записью-считыванием первого блока памяти данных. Устройство содержит также мажоритарный элемент. При опросе входов поступающие с адресных выходов программируемого контроллера последовательно изменяющиеся адреса вызывают поочередное соединение опрашиваемых входов с выходом мультиплексора, откуда сигналы поступают на один из входов мажоритарного элемента. Два других входа мажоритарного элемента соединены с выходами обоих запоминающих элементов, на которых присутствуют сигналы тех же входов, записанные в двух предыдущих циклах опроса. Информационным входом устройства является выход мажоритарного элемента, соединенный с входом данных программируемого контроллера. Сигнал на нем всегда совпадает с одинаковыми сигналами на двух любых входах мажоритарного элемента. Таким образом исключаются отдельные случайные искажения входных сигналов, длящиеся менее двух циклов опроса 2,

Недостатком известного устройства является отсутствие у него устойчивости к им- пульсным помехам, повторяющимся с частотой в два раза ниже частоты повторений циклов опроса входов, так как в этом случае на входы мажоритарного элемента поступают пары сигналов, одинаковых между собой, но противоположных уровней в смежных циклах опроса входов контроллера. У большинства современных программируемых контроллеров частота повторений циклов опроса входов находится в пределах 50-500 Гц. Применительно к ним для известного устройства опасная чд- стота повторяющихся помех может быть в пределах 25-250 Гц. Такие помехи вполне вероятны, источниками их могут быть сеть переменного тока, электрические разряды, сварки, мощные тиристорные выпрямители и преобразователи и др.

Целью изобретения является повышение надежности устройства для опроса входов путем уменьшения чувствительности к влиянию помех на правильный прием информации.

Повышение помехоустойчивости устройства для опроса входов позволяет расширитьобластьпримененияпрограммируемых контроллеров, что может дать значительный эффект.

Указанная цель достигается тем, что устройство для опроса входов программируе- мого контроллера, содержащее мультиплексор, информационные входы которого через элементы согласования подключены к информационным входам устройства, первый блок памяти данных, информационный вход которого соединен с выходом мультиплексора, первый запоминающий элемент, информационный вход которого соединен с выходом первого блока памяти данных, второй блок памяти данных, адресные входы которого соединены с соответствующими входами первого блока памяти данных и соответствующими адресными входами мультиплексора и подключены к соответствующим адресным выходам программируемого контроллера, второй запоминающий элемент, информационный вход которого соединен с выходом второго блока памяти данных, первый выход синхронизации программируемого контроллера подключен к входам выборки первого и второго блоков памяти данных, второй выход синхронизации соединен с входом записи первого и второго запоминающих элементов, а третий выход синхронизации подключен к входу управления записью-считыванием первого блока памяти данных, содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. и элемент И, выход которого со- 5 единен с входом управления записью-считыванием второго блока памяти данных, первый вход подключен к входу управления записью-считыванием первого блока памяти данных, а второй вход подключен к выхо- 0 ду элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с инверсным выходом первого запоминающего элемента, второй вход - с выходом мультиплексора и с информационным вхо- 5 дом второго блок памяти данных, а выход второго запоминающего элемента соединен с входом данных программируемого контроллера.

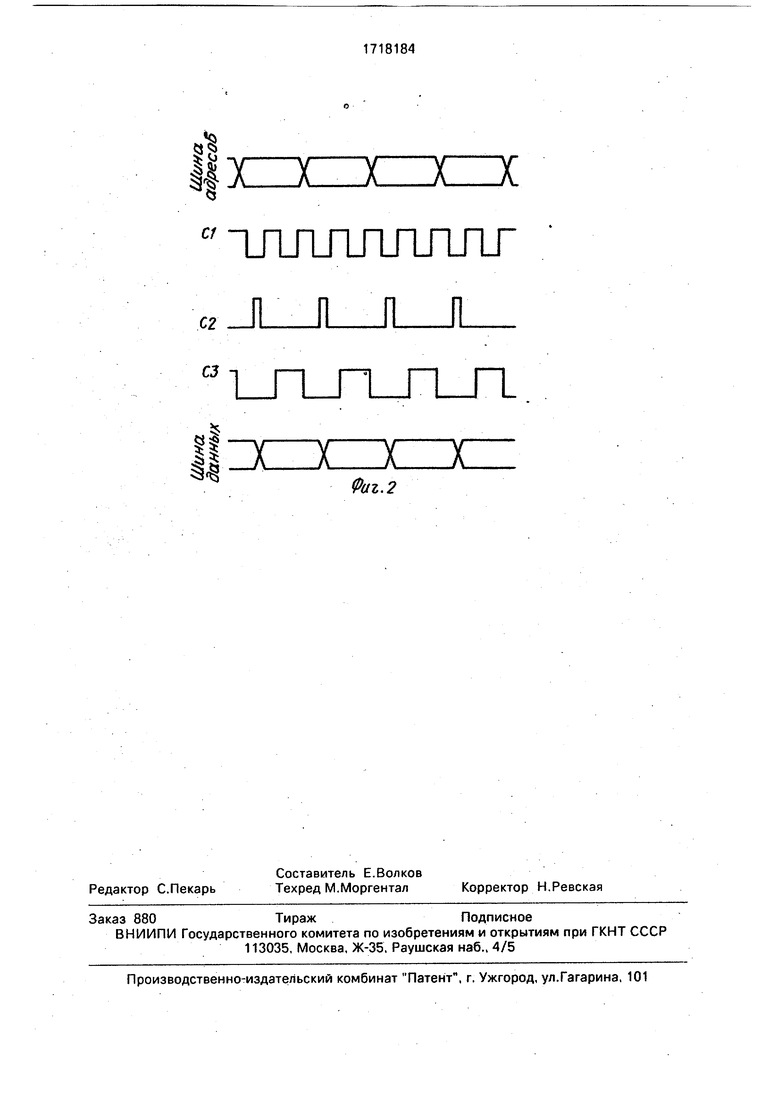

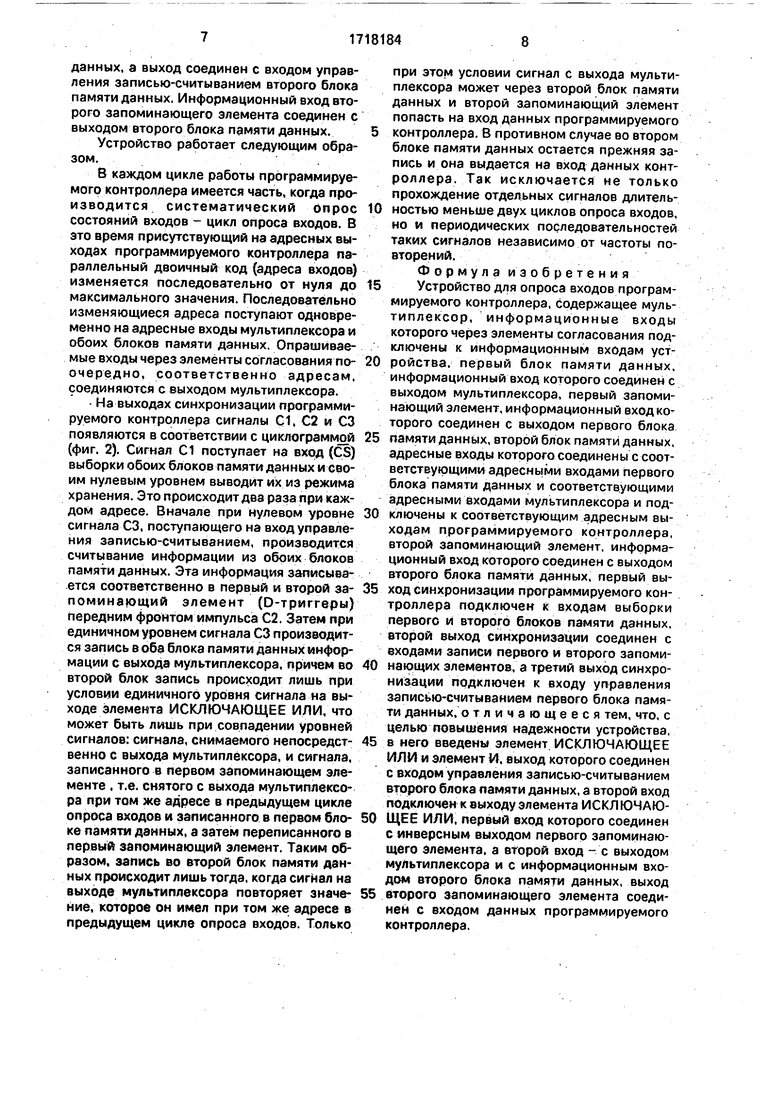

На фиг. 1 показана функциональная схема устройства; на фиг. 2 - циклограмма его работы.

Устройство содержит мультиплексор 1, первый блок 2 памяти данных, первый запоминающий элемент 3, второй блок 4 памяти данных, второй запоминающий элемент 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и элемент И 7. Информационные входы мультиплексора через элементы 8 согласования подключены к информационным входам устройства, соединенным с датчиками сигналов объекта 9 управления. Элементы согласования осуществляют гальваническую развязку цепей объекта и устройства для опроса входов и согласование уровней их сигналов. Они могут быть построены, например, на основе оптронов. Адресные входы мультиплексора и обоих блоков памяти данных соединены между собой соответственно параллельно и подключены к адресным выходам программируемого контроллера 10, а выход второго запоминающего элемента - к входу данных программируемого контроллера. Первый выход синхронизации (С1) программируемого контроллера 10 подключен к входам выборки первого и второго блоков памяти данных, второй выход синхронизации (С2)соединен с входом записи первого и второго запоминающих элементов, а третий выход синхронизации (СЗ) под- ключен к входу управления записью-считыванием первого блока памяти данных. Информационный вход первого запоминающего элемента соединен с выходом первого блока памяти данных, а инверсный выход - с одним из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Другой вход этого элемента подключен к соединенным между собой информационным входам первого и второго блоков памяти данных и выходу мультиплексора, а выход соединен с одним из входов элемента И. Другой вход элемента И подключен к входу управления записью-считыванием первого блока памяти

данных, а выход соединен с входом управления записью-считыванием второго блока памяти данных, Информационный вход второго запоминающего элемента соединен с выходом второго блока памяти данных.

Устройство работает следующим образом..

В каждом цикле работы программируемого контроллера имеется часть, когда про- изводится систематический опрос состояний входов - цикл опроса входов. В это время присутствующий на адресных выходах программируемого контроллера параллельный двоичный код (адреса входов) изменяется последовательно от нуля до максимального значения. Последовательно изменяющиеся адреса поступают одновременно на адресные входы мультиплексора и обоих блоков памяти данных. Опрашиваемые входы через элементы согласования поочередно, соответственно адресам, соединяются с выходом мультиплексора.

На выходах синхронизации программируемого контроллера сигналы С1, С2 и СЗ появляются в соответствии с циклограммой (фиг. 2). Сигнал С1 поступает на вход (CS) выборки обоих блоков памяти данных и своим нулевым уровнем выводит их из режима хранения. Это происходит два раза при каждом адресе. Вначале при нулевом уровне сигнала СЗ, поступающего на вход управления записью-считыванием, производится считывание информации из обоих блоков памяти данных. Эта информация записывается соответственно в первый и второй запоминающий элемент (D-триггеры) передним фронтом импульса С2. Затем при единичном уровнем сигнала СЗ производится запись в оба блока памяти данных информации с выхода мультиплексора, причем во второй блок запись происходит лишь при условии единичного уровня сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, что может быть лишь при совладении уровней сигналов: сигнала, снимаемого непосредственно с выхода мультиплексора, и сигнала, записанного в первом запоминающем элементе , т.е. снятого с выхода мультиплексора при том же адресе в предыдущем цикле опроса входов и записанного в первом блоке памяти данных, а затем переписанного в первый запоминающий элемент. Таким образом, запись во второй блок памяти данных происходит лишь тогда, когда сигнал на выходе мультиплексора повторяет значение, которое он имел при том же адресе в предыдущем цикле опроса входов. Только

при этом условии сигнал с выхода мультиплексора может через второй блок памяти данных и второй запоминающий элемент попасть на вход данных программируемого

контроллера. В противном случае во втором блоке памяти данных остается прежняя запись и она выдается на вход данных контроллера. Так исключается не только прохождение отдельных сигналов длительностью меньше двух циклов опроса входов, но и периодических последовательностей таких сигналов независимо от частоты повторений.

Формула изобретения

Устройство для опроса входов программируемого контроллера, содержащее мультиплексор, информационные входы которого через элементы согласования подключены к информационным входам устройства, первый блок памяти данных, информационный вход которого соединен с выходом мультиплексора, первый запоминающий элемент, информационный вход которого соединен с выходом первого блока

памяти данных, второй блок памяти данных, адресные входы которого соединены с соответствующими адресными входами первого блока памяти данных и соответствующими адресными входами мультиплексора и подключены к соответствующим адресным выходам программируемого контроллера, второй запоминающий элемент, информационный вход которого соединен с выходом второго блока памяти данных, первый выход синхронизации программируемого контроллера подключен к входам выборки первого и второго блоков памяти данных, второй выход синхронизации соединен с входами записи первого и второго запоминающих элементов, а третий выход синхронизации подключен к входу управления записью-считыванием первого блока памяти данных, отличающееся тем, что, с целью повышения надежности устройства,

в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, выход которого соединен с входом управления записью-считыванием второго блока памяти данных, а второй вход подключен к выходу элемента ИСКЛ ЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с инверсным выходом первого запоминающего элемента, а агорой вход - с выходом мультиплексора и с информационным входом второго блока памяти данных, выход

второго запоминающего элемента соединен с входом данных программируемого контроллера.

ЛГ

А

X

с/

иишппллг

С2

о п п п

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| и Левин А.А | |||

| Программируемые контроллеры | |||

| - М.: Машиностроение, 1985 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1992-03-07—Публикация

1989-08-07—Подача