Л ЛК3)25

Л

является наличие триггера коммутатора данных и коммутатора управле-4 ния, дешифратора и элемента ИЛИ, которые связаны между собой я с другими элементами. Триггер управляет поочередной работой счетчиков я одновременно переключает все коммутаторы, которые переводят блок памяти данных либо в режим обмена данными с входным и выходным блоками, либо в режим работы с блоком логической обработки. 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Программируемый контроллер | 1983 |

|

SU1238032A1 |

| Программируемый контроллер | 1987 |

|

SU1442976A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

Изобретение касается циклового программного управления производственным оборудованием. Цель изобретения - упрощение контроллера и расширение области его применения. Программируемый контроллер содержит блок 1 опроса состояния датчиков, блок 2 формирования выходных сигналов, блок 3 памяти данных, адресных счетчик 4, коммутатор 5 адресов, блок 6 логической обработки, генератор 7 импульсов, программный счетчик 8, блок 9 памяти программы, триггер 10, коммутатор 11 данных, коммутатор 12 управления, дешифратор 13 адресов опрашиваемых входов и элемент ИЛИ 14. Новым в контроллере является наличие триггера, коммутатора данных и коммутатора управления, дешифратора и элемента ИЛИ, которые связаны между собой и с другими элементами. Триггер управляет поочередной работой счетчиков и одновременно переключает все коммутаторы, которые переводят блок памяти данных либо в режим обмена данными с входным и выходным блоками, либо в режим работы с блоком логической обработки. 6 ил.

Изобретение относится к управляющим системам с программным управлением и может быть использовано для логического управления станками и автоматическими линиями.

Целью изобретения является упрощение программируемого кот роллера и расширение области применения.

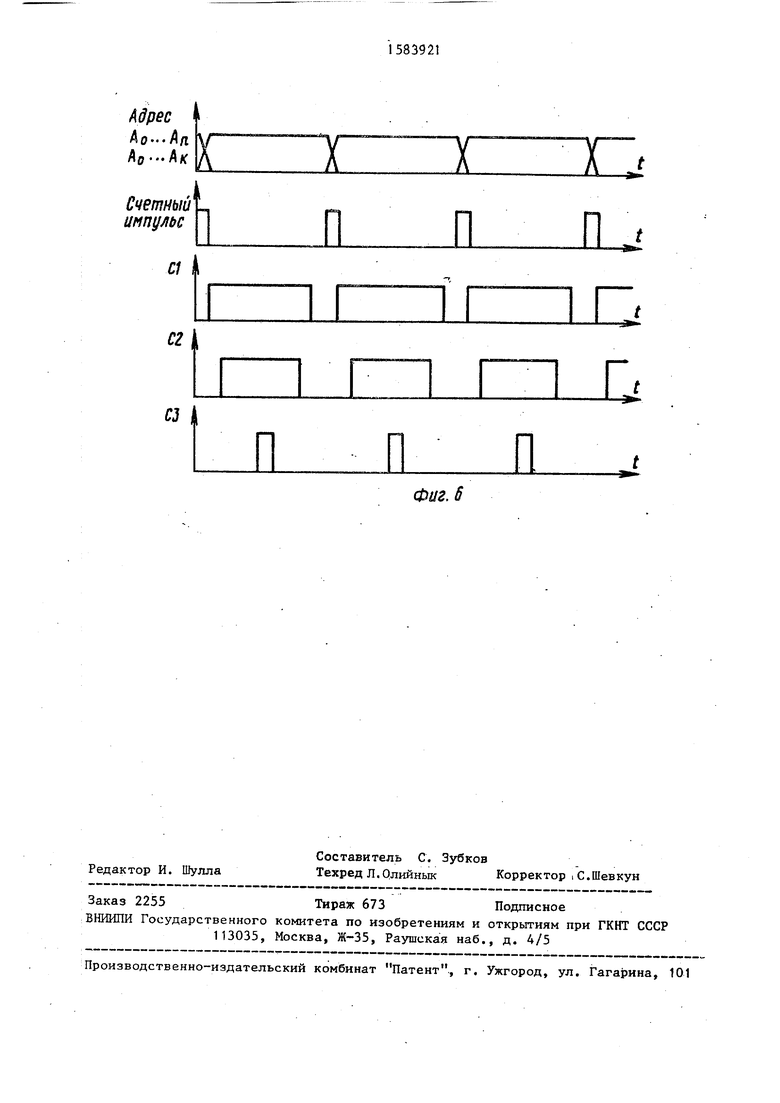

На фиг. I представлена функциональная схема контроллера; на фиг, 2- функциональная схема блока формирования выходных сигналов; на фиг. 3 функциональная схема блока логиче- ской обработки; на Фиг. 4 - функциональная схема генератора импульсов; на фиг„ 5 Функциональная схема третьего коммутатора; на фиг.6 - циклограмма работы генератора имнуль-

СОВ.

Программируемый контроллер содер- жит блок 1 опроса состояния датчиков блок 2 формирования выходных сигналов, блок 3 памяти дэнныхв адресный счетчик 4, первый коммутатор 5, блок 6 логической обработки, генератор 7 импульсов, программный счетчик 83 блок 9 памяти программ с выходами кодов

операций (Q $«) и адресов данных

40

(0,0««-Рк.) триггер 10, коммутатор П, коммутатор 12, дешифратор 13 и элемент ИЛИ 14. Блок 1 может быть реализован на мультиплексоре интегральной микросхеме К561КП2, выход которой 45 является выходом 15 блока 1 .

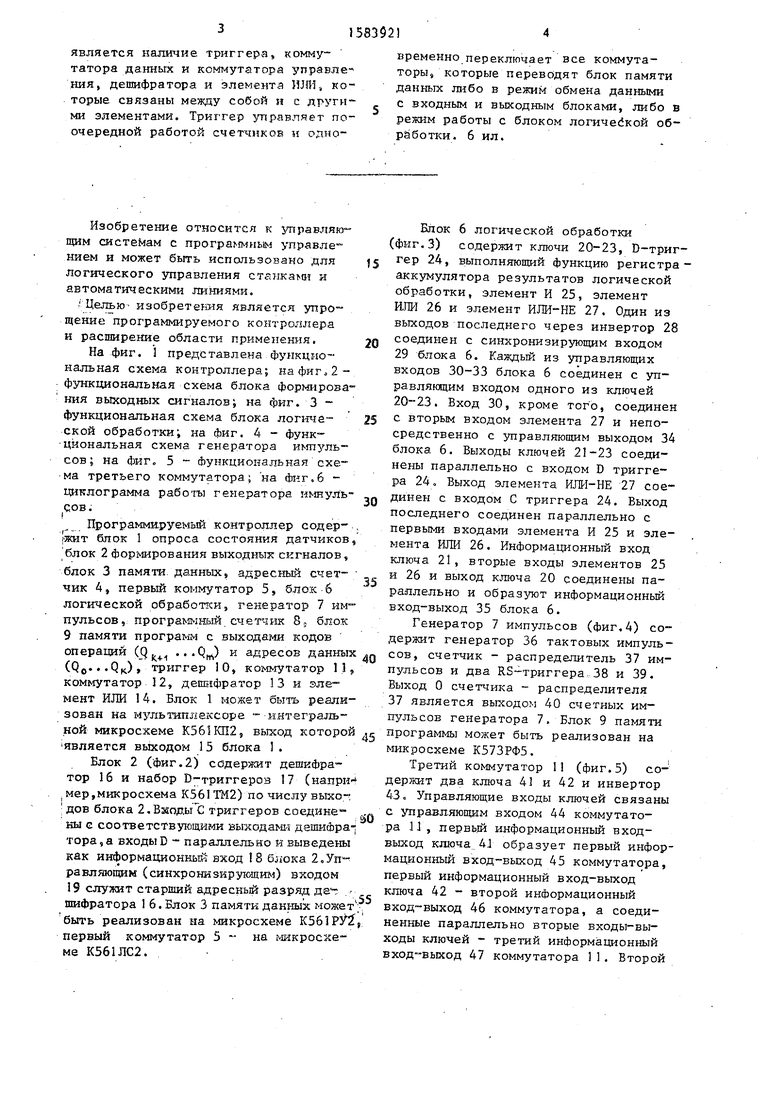

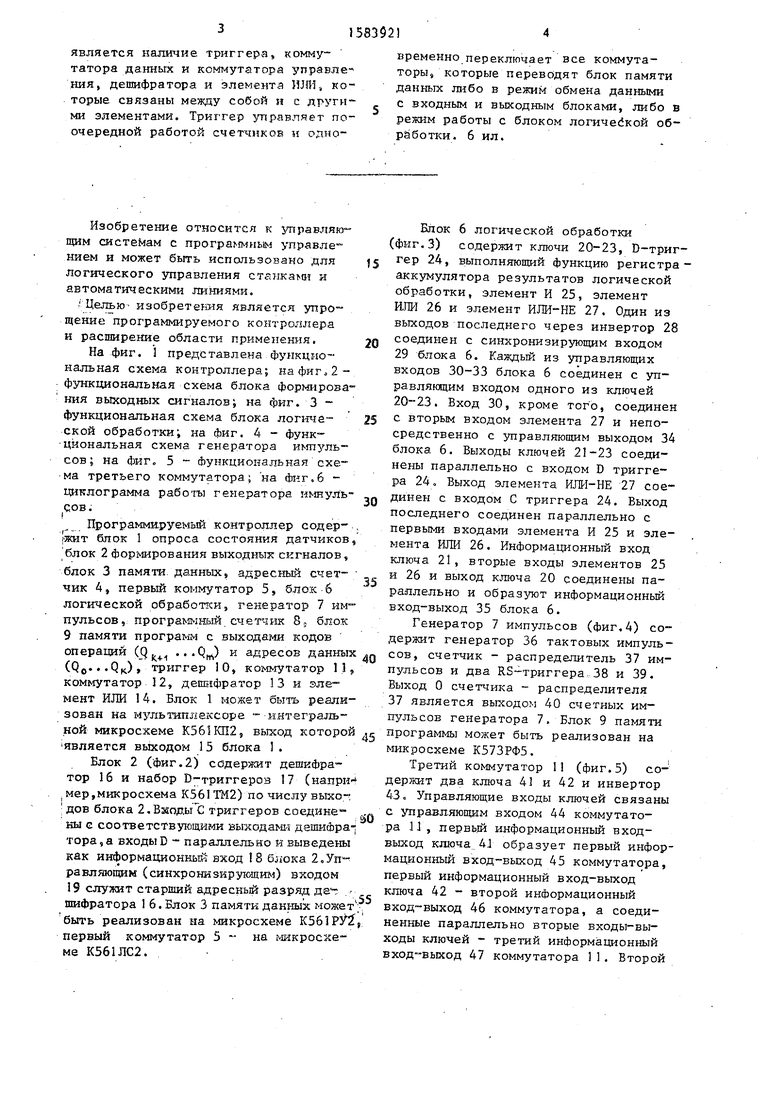

Блок 2 (фиг.2) содержит дешифратор 16 и набор D-триггероз 17 (напри-1 , мер,микросхема К561ТМ2) по числу выхо- дов блока 2. Взводы С триггеров соедине- .. кы с соответствующими выходами дешишра тора,а входыD - параллельно и выведены как информационный вход 18 блока 2.Управляющим (синхронизирующим) входом 19 служит старший адресный разряд де1 шифратора 1 6. Блок 3 памяти данных может1 быть реализован на микросхеме К561РУ2% первый коммутатор 5 - на микросхеме К561ЛС2.

55

15

20

35

40

45

..

55

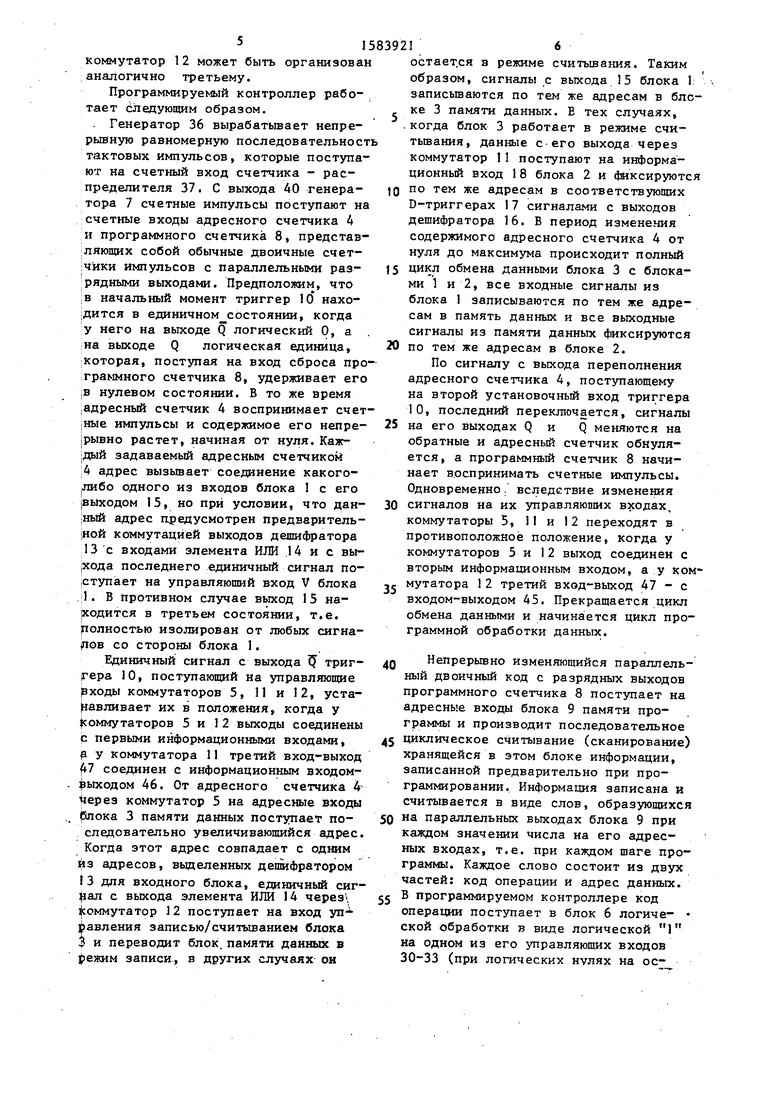

Елок 6 логической обработки (фиг.З) содержит ключи 20-23, D-триг- гер 24, выполняющий функцию регистра- аккумулятора результатов логической обработки, элемент И 25, элемент ИЛИ 26 и элемент ИЛИ-НЕ 27. Один из выходов последнего через инвертор 28 соединен с синхронизирующим входом 29 блока 6. Каждый из управляющих входов 30-33 блока 6 соединен с управляющим входом одного из ключей 20-23. Вход 30, кроме того, соединен с вторым входом элемента 27 и непосредственно с управляющим выходом 34 блока 6. Выходы ключей 21-23 соединены параллельно с входом D триггера 24. Выход элемента ИЛИ-НЕ 27 соединен с входом С триггера 24. Выход последнего соединен параллельно с первыми входами элемента И 25 и элемента ИЛИ 26. Информационный вход ключа 21, вторые входы элементов 25 и 26 и выход ключа 20 соединены параллельно и образуют информационный вход-выход 35 блока 6.

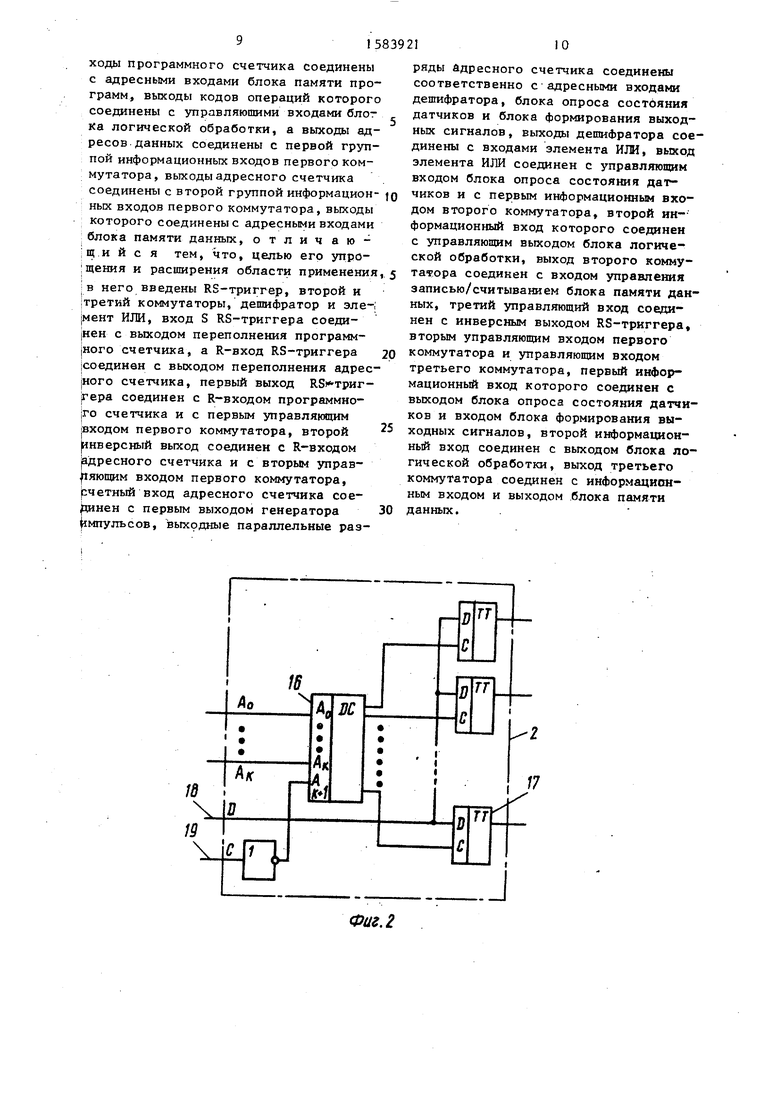

Генератор 7 импульсов (фиг.4) содержит генератор 36 тактовых импульсов, счетчик - распределитель 37 импульсов и два RS-триггера 38 и 39. Выход 0 счетчика - распределителя 37 является выходом 40 счетных импульсов генератора 7. Блок 9 памяти программы может быть реализован на микросхеме К573РФ5.

Третий коммутатор 11 (фиг.5) содержит два ключа 41 и 42 и инвертор 43 Управляющие входы ключей связаны с управляющим входом 44 коммутатора 11, первый информационный вход- выход ключа 4J образует первый информационный вход-выход 45 коммутатора, первый информационный вход-выход ключа 42 - второй информационный вход-выход 46 коммутатора, а соединенные параллельно вторые входы-выходы ключей - третий информационный вход-выход 47 коммутатора 1 1. Второй

коммутатор 12 может быть организован аналогично третьему.

Программируемый контроллер работает следующим образом.

. Генератор 36 вырабатывает непрерывную равномерную последовательност тактовых импульсов, которые поступают на счетный вход счетчика - распределителя 37. С выхода 40 генератора 7 счетные импульсы поступают на счетные входы адресного счетчика 4 и программного счетчика 8, представляющих собой обычные двоичные счетчики импульсов с параллельными разрядными выходами. Предположим, что в начальный момент триггер 10 находится в единичном состоянии, когда у него на выходе Q логический 0, а на выходе Q логическая единица, которая, поступая на вход сброса программного счетчика 8, удерживает его ,в нулевом состоянии. В то же время адресный счетчик 4 воспринимает счетные импульсы и содержимое его непрерывно растет, начиная от нуля. Каждый задаваемый адресным счетчиком 4 адрес вызывает соединение какого- либо одного из входов блока 1 с его ;выходом 15, но при условии, что данный адрес предусмотрен предварительной коммутацией выходов дешифратора 13 с входами элемента ИЛИ 14 и с вы- рсода последнего единичный сигнал по- ,ступает на управляющий вход V блока 1. В противном случае выход 15 находится в третьем состоянии, т.е. полностью изолирован от любых сигналов со стороны блока 1.

Единичный сигнал с выхода (J триггера 10, поступающий на управляющие Эходы коммутаторов 5, 11 и 12, устанавливает их в положения, когда у коммутаторов 5 и 12 выходы соединены с первыми информационными входами, а у коммутатора 11 третий вход-выход 47 соединен с информационным входом- выходом 46. От адресного счетчика 4 через коммутатор 5 на адресные входы блока 3 памяти данных поступает последовательно увеличивающийся адрес. Когда этот адрес совпадает с одним из адресов, выделенных дешифратором

13 для входного блока, единичный сигнал с выхода элемента ИЛИ 14 через, коммутатор J2 поступает на вход уп равления записью/считыванием блока $ и переводит блок, памяти данных в режим записи, в других случаях он

остает.ся в режиме считывания. Таким образом, сигналы с выхода 15 блока 1 записываются по тем же адресам в блоке 3 памяти данных. В тех случаях, .когда блок 3 работает в режиме считывания, данные с его выхода череэ коммутатор 11 поступают на информационный вход 18 блока 2 и фиксируются

g по тем же адресам в соответствующих D-триггерах 17 сигналами с выходов дешифратора 16. В период изменения содержимого адресного счетчика 4 от нуля до максимума происходит полный

5 цикл обмена данными блока 3 с блоками 1 и 2, все входные сигналы из блока 1 записываются по тем же адресам в память данных и все выходные сигналы из памяти данных фиксируются

0 по тем же адресам в блоке 2.

По сигналу с выхода переполнения адресного счетчика 4, поступающему на второй установочный вход триггера 10, последний переключается, сигналы

5 на его выходах Q и Q меняются на обратные и адресный счетчик обнуляется, а программный счетчик 8 начинает воспринимать счетные импульсы. Одновременно. вследствие изменения

0 сигналов на их управляющих входах, коммутаторы 5, 11 и 12 переходят в противоположное положение, когда у коммутаторов 5 и 12 выход соединен с вторым информационным входом, а у ком5 мутатора 12 третий вход-выход 47 - с входом-выходом 45. Прекращается цикл обмена данными и начинается цикл программной обработки данных.

Q Непрерывно изменяющийся параллельный двоичный код с разрядных выходов программного счетчика 8 поступает на адресные входы блока 9 памяти программы и производит последовательное

5 Циклическое считывание (сканирование) хранящейся в этом блоке информации, записанной предварительно при программировании. Информация записана и считывается в виде слов, образующихся

0 на параллельных выходах блока 9 при каждом значении числа на его адресных входах, т.е. при каждом шаге программы. Каждое слово состоит из двух частей: код операции и адрес данных.

5 В программируемом контроллере код

операции поступает в блок 6 логиче- ской обработки в виде логической 1 на одном из его управляющих входов 30-33 (при логических нулях на остальных из этих входов). Поступившая на один из управляющих входов логическая 1 означает команду на выпол-

10

20

25

30

некие блоком 6 определенных действий, а именно (фиг.З) 1 на входе 31 - запись в аккумулятор 27 текущего значения данных, поступающих с входа- выхода 35; J на входе 32 - запись в аккумулятор 24 результата логической операции И текущего значения данных с результатом предыдущей операции; на входе 33 - запись в аккумулятор 24 результата логической операции ИЛИ текущего значения данных jj с результатом предыдущей операции; 1 на входе 30 - вывод результата предыдущей операции на вход-выход 35.

Запись текущего значения данных и результатов логических операций в аккумулятор 24 производится с помощью синхроимпульсов СЗ, поступающих на вход 29 блока 6 от генератора 7 импульсов. При выводе результата из блока 6 запись в аккумулятор исключается с помощью элемента ИЛИ-НЕ 27, используемого в качестве ключа, запираемого логической 1 на входе 30. Уровень логического сигнала с входа 30 непосредственно поступает на управляющий выход 34, где означает признак данных, а именно логический О - данные, подлежащие логической обработке в блоке 6 (операн- , ды), логическая 1 - выводимые из блока 6 результаты логической обработки.

Считываемый при каждом очередном шаге программы адрес данных поступает через коммутатор 5 на адресные входы блока памяти данных. Одновременно сигнал с выхода 34 блока 6 через коммутатор 12 поступает на вход управления записью/считыванием блока 3 и определяет его режим: при логическом д5 О значение сигнала считывается из памяти данных и направляется через коммутатор I1 в блок 6 для логической обработки в соответствии с кодом операции на данном шаге программы, при en логической 1 результат предыдущей логической обработки из блока 6 через коммутатор 11 поступает в блок 3 и записывается в память данных.

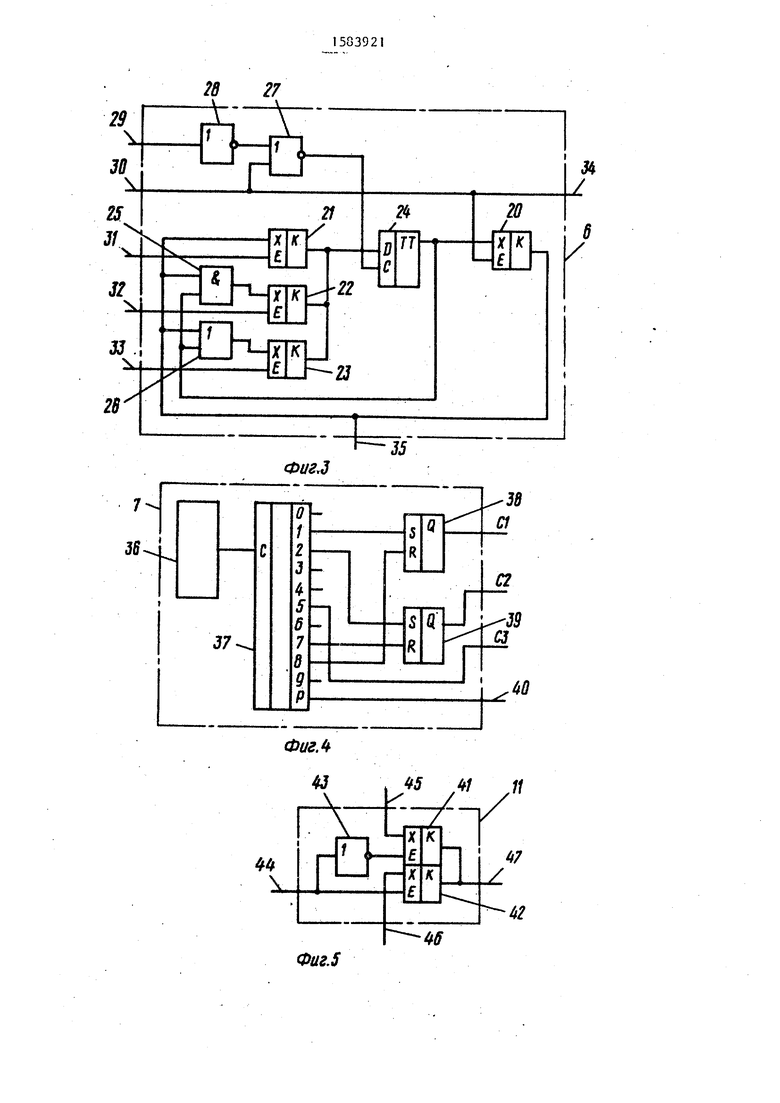

Синхронизация работы блоков, памяти „ программы 9, памяти данных 3, логической обработки 6, и блока 2 обеспечивается синхроимпульсами С1, С2 и СЗ, вырабатываемыми генератором 7 импуль5839218

сов по циклограмме (фиг.6). Синхроимпульсы С1 и С2 образуются на выходах триггеров 38 и 39 (фиг.4), установочные входы которых подключены к выходам счетчика - распределителя 37 в соответствии с циклограммой. Синхроимпульс СЗ образуется непосредственно на одном из выходов счетчика распределителя 37.

По окончании сканирования программы сигнал переполнения программного счетчика 8 поступает на первый установочный вход триггера JO и производит его переключение. Прекращается цикл программной обработки данных и начинается очередной цикл обмена данными, по окончании которого вновь начинается цикл программной обработки данных и т.д.

В цикле программной .обработки данных операндами могут служить любые записанные в блоке 3 данные, т.е. не только сигналы блока 1, но и результаты всех логических операций, в том числе и направляемые при обмене данными в блок 2. Если же в блоке 2 фиксировать сигналы по адресам, совпадающим с адресами каких-либо входов блока 2, то сигналы на соответствующих выходах повторяют состояния входов с одинаковыми адресами.

Упрощение конструкции и расширение функциональных возможностей программируемого контроллера позволяет расширить область его применения, получить более рациональные решения |ряда задач автоматизации производства, что в связи с большим распространением программируемых контроллеров в ,народном хозяйстве может дать значительный эффект.

35

40

Формула изобретения

Программируемый контроллер, содержащий блок опроса состояния датчиков, блок формирования выходных сигналов, соединенные с объектом управления, блок памяти данных, адресный счетчик, первый коммутатор, блок логической обработки, генератор импульсов, первый выход которого соединен с С-вхо- дом программного счетчика, второй, третий и четвертый выходы соединены соответственно с входами синхронизации блоков памяти программ, памяти данных, логической обработки и блока формирования выходных сигналов, выФормула изобретения

Программируемый контроллер, содержащий блок опроса состояния датчиков, блок формирования выходных сигналов, соединенные с объектом управления, блок памяти данных, адресный счетчик, первый коммутатор, блок логической обработки, генератор импульсов, первый выход которого соединен с С-вхо- дом программного счетчика, второй, третий и четвертый выходы соединены соответственно с входами синхронизации блоков памяти программ, памяти данных, логической обработки и блока формирования выходных сигналов, выходы программного счетчика соединены с адресными входами блока памяти программ, выходы кодов операций которого соединены с управляющими входами блока логической обработки, а выходы адресов данных соединены с первой группой информационных входов первого коммутатора, выходы адресного счетчика соединены с второй группой информацион- ных входов первого коммутатора, выходы которого соединены с адресными входами блока памяти данных, отличающийся тем, что, цепью его упрощения и расширения области применения

в него введены RS-триггер, второй и третий коммутаторы, дешифратор и эле-, ,мент ИЛИ, вход S RS-триггера соеди- |Нен с выходом переполнения программ- |Ного счетчика, а R-вход RS-триггера соединен с выходом переполнения адрес- «ого счетчика, первый выход RS Tpnr- гера соединен с R-входом программного счетчика и с первым управляющим входом первого коммутатора, второй снверсный выход соединен с R-входом адресного счетчика и с вторым управ- |тяющим входом первого коммутатора, рчетный вход адресного счетчика соединен с первым выходом генератора Импульсов, выходные параллельные раз

Q f

0

5

0

ряды адресного счетчика соединены соответственно с адресными входами дешифратора, блока опроса состояния датчиков и блока формирования выходных сигналов, выходы дешифратора соединены с входами элемента ИЛИ, выход элемента ИЛИ соединен с управляющим входом блока опроса состояния датчиков и с первым информационным входом второго коммутатора, второй информационный вход которого соединен с управляющим выходом блока логической обработки, выход второго коммутатора соединен с входом управления записью/считыванием блока памяти данных, третий управляющий вход соединен с инверсным выходом RS-триггера, вторым управляющим входом первого коммутатора и управляющим входом третьего коммутатора, первый информационный вход которого соединен с выходом блока опроса состояния датчиков и входом блока формирования выходных сигналов, второй информационный вход соединен с выходом блока логической обработки, выход третьего коммутатора соединен с информационным входом и выходом блока памяти данных.

Фаг. 2

ft

U to St

Ј0 6Ј

23

13

9ЈM

tt

Ъ гпф

tf

as i

ргпф

а

91

IZ6C9S1

Фиг. б

| Патент США 3827030, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Крыленко В.В., Миков И.Н., Фридман Л.И | |||

| и др | |||

| Управление автоматическими линиями с помощью ЭВМ | |||

| - М.: Машиностроение, 1983, с.139 | |||

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-08-07—Публикация

1988-06-17—Подача