Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ,

Цель изобретения - расширение области применения путем выполнения операции деления чисел на константу типа (2+1),

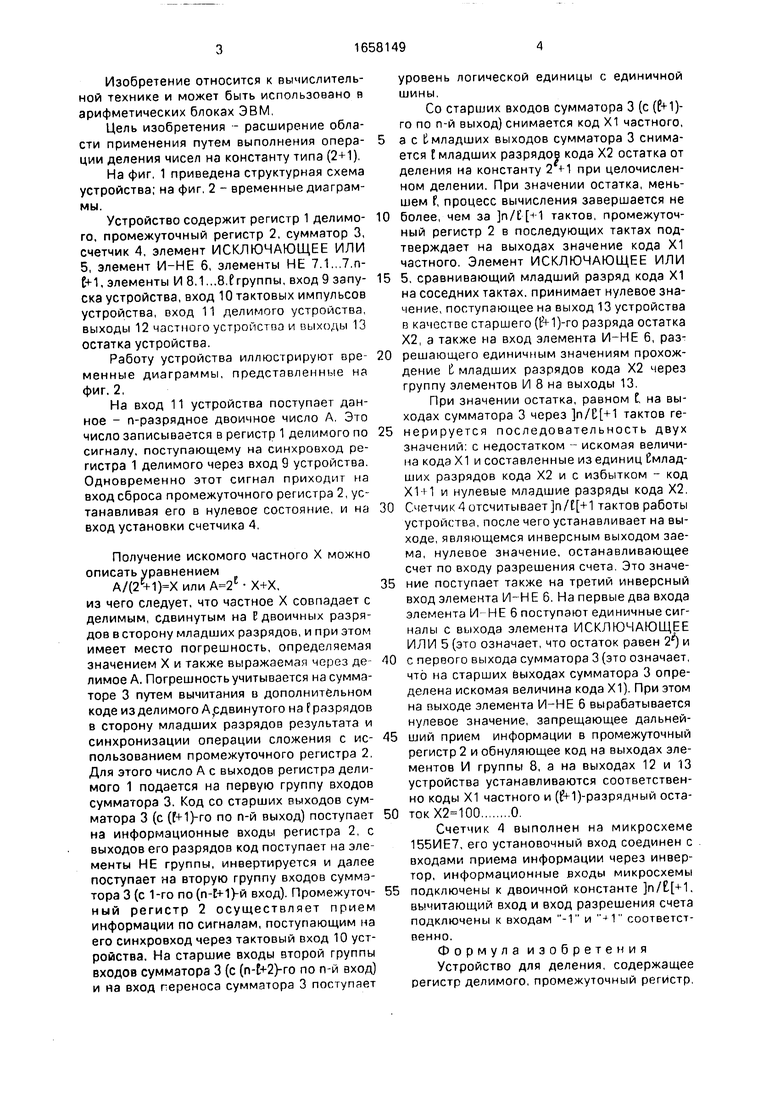

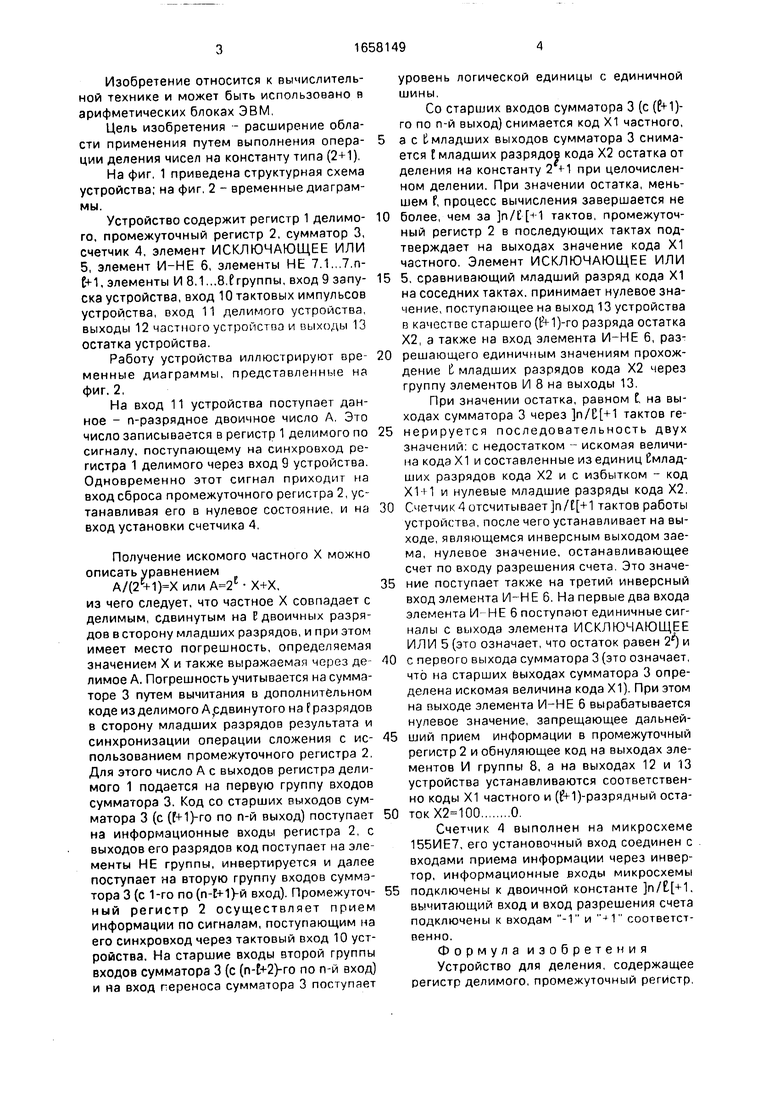

На фиг, 1 приведена структурная схема устройства; на фиг, 2 - временные диаграммы.

Устройство содержит регистр 1 делимого, промежуточный регистр 2, сумматор 3, счетчик 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент И-НЕ 6, элементы НЕ 7.1...7.П- С+1, элементы И 8.1...8,Сгруппы, вход 9 запуска устройства, вход 10 тактовых импульсов устройства, вход 11 делимого устройства, выходы 12 частного устройства и выходы 13 остатка устройства.

Работу устройства иллюстрируют временные диаграммы, представленные на фиг. 2,

На вход 11 устройства поступает данное - n-разрядное двоичное число А. Это число записывается в регистр 1 делимого по сигналу, поступающему на синхровход регистра 1 делимого через вход 9 устройства. Одновременно этот сигнал приходит на вход сброса промежуточного регистра 2, устанавливая его в нулевое состояние, и на вход установки счетчика 4,

Получение искомого частного X можно описать уравнением

А/(2Г+1)Х или Х+Х, из чего следует, что частное X совпадает с делимым, сдвинутым на Е двоичных разрядов в сторону младших разрядов, и при этом имеет место погрешность, определяемая значением X и также выражаемая через делимое А. Погрешность учитывается на сумматоре 3 путем вычитания в дополнительном коде изделимого Ардвинутого на f разрядов в сторону младших разрядов результата и синхронизации операции сложения с использованием промежуточного регистра 2, Для этого число А с выходов регистра делимого 1 подается на первую группу входов сумматора 3. Код со старших выходов сумматора 3 (с (f+1)-ro по n-й выход) поступает на информационные входы регистра 2, с выходов его разрядов код поступает на элементы НЕ группы, инвертируется и далее поступает на вторую группу входов сумматора 3 (с 1-го по (п-Е+1)-й вход). Промежуточ- ный регистр 2 осуществляет прием информации по сигналам, поступающим на его синхровход через тактовый вход 10 устройства. На старшие входы второй группы входов сумматора 3 (с (n-t+2}-ro по n-й вход) и на вход переноса сумматора 3 поступает

уровень логической единицы с единичной шины.

Со старших входов сумматора 3 (с (Ј+1)- го по n-й выход) снимается код Х1 частного,

ас t младших выходов сумматора 3 снимается {младших разрядов кода Х2 остатка от деления на константу 2 +1 при целочисленном делении. При значении остатка, меньшем F, процесс вычисления завершается не

0 более, чем за тактов, промежуточный регистр 2 в последующих тактах подтверждает на выходах значение кода Х1 частного. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

5 5, сравнивающий младший разряд кода Х1 на соседних тактах, принимает нулевое значение, поступающее на выход 13 устройства в качестве старшего (Р+1)-го разряда остатка Х2, а также на вход элемента И-НЕ 6, раз0 решающего единичным значениям прохождение t младших разрядов кода Х2 через группу элементов И 8 на выходы 13.

При значении остатка, равном С на выходах сумматора 3 через тактов ге5 нерируется последовательность двух значений: с недостатком - искомая величина кода Х1 и составленные из единиц Емлад- ших разрядов кода Х2 и с избытком - код Х1 + 1 и нулевые младшие разряды кода Х2.

0 Счетчик 4 отсчитывает п/С +1 тактов работы устройства, после чего устанавливает на выходе, являющемся инверсным выходом зае- ма, нулевое значение, останавливающее счет по входу разрешения счета. Это значе5 ние поступает также на третий инверсный вход элемента И-НЕ 6. На первые два входа элемента И-НЕ 6 поступают единичные сигналы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 (это означает, что остаток равен 2) и

0 с первого выхода сумматора 3 (это означает, что на старших выходах сумматора 3 определена искомая величина кода Х1). При этом на выходе элемента И-НЕ 6 вырабатывается нулевое значение, запрещающее дальней5 ший прием информации в промежуточный регистр 2 и обнуляющее код на выходах элементов И группы 8, а на выходах 12 и 13 устройства устанавливаются соответственно коды Х1 частного и (+1)-разрядный оста0 токХ2 1000.

Счетчик 4 выполнен на микросхеме 155ИЕ7, его установочный вход соединен с входами приема информации через инвертор, информационные входы микросхемы

5 подключены к двоичной константе п/Е.+1, вычитающий вход и вход разрешения счета подключены к входам -1 и -И соответственно.

Формула изобретения Устройство для деления, содержащее регистр делимого, промежуточный регистр,

сумматор, группу элементов И, первый элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, выходы разрядов которого соединены с входами разрядов первого слагаемого сумматора, выходы С младших разрядов которого соединены с первыми входами элементов И группы соответственно, выходы которых соединены с выходами I младших разрядов остатка устройства, выходы разрядов с (t+1}-ro по n-й сумматора (где п - разрядность делимого) соединены с информационными входами разрядов промежуточного регистра, отличающееся тем, что, с целью расширения области примене- йия путем выполнения операции деления чисел на константу типа (2 +1), устройство содержит счетчик, элемент И-НЕ, (n-Q элементов НЕ, причем выходы разрядов промежуточного регистра соединены с входами с первого по (n-f+1) элементов НЕ соответственно, выходы которых соединены с входами разрядов с первого по (п-Е+1)-й второго слагаемого сумматора, входы n-го и (п-Е+2) разрядов второго слагаемого которого соединены с входом переноса сумматора и входом логической единицы устройства, выход младшего разряда промежуточного регистра соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с информационным входом младшего разряда промежуточного регистра, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

соединен с выходом старшего разряда остатка устройства и с первым прямым входом элемента И-НЕ, второй прямой вход которого соединен с выходом младшего разряда сумматора, выходы разрядов с (М)-го по п-й

которого соединены с выходом частного устройства, вход запуска устройства соединен с входом сброса промежуточного регистра, с входом синхронизации регистра делимого и установочным входом счетчика, синхровход которого соединен с синхровходом промежуточного регистра и с входом тактовых импульсов устройства, инверсный выход за- ема счетчика соединен с входом разрешения счета счетчика и инверсным входом

элемента И-НЕ, выход которого соединен с входом разрешения записи промежуточного регистра и вторыми входами элементов И группы.

Вх.Ю

27/5

29/6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

Изобретение относится к вычигаитель- ной тех |ике. Целью изобретения является расширение области применения устройст ва за счет выполнения операции деления чисел на константу типа () Дзлени« осуществляется в соответствии с уравнением Х+Х, где X - частное. Устройство содержит регистр 1 принимающий делимое А, сумматор 3, вычитающий в дополнительном коде из делимого Л резуль тэт с,пвину тый на Е разрядов в сторону м,,адши разрядов, задержанных на такт на промежуточном регистре 2. Первоначально регистр 2 обнуляется Со старших и младших выходов сумматора 3 снимается код Х1 частного и 6мл ад- ших разрядов кода Х2 остатка соответственно При значении остатка меньше Е процесс вычисления завершается не более чем за тактов Промежуточный регистр 2 на последующих тактах подтверждает на выходах значение кода Х1 частного. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 принимает нулевое значение, поступающее в качестве старшего разряда остатка Х2. При значении остатка, равном Е, на выходах сумматора 3 через тактов генерируется последовательность двух значений: с недостатком - искомая величина кода Х1 и единичные младшие разряды кода Х2; с избытком - код Х1 + 1 и нулевые младшие разряды кода Х2 Счетчик 4 отсчитывает тактов работы устройства, после чего устанавливает на выходе нулевое значение, останавливающее счет по входу разрешения счета На выходе элемента И-НЕ 6 устанавливается нулевое значение, запрещающее прием информации в промежуточный регистр 2 2 ил. Ё CJ Ос Ј ч:

Bx.11

ZX

17017

Вых.

ЗЛ.1

Вы 3A.1

Вых.

ЗА.З

остояние четчика

Вш-эл..

000 110 W1 101

-У-у-х-)

А . А

77077 ЮЮ1 10110 W11Q

4 3 2 1 О

Вых.зл.5 Вых. эл.6

вых. зл. 7

111 001 010 OJO

ПО

п ZXZX

707

Bbtx.11

11 01

11101

11101

УС

000 111 101 110 101 ПО

-v-v- х-х-х-

.А-А-А-/ Ч /Ч

7770; 11101 11000 10111 11000 10111

-v-v-v-v-у .-/ -А-А-А /

i4 j г / о

111 000 OW ОСП; 010 001

111 000 110 101 110 Ю1

10

01 10 00 U 00 00

XZXDCXIXIXZ:

| Устройство для деления двоичного кода на (2 @ -1) | 1987 |

|

SU1481746A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1989-06-22—Подача