2K:vur r - tn.

b«Vuro u ::-2ur- utr иГ-и

1+1

dU

применена аппрокaxсимация вида

2((Ui-Ui.J

(6)

ti(UiM-U,-.,) Это обуславливает узкий класс решаемых задач, ограниченный только линейными уравнениями теплопроводност

Цель изобретения - расширение класса решаемых задач.

Поставленная цель достигается тем,что в устройство, содержащее певый блок умножения, два регистра, блок ввода и сумматор, выход которого соединен с первым входом первого регистра, выход которого соединен с первыми входами первого блока умножения, второго регистра и информационным выходом устройства, тактовый вход устройства соединен с вторыми входами первого и второго регистров, первый информационный взсод устройства соединен через блок ввода с вторым-входом первого блока умножения, выход которого соединен с входом сумматора, второй информационный вход устройства соединен с третьими входами первого и второг регистров, выход второго регистра соединен с третьим входом первого блока умножения,введены второй блок умножения, блок деления и блок вычитания, причем первый, второй и третий выходы блока вычитания соединены соответственно с первым и вторым входами второго блока умножения и первым входом блока деления второй и третий входы которого соединены соответственно с выходом второго блока умножения и тактовым входом устройства, выход блока деления соединен с четвертым входом первого блока умножения, первый и второй входы блока вычитания соединены соответственно с выходами первого регистра и блока ввода.

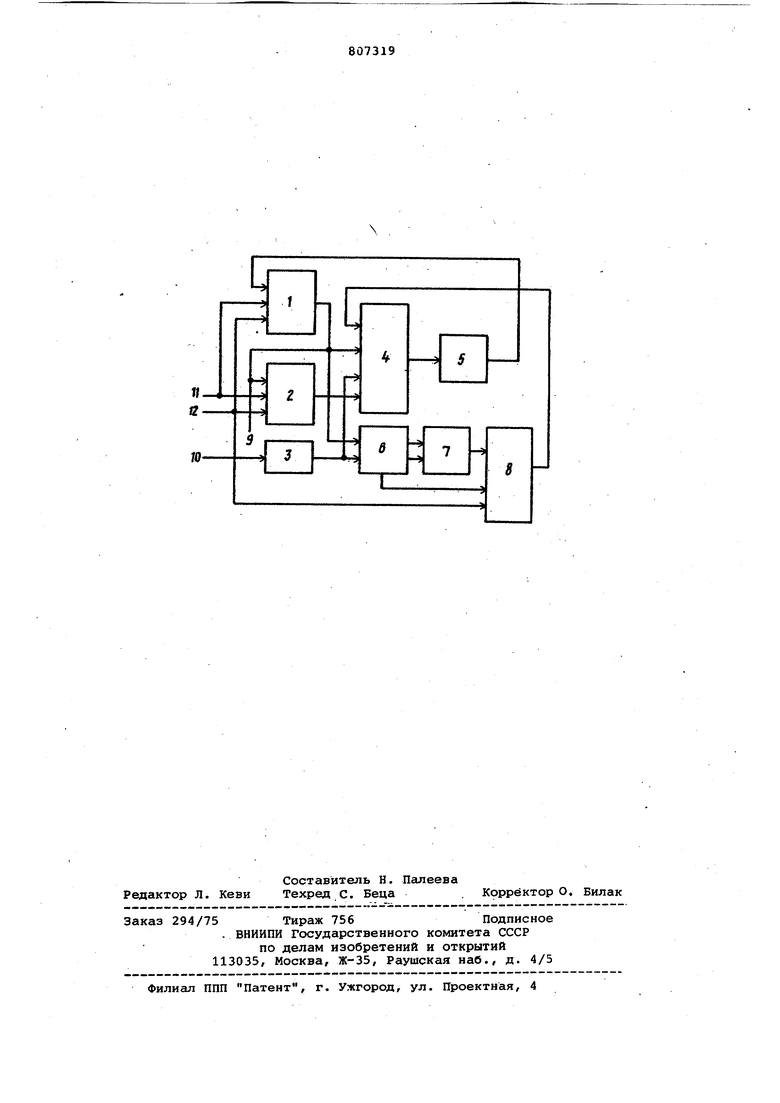

На чертеже представлена структурная схема устройства.

Устройство содержит первый регистр 1, второй регистр 2, блок 3 ввода, первый блок 4 умножения, сумматор 5, блок б вычитания, второ блок 7 умножения, блок 8 деления.

Выход 9 является выходом устройства, входы 10-12 являются первыми и вторыми информационными и тактовы входами устройства.

Первый регистр 1 предназначен для Хранения на к-ой итерации текущего решения и и записи полученного решения и (3).

Второй регистр 2 предназначен для хранения и вьвдачи начального условия и при итерировании на п-ом временном слое записи полученного решения по окончании итераций в с качестве начального условия для {п+1)-го временного слоя.

Блок 3 ввода служит для ввода в устройство информации о решении в соседних, подключенных к данному

Q устройствах.

Первый блок 4 умножения предназначен -для образования произведений, входящих в итерационную формулу (3) с использованием разностной схемы (5). ,

Сумматор 5 служит для образования решения путем суммирования произведений, поступающих из блока 4 Б соответствии с видом формулы (3) и (5).

0 Блок 6 вычитания предназначен для вычисления разностей, входящих в формулу (6).

Второй блок 7 умножения служит для образования числителя формулы

5 (б).

Блок 8 деления предназначен для вычисления выражения (6).

Первый информационный вход 10 устройства служит для подключения

rj к устройству выходов 9 соседних устройств при образовании цифровой сетки.

Второй информационный вход 11 устройства предназначен для пода, чи начальных условий.

Управляющий вход 12 устройства служит для подачи управляющего сигнала.

Работа устройства происходит следующим образом,

0 В регистры 1 и 2 по управляющему сигналу на входе 12 с входа 11 записываются начальные условия (и|° нулевая итерация решения на первом временном слое и - решение на

С нулевом временном слое, известное из постановки задачи), С выхода первого регистра 1 поступает на первый вход блока 6 вычитания, на .. второй вход которого приходят и;-;.° ,

0 i°-t передаваемые блоком 3 ввода с первого информационного входа 10, соединенного с выходом 9 соседних устройств. На выходах блока б вычитания образуются разности ( ) и ( )., поступающие на входы

второго блока 7 умножения и разность () , поступающая на первый вход блока 8 деления в качестве делителя, -на второй вход которого приходит в качестве делимого произве0 Дение ( -и|° ) (U ) с выхода второго блока 7 умножения. Таким образом, с выхода блока 8 деления значение выражения (6) -поступает начетвертый вход первого

5 блока 4 умножения, где последовательно умножается на величины ,0/ uj° , , поступающйе на его первый, второй, третий, входы р выходорегистров 1 и 2 и блока 3 ввода, на коэффициенты разностной схемы (5) и итерационной формулы (3), являющиеся известными функциями от fi , С , О и хранимые в рамом блоке 4, Сумматор 5 суммирует полученные в первом блоке 4 умножения произведения, образующие согласно (5) и (3), первую итерацию решения на первом временном слое U которая записывается lio первому входу в первый регистр 1, При решении линейных уравнений (1) по разностной схеме (2) методом итерации (3) блок 8 деления настраивается по управляющему сигналу, поступающему на его третий вход с входа 12 устройства, на генерацию (1) и вместо схемы (5) реализуется схема (2). Аналогично происходит работа устройства на второй и т.д. к-ой итерации, при этом определяются значения U;- и т.д. , По окончании итерационного процесса при поступлении соответсГвующего управляющего сигнала на вхо 12 информация из первого регистра 1 переписывается по первому входу во второй регистр 2, являясь величиной и,% т.е. начальным условием для второго временного слоя, на котором определяется , , и т.д. . На последующих временных слоях работа устройства происходит аналогичным образом.

Реализацию предлагаемого изобретения осуществляют на микросхемах серии К 155.

Использование в устройстве блока вычитания; соединенного входами с выходами первого регистра и блока ввода, а выходами с входами введенных второго блока умножения и блока деления, подключенного выходом к первому блоку умножения, выгодно отличает данное устройство от известного, так как позволяет решать важный класс нелинейных уравнений (4), характеризующих, например, актуальные задачи моделирования приборов с зарядовой связью, что существенно

расширяет класс решаемых задач, ограниченных только линейными уравнениями.

Формула изобретения

Устройство для решения дифференциальных уравнений в частных производных, содержащее первый блок умножения, два регистра, блок ввода и

0 сумматор, выход которого соединен с первым входом первого регистра, выход которого соединен с первыми входами первого блока умножения,второго регистра и информационным выходом

5 устройства, тактовый вход устройства соединен с вторыми входами первого и второго регистров, первый информационный вход устройства соединен через блок ввода с вторым входом пер0вого блока умножения, выход которого соединен с входом сумматора, второй информационный вход устройства сое- динен с третьими входами первого и второго регистров, выход второго регистра соединен с третьим входом

5 первого блока умножения, о т л. ичающееся тем, что, с целью расширения класйа решаемых задач, в него введены второйiблок умножения, .блок деления и блок вычитания, при0чем первый, второй и третий выходы блока вычитания соединены соответственно с первым и вторым входами второго блока умножения и первым входом блока деления, второй и тре5тий входы которого соединены соответственно с выходом второго блока умножения и тактовым входом устройства, выход блока деления соединен с четвертым входом первого блока.,

0 умножения, первый и второй входы блока вычитания соединены соответственно с .выходами первого регистра и блока ввода.

Источники информации,

5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 583455, кл. G Об F 15/32, 1977.

2.Авторское свидетельство СССР № 373735, кл. G 06 F 15/32, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифферен-циАльНыХ уРАВНЕНий B чАСТНыХпРОизВОдНыХ | 1978 |

|

SU798864A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1977 |

|

SU691861A1 |

| Устройство для решения дифференциальных уравнений | 1979 |

|

SU860078A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1978 |

|

SU742946A1 |

| Устройство для решения дифференциальныхуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1978 |

|

SU822196A1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| Устройство для решения дифференциальныхуРАВНЕНий | 1978 |

|

SU819810A1 |

| Вычислительная система для решения дифференциальных уравнений | 1978 |

|

SU771674A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1977 |

|

SU696473A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1977 |

|

SU679989A1 |

Авторы

Даты

1981-02-23—Публикация

1979-03-28—Подача