Изобретение относится к вычислительной технике и может использоваться для управления динамической памятью

Известно устройство содержащее два коммутатора, триггер, счетчик и схему сравнения,- Первый коммутатор является адресным.. Строчные адреса внешних обращений поступают так-, чтобы их последовательное изменение привело -к последовательному размещению информации в памяти. Через второй коммутатор задается адрес границы задействованной памяти. В режиме регенерации при совпадении состояний счетчика с адресом границы регенерация прекращается

Быстродействие устройства ограничивается необходимостью, при наращивании объема задействованной памяти изменять ее границу извне. Кроме того, извне должна формироваться последовательная инкремента- ция адресов внешних обращений, что (ограничивает функциональные возмож- JHOCTM устройства.

Наиболее близким к изобретению по технической сущности является устройство, содержащее два коммутато- . ра, три счетчика, триггер и элемент 214. Счетчики подсчитывают количество загружаемых ячеек памяти, и по их состоянию присваиваются адреса загружаемой информации. В режиме регенерации перебираются адреса лишь загруженной к началу работы в этом режиме зоны памяти,

Функциональные возможности устройства и его быстродействие ограничиваются необходимостью выделения в течение цикла регенерации определенного времени на регенерацию. Во время этого временного интервала внешние обращения к памяти воспрещаются .

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство для распределения и регенерации динамической памяти, (содержащее три счетчика, два коммуе 8

1

&э ел

00

ЈЛ -4

татора, синхровхор первого сметчика -; вход разрешения записи устоойства, вход сброса - вход начальной установ : KW устройства, подключенный к входам/ сброса второго и управления третьего счетчиков, информационный выход подключен к первому информационному входу первого коммутатора и является выходом адреса строки устройства, а выход переноса соединен с синхровхо- дом второго счетчика, выход которого - второй выход адреса столбца устройства подключен к информационному входу третьего счетчика, синхровход первого коммутатора является входом

разрешения считывания устройства,

второй информационный вход первого и первый информационный вход второго коммутатора -соответственно первыми второй адресные входы, а их выходы - соответствующие адресные выходы устройства , введен третий коммутатор, управляющий вход которого подключен к синхровходу первого счетчика, первый информационный вход соединен с выходом второго, второй информационный вход - с информационным выходом третьего счетчиков, выход подключен к второму информационному входу второго коммутатора, управляющий вход которого подключен к управляющему входу первого коммутатора, а выход заема переноса третьего счетчика соединен с входом установки этого счетчика.

Устройство позволяет осуществлять обращение к памяти в течение всего периода-регенерации, что существенно расширяет его функциональные возможности.

Повышается быстродействие устройства, поскольку на время регенерации специальной блокировки обращения процессора к памяти не требуется, следовательно, обмен процессора с памятью упрощается. Быстродействие повышается примерно в 2 раза.

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - временные диаграммы его работы.

Устройство содержит (фиг. 1) первый 1, второй 2 и третий 3 счетчи10

15

30

40

ца 12, первый 13 и второй 1 адресные входы, первый 15 и второй 16 адресные выходы.

Синхровход первого счетчика 1 под ключен к входу 7 устройства и управляющему входу третьего коммутатора 6 вход сброса - к входу- сброса второго счетчика 2, управляющему входу треть его счетчика 3 и входу 10 начальной установки устройства, информационный выход- - к первому информационному входу первого коммутатора А и выходу 11 устройства, а выход переноса - к синхровходу счетчика 2) В ыход кото

рого подключен к выходу 12 устройства, первому информационному входу тоетьего коммутатора 6 и информацион ному входу счетчика 3, выход заема

20 переноса которого соединен с его вхо дом установки, синхровход подключен к входу 8 устройства, а информационный выход - к второму информационному входу коммутатора 6, управляющий

25 выход - к второму информационному

входу коммутатора 6, управляющий вхо первого коммутатора 4 подключен к уп равляющему входу второго коммутатора 5 и входу 3 устройства, второй инфор мационный вход - к первому адресному входу 13 устройства, а выход - к пер вому адресному выходу 15 устройства, первый информационный вход коммутато ра 5 подключен к второму адресному входу 14 устройства, второй - к вы-

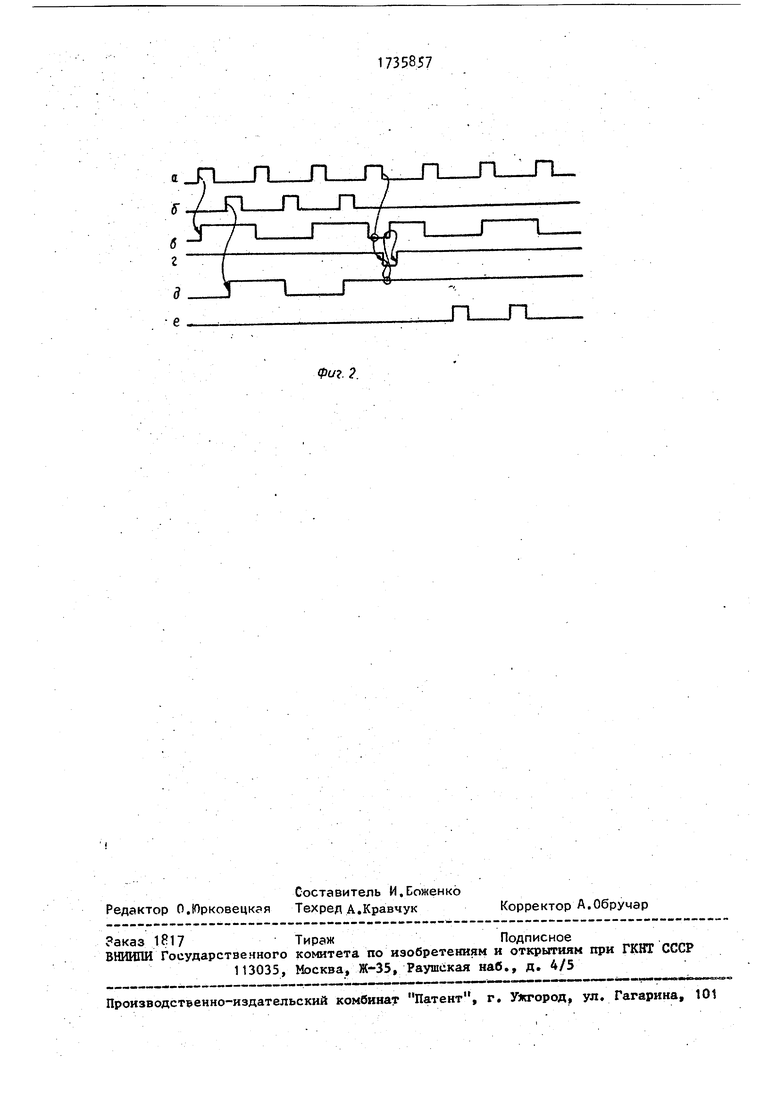

35 ходу коммутатора 6, а выход - к второму адресному выходу 16 устройства. На фиг.2 обозначены: а - импульсы регенерации, поступающие на вход 8 устройства , б - импульсы загрузки памяти на входе 7 в - состояние третьего счетчика 3} г - выход заема переноса счетчика 3, Д - состояние второго счетчика 2, е - импульсы обращения к задействованной памяти на

45 входе 9. I

В реализованном варианте устройства счетчики 1 - 3 выполнены на микросхемах К555ИЕ7, коммутаторы k 50 6 - на К555КП11.

Устройство работает следующим образом.

Первый счетчик 1 является счетчиком определения адреса столбца грани

ки, первый 4, второй 5 и третий 6 ком- цы задействованной зоны памяти, вто- мутаторы, входы разрешения записи 7 РОЙ счетчик 2 - счетчиком опреде- импульсов регенерации 8, разрешения ления адреса строки границы, третий считывания 9 и начальной установки счетчик 3 является счетчиком реге- 10, выходы адреса строки 11 и столб- нерации. С выходов 11 и 12 в про0

5

0

0

ца 12, первый 13 и второй 1 адресные входы, первый 15 и второй 16 ад- ресные выходы.

Синхровход первого счетчика 1 подключен к входу 7 устройства и управляющему входу третьего коммутатора 6, вход сброса - к входу- сброса второго счетчика 2, управляющему входу третьего счетчика 3 и входу 10 начальной установки устройства, информационный выход- - к первому информационному входу первого коммутатора А и выходу 11 устройства, а выход переноса - к синхровходу счетчика 2) В ыход которого подключен к выходу 12 устройства, первому информационному входу тоетьего коммутатора 6 и информационному входу счетчика 3, выход заема

0 переноса которого соединен с его вхо- дом установки, синхровход подключен к входу 8 устройства, а информационный выход - к второму информационному входу коммутатора 6, управляющий

5 выход - к второму информационному

входу коммутатора 6, управляющий вход первого коммутатора 4 подключен к управляющему входу второго коммутатора 5 и входу 3 устройства, второй информационный вход - к первому адресному входу 13 устройства, а выход - к первому адресному выходу 15 устройства, первый информационный вход коммутатора 5 подключен к второму адресному входу 14 устройства, второй - к вы-

5 ходу коммутатора 6, а выход - к второму адресному выходу 16 устройства. На фиг.2 обозначены: а - импульсы регенерации, поступающие на вход 8 устройства , б - импульсы загрузки памяти на входе 7 в - состояние третьего счетчика 3} г - выход заема переноса счетчика 3, Д - состояние второго счетчика 2, е - импульсы обращения к задействованной памяти на

5 входе 9. I

В реализованном варианте устройства счетчики 1 - 3 выполнены на микросхемах К555ИЕ7, коммутаторы k 0 6 - на К555КП11.

Устройство работает следующим образом.

Первый счетчик 1 является счетчиком определения адреса столбца границы задействованной зоны памяти, вто- РОЙ счетчик 2 - счетчиком опреде- ления адреса строки границы, третий счетчик 3 является счетчиком реге- нерации. С выходов 11 и 12 в про5

цессор для сведения поступают адреса присвоенные загружаемой информации, С выходов 15 и 16 адресуются ячейки задействованной зоны памяти. Поскольку регенерация динамической памяти осуществляется путем переброса только адресов ее строк, то для регенерации используется информация о состоянии счетчика 2.

Перед загрузкой памяти производится начальная установка устройства сигнал которой поступает по входу 10 Счетчики 1 и 2 сбрасываются, а счетчик 3 переводится в режим прямого счета и тем самым выход заема переноса счет-чика 3 блокируется. По импульсам регенерации, поступающим на вход 8t счетчик 3 последовательно генерирует все адреса строк динамической памяти. При этом сигналы на входы 7 и 9 не поступают, и строчные адреса через коммутаторы 6 и 5 и выход 16 поступают на адресацию памяти Сигнал начальной установки устанав-- ливается на входе 10 на время, необходимое для начала нормального функционирования динамической памяти Как правило, это время после включения питания составляет 8-16 циклов регенерации всех адресов строк, По истечении этого времени сигнал начальной установки снимается., снимается тем самым сброс со счетчиков 1 и 2, а счетчик 3 переводится в режим обратного счета.

Последующая регенерация памяти производится счетчиком 3 по импульсам регенерации (фиг. 2а) в режиме обратного счета (фиг.2в), В промежутках между импульсами регенерации производится загрузка памяти по импульсам загрузки (фиг.26), поступающим на вход 7. По ним коммутатор 6 подключает к второму входу коммутатора 5 выход счетчика 2. Коммутаторы Ь и 5 по-прежнему передают на выходе 15 и 16 информацию с выходов соответственно счетчика 1 и коммутатора 6. По импульсам загрузки переключается счетчик 1, а по сигналам его переноса - счетчик 2 (фиг.2д По состоянию счетчиков 1 и 2 через выходы 15 и 16 присваиваются адреса загружаемой в память информации. Эти же адреса через выходы 11 и 12 поступают к процессору для сведения,. Такое размещение информации, начиная с младших разрядов адресов

10

15

25

35&576

столбцов и при изменении адресов строк только после полного перебора адресов столбцов, обеспечивает мини- , мально необходимый с точки зрения ее ) регенерации объем задействованной памяти ,

При установке в процессе регенерации счетчика 3 в нулевое состояние он вырабатывает сигнал заема переноса (фиг.2г). По нему в счетчике 3 устанавливается код адреса строки границы задействованной зоны, сформированный счетчиком 2, После этого сиг-нал заема сбрасывается и счетчик 3 осуществляет перебор адресов регенерации от адресов границы до нулевого адреса.

В режиме обмена процессора с за20 груженной зоной памяти сигналы за- - |груз и не поступают. В промежутке между импульсами регенерации на вход 9 поступают импульсы обмена (фиг.2е). По ним коммутаторы ( и 5 подключают к выходам 15 и 16 входы 13 и 14 соответственно. В этом случае адреса обращения к памяти задаются процессором: по входу 13 - адреса строк, по входу i - адреса столбцов.

Таким образом, устройство в промежутках между формированием адресов регенерации присваивает адреса загружаемой в память информации. В процессе регенерации перебирается минимально необходимое количество адре35 сов строк.

В устройстве-прототипе для процесса регенерации необходима отводить определенный промежуток времени, в течение которого загрузка памяти, а

40 равно последующие внешние обращения к ней блокируются. Это требует специальной организации обращения про- . цессора к памяти, чем область применения прототипа ограничивается. В

45 предлагаемом устройстве обеспечивается возможность адресации памяти вне зависимости от того, закончен или нет процесс регенерации. Это позволяет упростить процедуру обмена

50 процессора с памятью и, как следствие, примерно вдвое повысить скорость обмена.

30

Формула изобретения

Устройство для распределения, и регенерации динамической памяти, содержащее три счетчика и два коммутатора, причем синхровход первого счетчика является входом разрешения записи устройства, вход сброса соедине с входом сброса второго счетчика и управляющим входом третьего сиетми- ка и является входом начальной- уста- новки устройства, информационный выход подключен к первому информационному входу первого коммутатора и является выходом адреса столбца устройства, а выход переноса соединен с синхровходом второго счетчика, выход которого соединен с информационным входом третьего счетчика и является выходом адреса строки устройства, синхровход третьего счетчика-являетс входом импульсов регенерации устройства, первый и второй информационные входы второго и первого коммутаторов являются вторым и первым адресными входами устройства соответственно, управляющий вход первого коммутато

5

0

ра является входом разрешения считывания устройства, выходы первого и второго коммутаторов являются первым и вторым адресными выходами устройства соответственно, отличающееся тем, что, с целью расширения функциональных возможностей, в него введен третий коммутатор, управляющий вход которого соединен с синхровходом первого сметчика, первый и второй информационные входы соединены с информационными выходами второго и третьего счетчиков соответственно, а выход подключен к второму информационному входу второго коммутатора, управляющий вход которого соединен с управляющим входом первого коммутатора, а выход переноса третьего счетчика подключен к входу его установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для управления регенерацией динамической памяти | 1987 |

|

SU1474744A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство для отображения информации | 1986 |

|

SU1367009A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

Изобретение относится к вычислительной технике и может использоваться для управления динамической памятью. Цель изобретения расширение функциональных возможностей устройства. Это достигается введением третьего коммутатора с соответствующими связями. 2 ил.

| Запоминающее устройство | 1983 |

|

SU1101891A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ И РЕГЕНЕРАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | |||

Авторы

Даты

1992-05-23—Публикация

1989-10-16—Подача