О)

го

;й

IN;) 01

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств ;на основе элементов полупроводниковой динамической-памяти.

Цель изобретения - повышение быстродействия устройства.

На фиг,I представлена функционапь

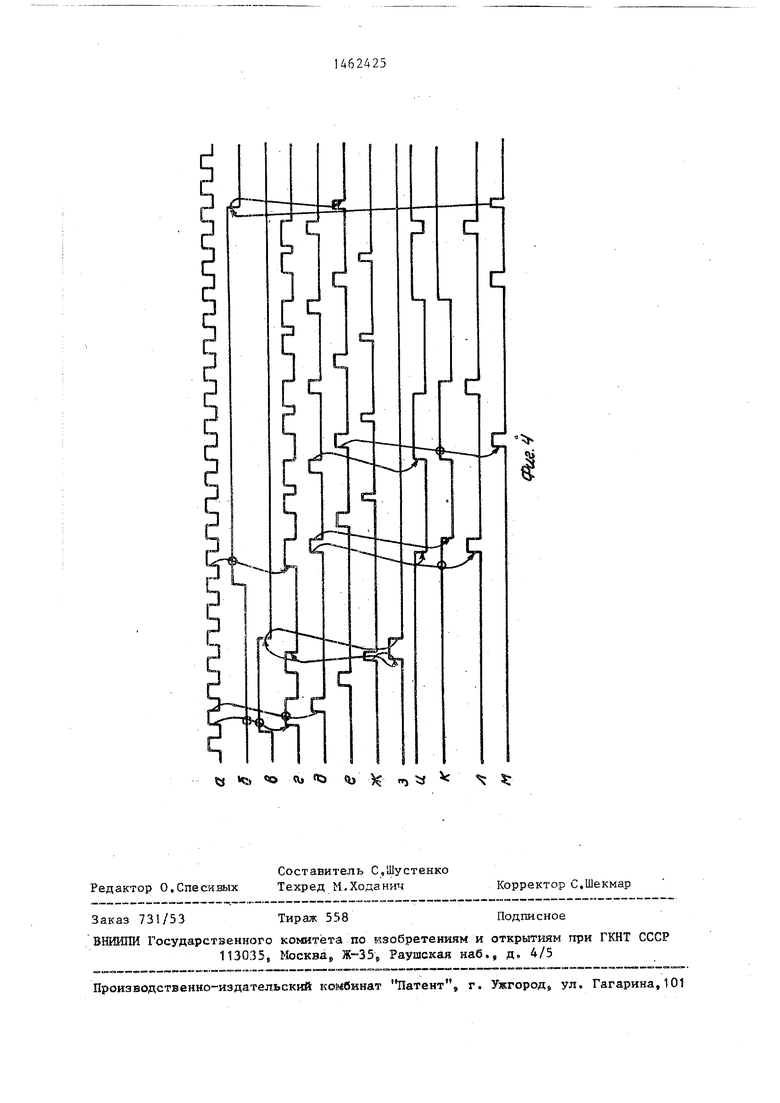

ления на входе 1; 2 последовательность переключения счетчика 17;a-;k- сигналы на первом-третьем выходах дешифратора 18§ о.- сигнал подтверждения на прямом выходе триггера 19; ц - сигнал обратного переноса счетчика 2 на входе 3,2; к - выходное состояние триггера 20; л - сигнал, установки

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регенерации динамической памяти со свободными зонами | 1989 |

|

SU1672529A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для управления регенерацией динамической памяти | 1987 |

|

SU1474744A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для распределения и регенерации динамической памяти | 1989 |

|

SU1735857A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1354242A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения - повьппение быстродействия устройства. Устройство содержит счетчик 1 зон, блок 8 памяти, счетчик 2 адресов, .блок 3 синхронизации, вход 4 записи, выход 5 сигнала подтверждения., выход 6 импульсов регенерации, адресные выходы 7 младших разрядов, триггер 9, вход 10 режима, выход 11 запроса регенер ации, йдрес- ные входы 12, адресные выходы 13 старших разрядов. В режиме внешних обращений к памяти в блок 8 памяти записываются верхние границы каждой из зон динамической памяти, В режиме регенерации в счетчик 2 заносятся из блока 8 памяти младшие разряды адреса границы зоны, определяемой счетчиком 1. Счетчик 2 перебирает адреса до нулевого состояния, при котором вырабатывается сигнал заема, поступающий в блок 3. Осуществляется изменение состояния -счетчика 1, и уст.ройство переходит к аналогичному перебору адресов следукндей зоны. По окончании регенерации последней зоны счетчик 1 вырабатывает сигнал заема, сбрасывающий триггер 9 и переводящий устройство в режим внесения обращения . 4 ил. (Л

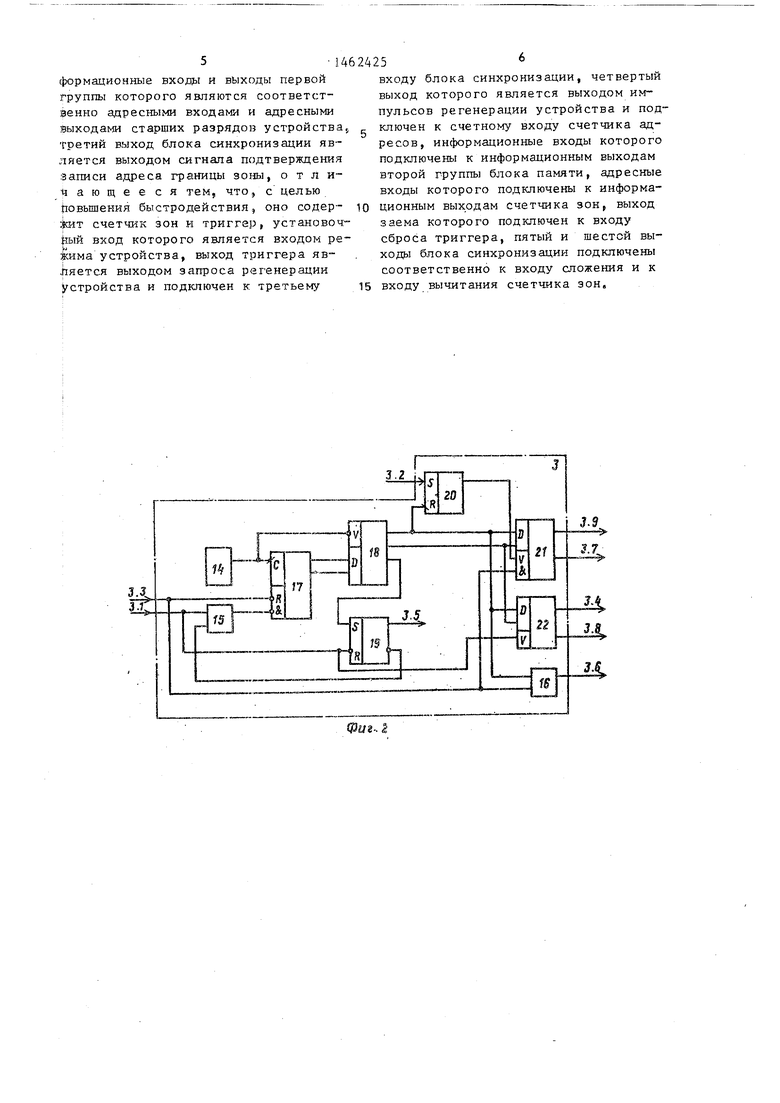

нал схема устройства; на фиг,2 - функ-ю счетчика 2 -на выходе 3,9; м - сигнал

пиональная слсема блока синхронизации

в реапизованном варианте устройства;

на фиг, 3, 4 - временные диаграмг л

работы соответственно устройства и

блока синхронизации.

15

декремента счетчика 1 на выходе 3,7.

Устройство реализовано для управления регенерацией динамической памяти с семиразрядным строчным адресом регенерации, разбитой на 8 зон. Переход от зоны к зоне определяется переключением трех старших разрядов на втором-выходе блока 8 памяти адресов. Перебор строчных адресов внутри зоны - переключением четырех разрядов счетчика 2,

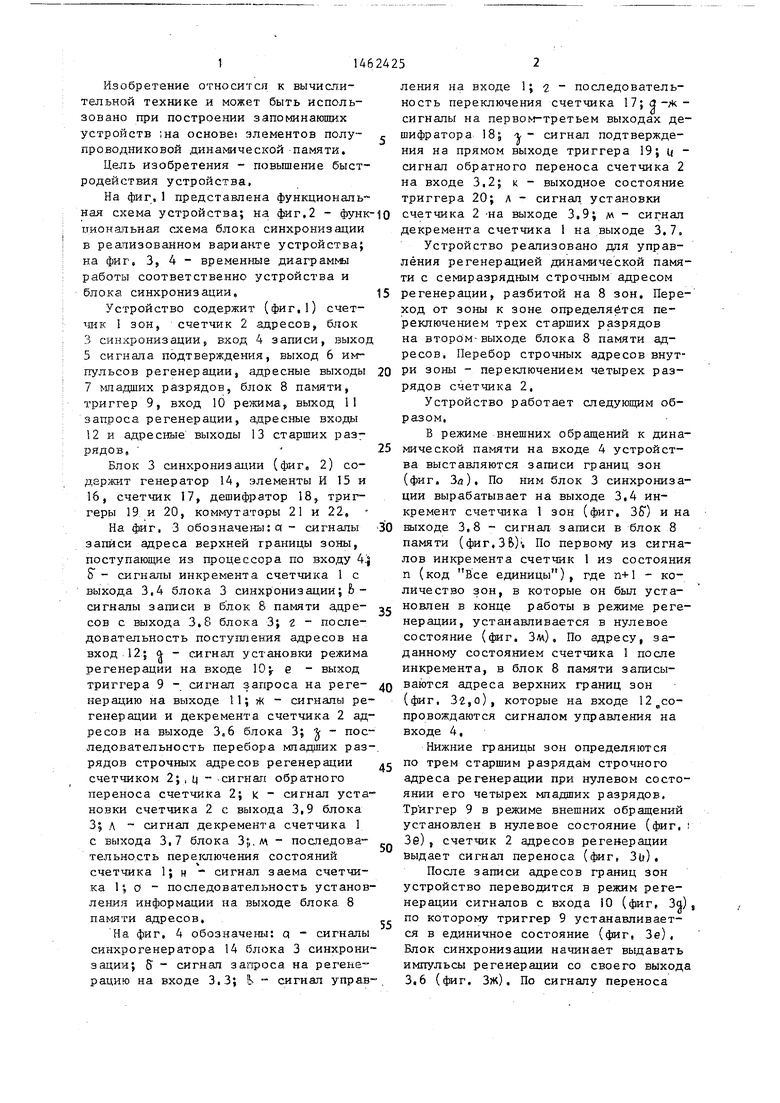

Устройство содержит (фиг,1) счетчик 1 зон, счетчик 2 адресов, блок 3 синхронизации5 вход 4 записи, выход 5 сигнала подтверждения, выход 6 И пульсов регенерации, адресные выходы 7 младших разрядов, блок 8 памяти, триггер 9, вход 10 режима, выход 11 запроса регенерации, а,цресные входы 12 и адресные выходы 13 старших разрядов,

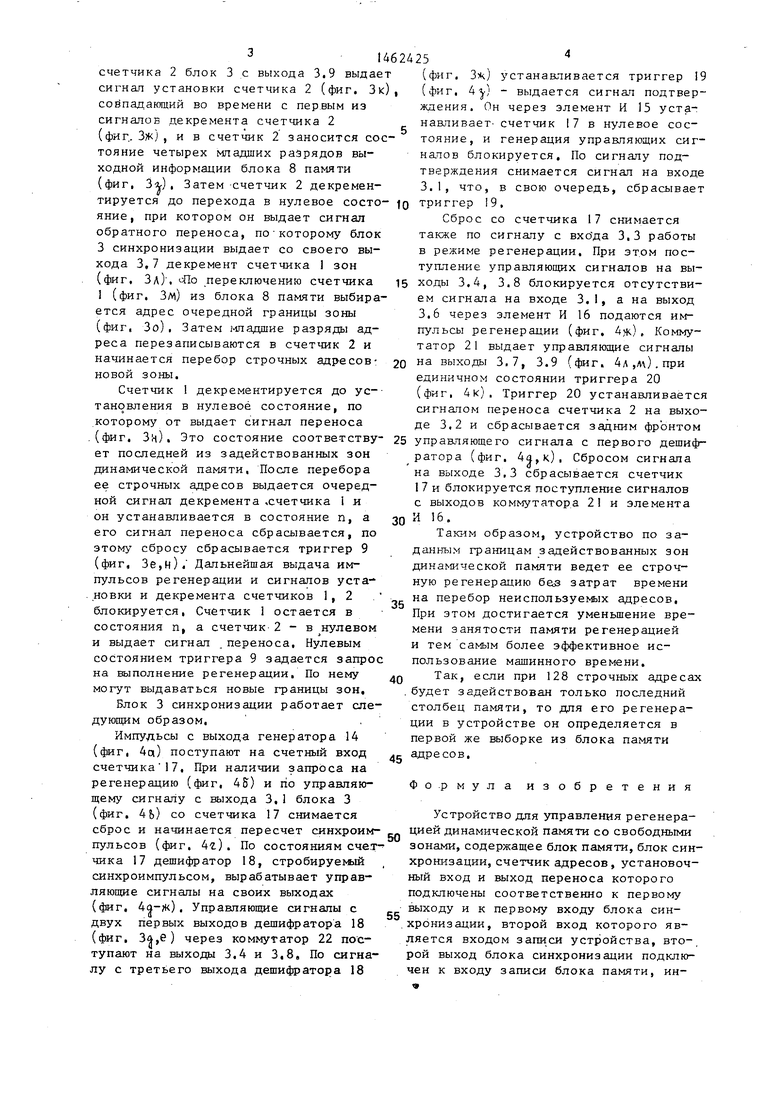

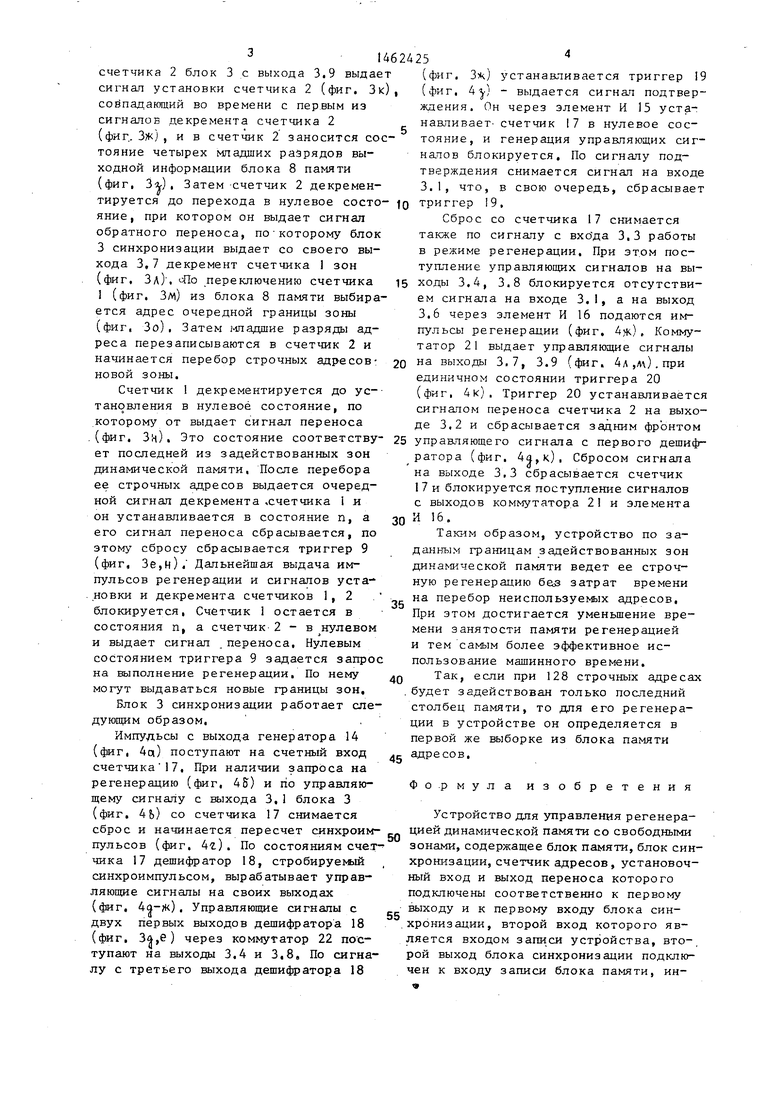

Блок 3 синхронизации (фиг, 2) содержит генератор 14, элементы И 15 и 16, счетчик 17, дешифратор 18, триггеры 19. и 20, коммутаторы 21 и 22,

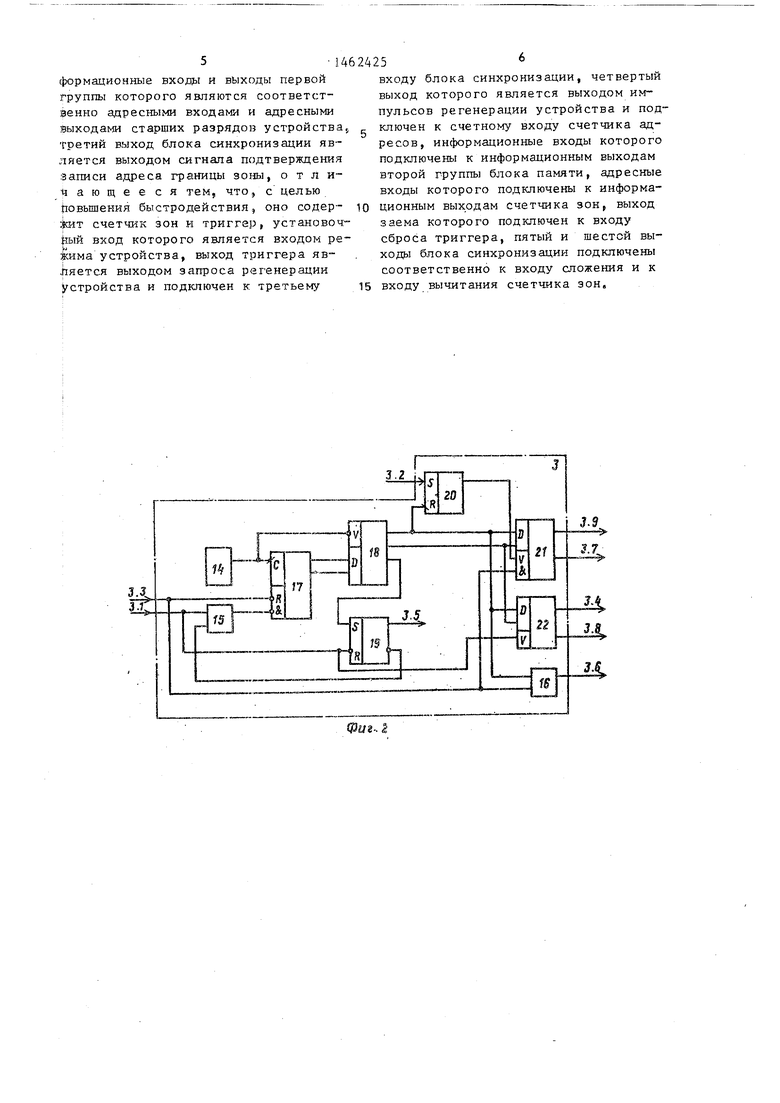

На фиг, 3 обозначены:а - сигналы записи адреса верхней границы зоны, поступающие из процессора по входу 4. j S - сигналы инкремента счетчика 1 с выхода 3,4 блока 3 синхронизации; Ь- сигналы записи в б лок 8 памяти а,цре- сов с выхода 3,8 блока 3; г - последовательность постугтев:ия адресов на вход 12; - сигнал установки режима регенерации на входе 10;. е - выход триггера 9 - сигнал запроса на регенерацию на выходе 11; ж - сигналы регенерации и декремента счетчика 2 адресов на выходе 3,6 блока 3; - последовательность перебора младших разрядов строчных адресов регенерации счетчиком 2; , ц - .сигнал обратного переноса счет чика 2; к - сигнал установки счетчика 2 с выхода 3,9 блока 3; л сигнап декремента счетчика 1 с выхода 3,7 блока 3;.м - последовательность перегслючения состояний счетчика 1; н - сигнал заема счетчика 1 , о - поспедовательность установления информации на выходе блока 8 памяти адресов,

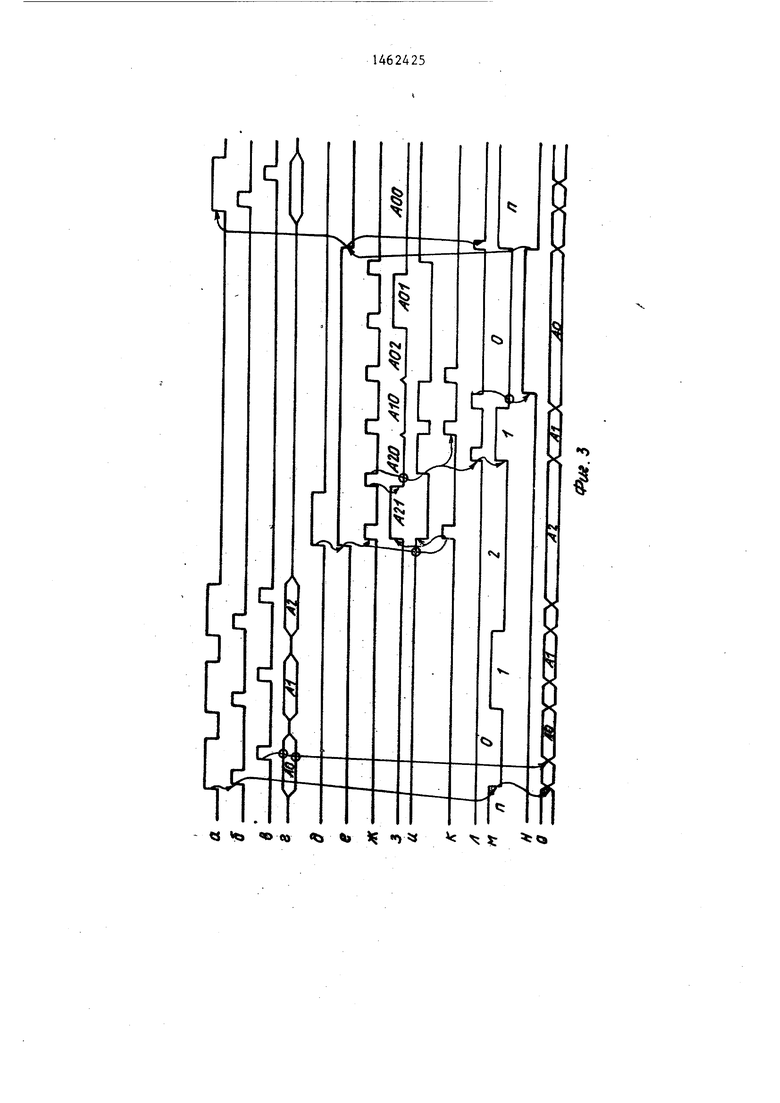

На фиг, 4 обозначены: q - сигналы синхрогенератора 14 блока 3 синхронизации; 5 - сигнал запроса на регенерацию на входе 3,3; Ь - сигнал управ

декремента счетчика 1 на выходе 3,7.

Устройство реализовано для управления регенерацией динамической памяти с семиразрядным строчным адресом регенерации, разбитой на 8 зон. Переход от зоны к зоне определяется переключением трех старших разрядов на втором-выходе блока 8 памяти адресов. Перебор строчных адресов внутри зоны - переключением четырех разрядов счетчика 2,

Устройство работает cлeдyюш м образом,

В режиме внешних обращений к дина- мической памяти на входе 4 устройства выставляются записи границ зон (фиг. За), По ним блок 3 синхронизации вырабатывает на выходе 3,4 инкремент счетчика 1 зон (фиг, ЗБ) и на выходе 3,8 сигнал записи в блок 8 памяти (фиг. 36), По первому из сигналов инкремента счетчик 1 из состояния п (код Все единицы), где п+1 - ко

5

0

личество зон, в которые он был установлен в конце работы в режиме регенерации, устанавливается в нулевое состояние (фиг, 3м), По адресу, заданному состоянием счетчика 1 после инкремента, в блок 8 памяти записываются адреса верхних границ зон (фиг, 32,о), которые на входе 12 сопровождаются сигналом управления на входе 4,

Нижние границы зон определяются 5 по трем старшим разрядам строчного адреса регенерации при нулевом состоянии его четырех младших разрядов, Тр иггер 9 в режиме внешних обращений установлен в нулевое состояние (фиг, i 39), счетчик 2 адресов регенерации выдает сигнал переноса (фиг, Зи) .

После записи адресов границ зон устройство переводится в режим регенерации сигналов с входа Ш (фиг. За), по которому триггер 9 устанавливается в единичное состояние (фиг, Зе), Блок синхронизации начинает выдавать импульсы регенерации со своего выхода 3,6 (фиг. Зж), По сигналу переноса

0

5

счетчика 2 блок 3 с выхода 3.9 сигнал установки счетчика 2 (фиг. Зк) , совпадающий во времени с пер.вым из сигналоБ декремента счетчика 2 (фиг, Зж) , и в счетчик 2 заносится состояние четырех младших разрядов выходной информации блока 8 памяти (фиг. 3). Затем-счетчик 2 декремен1462425

выдает (фиг. ) устанавливается триггер 19 (фиг. 4 ) - выдается сигнап подтверждения. Он через элемент И 15 устанавливает- счетчик 17 в нулевое состояние, и генерация управляющих сиг- напов блокируется. По сигналу подтверждения снимается сигнал на входе 3.1, что, в свою очередь, сбрасывает

тируется до перехода в нулевое состо- IQ триггер 19.

яние, при котором он выдает сигнал обратного переноса, покоторому блок 3 синхронизации выдает со своего выхода 3,7 декремент счетчика 1 зон (фиг. Зл). Ло переключению счетчика I (фиг. З/м) из блока 8 памяти выбирается адрес очередной границы зоны (.фиг, Зо) . Затем г-отадшие разряды адреса перезаписываются в счетчик 2 и начинается перебор строчных адресов- новой зоны.

Счетчик 1 декрементируется до ус-- тановления в нулевое состояние, по которому от выдает сигнал переноса

20 на выходы 3,7, 3.9 (фиг. 4л ,л). при единичном состоянии триггера 20 (фиг, 4к), Триггер 20 устанавливается сигналом переноса счетчика 2 на выходе 3.2 и сбрасывается задним фронтом

(фиг. Зн). Это состояние соответству- 25 управляющего сигнала с первого дешифет последней из задействованных зон динамической памяти. После перебора ее строчных адресов выдается очередной сигнал декремента ,счетчика 1 и он устанавливается в состояние п, а его сигнал переноса сбрасывается, по этому сбросу сбрасывается триггер 9 (фиг, Зе,н). Дальнейшая выдача импульсов регенерации и сигналов установки и декремента счетчиков 1,2 блокируется, Счетчик 1 остается в состояния п, а счетчик- 2 - в нулевом и выдает сигнал переноса. Нулевым состоянием триггера 9 задается запрос на выполнение регенерации. По нему могут выдаваться новые границы зон,

Блок 3 синхронизации работает следующим образом.

Импудьсы с выхода генератора 14 (фиг, 4о() поступают на счетный вход счетчика 17, При наличии запроса на регенерацию (фиг, 45) и по управляющему сигналу с выхода 3,1 блока 3 (фиг, 4Ь) со счетчика 17 снимается сброс и начинается пересчет синхроим ратора (фиг. 4, к). Сбросом сигнала на выходе 3.3 сбрасывается счетчик 1 7 и блокируется поступление сигналов с выходов коммутатора 2 и элемента

30 i 16.

Таким образом, устройство по заданным границам задействованных зон динамической памяти ведет ее строчную регенерацию без затрат времени на перебор неиспользуемых адресов. При этом достигается уменьшение времени занятости памяти регенерацией и тем самым более эффективное использование машинного времени, Q Так, если при 128 строчных адресах .будет задействован только последний столбец памяти, то для его регенерации в устройстве он определяется в первой же выборке из блока памяти адресов.

45

Фо-рмула изобретения

Устройство для управления регенера- цией динамической памяти со свободными пульсов (фиг. 4-2.). По состояниям счет- зонами, содержащее блок памяти, блок син- чика 17 дешифратор 18, стробируемый синхроимпульсом, вырабатывает управляющие сигналы на своих выходах (фиг, 4а-ж) . Управляющие сигналы с двух первых выходов дешифратора 18 (фиг, 34,е) через коммутатор 22 поступают на выходы 3,4 и 3,8, По сигналу с третьего выхода дешифратора 18

55

хронизации, счетчик адресов, установочный вход и выход переноса которого подключены соответственно к первому выходу и к первому входу блока синхронизации, второй вход которого является входом записи устройства, второй выход блока синхронизации подключен к входу записи блока памяти, инСброс со счетчика 17 снимается также по сигналу с вхо да 3.3 работы в режиме регенерации. При этом поступление управляющих сигналов на выходы 3.4, 3.8 блокируется отсутствием сигнала на входе 3.1, а на выход 3.6 через элемент И 16 подаются импульсы регенерации (фиг, 4ж) , Коммутатор 21 выдает управляюаще сигналы

на выходы 3,7, 3.9 (фиг. 4л ,л). при единичном состоянии триггера 20 (фиг, 4к), Триггер 20 устанавливается сигналом переноса счетчика 2 на выхое 3.2 и сбрасывается задним фронтом

правляющего сигнала с первого дешиф ратора (фиг. 4, к). Сбросом сигнала на выходе 3.3 сбрасывается счетчик 1 7 и блокируется поступление сигналов с выходов коммутатора 2 и элемента

0 i 16.

Таким образом, устройство по заданным границам задействованных зон динамической памяти ведет ее строчную регенерацию без затрат времени на перебор неиспользуемых адресов. При этом достигается уменьшение времени занятости памяти регенерацией и тем самым более эффективное использование машинного времени, Q Так, если при 128 строчных адресах .будет задействован только последний столбец памяти, то для его регенерации в устройстве он определяется в первой же выборке из блока памяти адресов.

5

Фо-рмула изобретения

Устройство для управления регенера- цией динамической памяти со свободными зонами, содержащее блок памяти, блок син-

5

хронизации, счетчик адресов, установочный вход и выход переноса которого подключены соответственно к первому выходу и к первому входу блока синхронизации, второй вход которого является входом записи устройства, втоУстройство для управления регенера- цией динамической памяти со свободными зонами, содержащее блок памяти, блок син-

рой выход блока синхронизации подключен к входу записи блока памяти, ин(}юрмационные входы и выходы первой Группы которого являются соответственно адресными входами и адресными выходами старших разрядов устройства третий выход блока синхронизации является выходом си;гнала подтверждения записи адреса границы зоны, о т л и- йающееся тем, что, с целью Ьовьшзения быстродействия, оно содер- счетчик зон и триггер, установоч- {тый вход которого является входом ре- Кима устройства, выход триггера является выходом запроса регенерации устройства и подютючен к третьему

входу блока синхронизации, четвертый выход которого является выходом импульсов регенерации устройства и подключен к счетному входу счетчика адресов, ин(}юрмационные входы которого подключены к информационным выходам второй группы блока памяти, адресные входы которого подключены к информационным выходам счетчика зон, выход заема которого подключен к входу сброса триггера, пятый и шестой выходы блока синхронизации подключены соответственно к входу сложения и к

входу вычитания счетчика зон.

«Ч «о ад i « ; Jt «s

| Устройство для управления регенерацией оперативного накопителя | 1984 |

|

SU1198474A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-13—Подача