Јъ 1 4

4

Изобретение относится к вычислительной технике, и может быть использовано при построении оперативных запоминающих устройств (ОЗУ) на основе эле-ментов полупроводниковой динамической памяти.

Цель изобретения - расширение области применения устройства за счет регенерации области памяти от задан- ного адреса до последнего адреса.

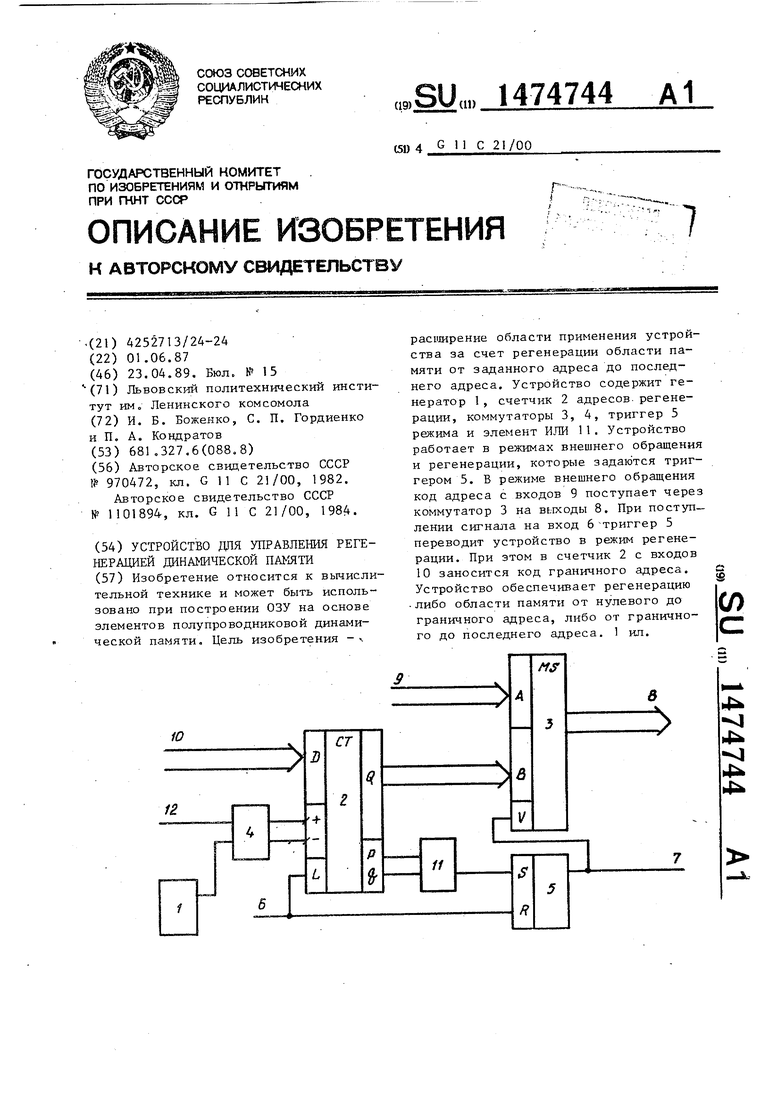

На чертеже представлена функциональная схема предлагаемого устройства .

Устройство содержит генератор 1 и счетчик 2 адресов регенерации, первы 3 и второй 4 коммутаторы, триггер 5 режима, вход 6 требования регенерации устройства, выход 7 режима устройства, выходы 8 устройства, первые входы 9 адреса обращения, входы 10 граничного адреса устройства, элемент ИЛИ 11 и вход 12 режима регенерации.

По входу 6 устройство переводится в режим регенерации. По выходу 7 определяются режимы регенерации или внешнего обращения, в которых работает устройство. С выхода 8 задаются строчные адреса внешних обращений

или регенерации. По входу 9 поступают строчные адреса внешних обращений По входу 10 задается адрес границы задействованного объема ОЗУ, по входу 1 2 - первый или второй режимы ре- генерации.

Устройство работает следующим образом.

При состоянии логической 1 на выходе триггера 5 устройство работа- ет в режиме внешнего обмена. Коммутатор 3 подключает строчные адреса внешних обращений с входа 9 на выход 8.

По сигналу обращения к устройст- ву, синхронизированному с тактовыми импульсами генератора 1, триггер 5 сбрасывается в логический О, а в счетчике 2 устанавливается адрес границы задействованного объема ОЗУ. Коммутатор 3 подключает на выход 8 информационный выход счетчика 2. Устройство переходит в режим регенера|ЦИИ.

В первом режиме регенерации по сигналу с входа 12 второй коммутатор 4 подключает к вычитающему входу счетчика 2 выход генератора 1, а на суммирующем входе устанавливает ло

«j 20

25 30

ос

до

5

-

0

пгче.гкую 1. Выход прямого переноса счетчика бпокируется. По сигналам генератора 1 счетчик 2 ведет реверсивный перебор строчных адресов, начиная с адреса границы зоны и кончяя начальным адресом ОЗУ. По его достижении сигнал з.чема счетчика 2 через элемент ИЛИ 11 поступает на установку триггера 5 и устройство вновь переходит в режим внешнего обращения.

Во втором режиме регенерации коммутатор 4 подключает выход генератора 1 к суммирующему входу счетчика 2. Логическая 1 устанавливается на вычитающем входе. Блокируется выход заема. Счетчик 2 перебирает строчные адреса, начиная с адреса границы зоны, до конечного адреса ОЗУ. После этого сигнал перекоса счетчика 2 через элемент ИЛИ 1 устанавливает триггер 5 в 1.

Таким образом в устройстве производится восстановление информации как в ОЗУ от нулевого до граничного адресов, так и в объеме от/граничного до последнего адресов.

Формула изобретения

Устройство для управления регече

рацией динамической памяти, содержащее первый и второй коммутаторы, г - счетчик адресов регенерации, триггер режима, генератор, причем информационные входы первой группы и выходы первого коммутатора являются соответственно адресными входами и адресными выходами устройства, информационные входы второй группы первого коммутатора подключены к информационным выходам счетчика адресов регенерации, вход сброса триггера режима является входом требования регенерации, выход триггера режима подключен к управляющему входу первого коммутатора и является выходом режима устройства, отличающееся тем, что, с целью расширения области применения устройства за счет регенерации области памяти от заданного адреса до последнего адреса, оно содержит элемент ИЛИ, первый и второй входы которого подключены соответственно к выходу переноса и выходу заема счетчика адресов регенерации, вход суммирования и вход вычитания которого подключены соответственно к первому и

314747444

второму пыход;1м второго коммутатора,регенерации устройства н входлмм грлинформационный вход которого подклю-ничного адреса устройства, вход рочен к выходу генератора, а управляю- жима счетчика адресов регенерации

щий вход второго коммутатора и инфор- подключен к входу сброса триггера ремационные входы счетчика адресов яв-жима, вход установки которого подклшляются соответственно входом режимачен к выходу элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения и регенерации динамической памяти | 1989 |

|

SU1735857A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1608752A1 |

| Устройство для регенерации динамической памяти со свободными зонами | 1989 |

|

SU1672529A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для регенерации динамической памяти | 1987 |

|

SU1497637A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении ОЗУ на основе элементов полупроводниковой динамической памяти. Цель изобретения - расширение области применения устройства за счет регенерации области памяти от заданного адреса до последнего адреса. Устройство содержит генератор 1, счетчик 2 адресов регенерации, коммутаторы 3,4,триггер 5 режима и элемент ИЛИ 11. Устройство работает в режимах внешнего обращения и регенерации, которые задаются триггером 5. В режиме внешнего обращения код адреса с входов 9 поступает через коммутатор 3 на выходы 8. При поступлении сигнала на вход 6 триггер 5 переводит устройство в режим регенерации. При этом в счетчик 2 с входов 10 заносится код граничного адреса. Устройство обеспечивает регенерацию либо области памяти от нулевого до граничного адреса, либо от граничного до последнего адреса. 1 ил.

| Устройство для управления регенерацией | 1981 |

|

SU970472A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Динамическое запоминающее устройство с зонами свободной памяти | 1982 |

|

SU1101894A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1989-04-23—Публикация

1987-06-01—Подача