Изобретение относится к вычислительной технике и может быть использовано при вычислительных системах различного назначения.

Целью изобретения является повышение скорости обмена между централь ным вычислительным (ЦВ) и интеллектуальными контроллерами (ИК) за счет аппаратурной реализации процедур обмена.

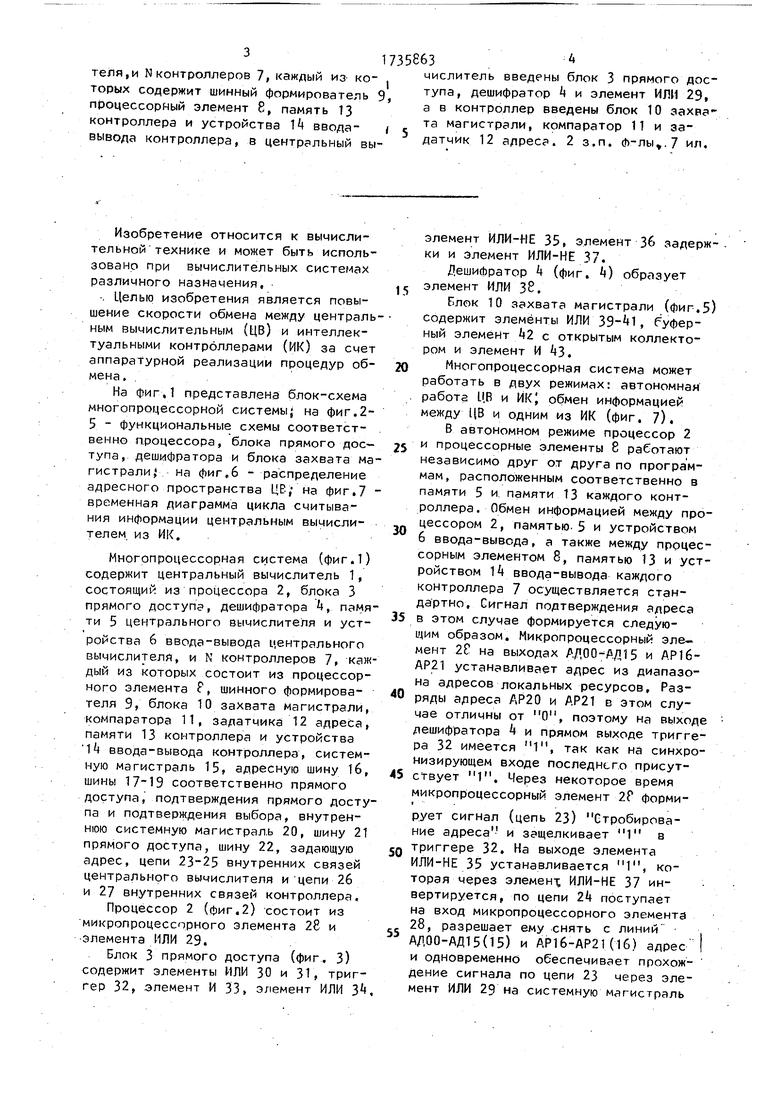

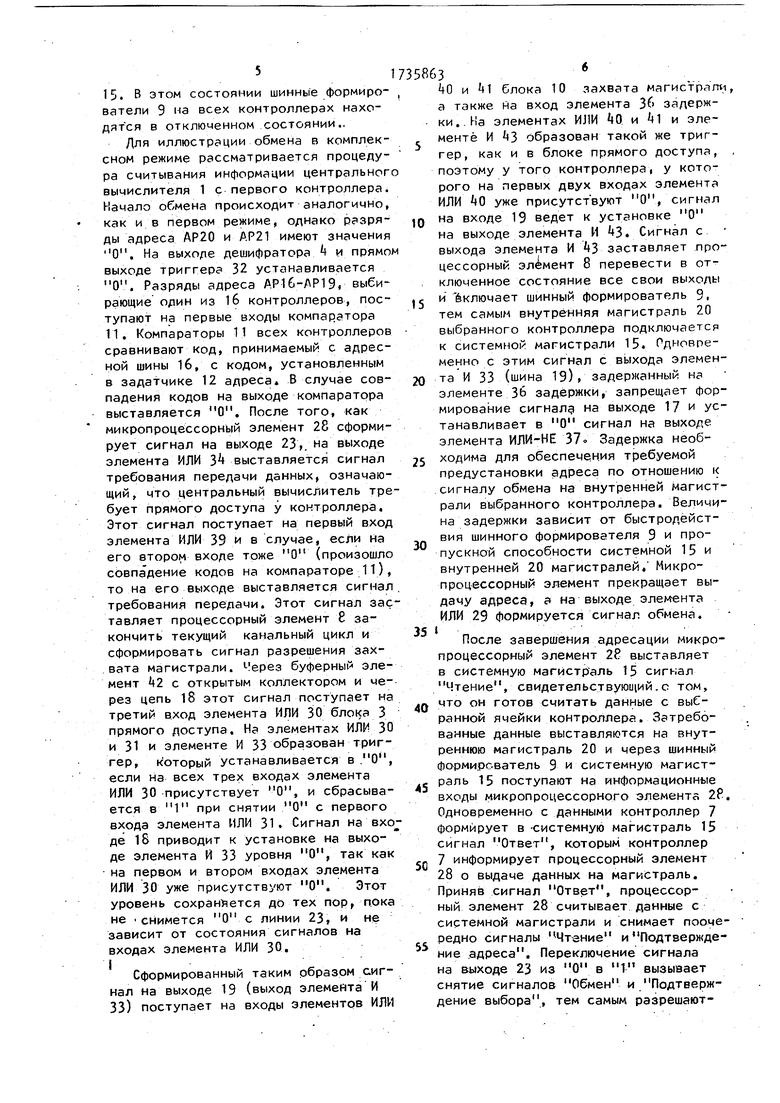

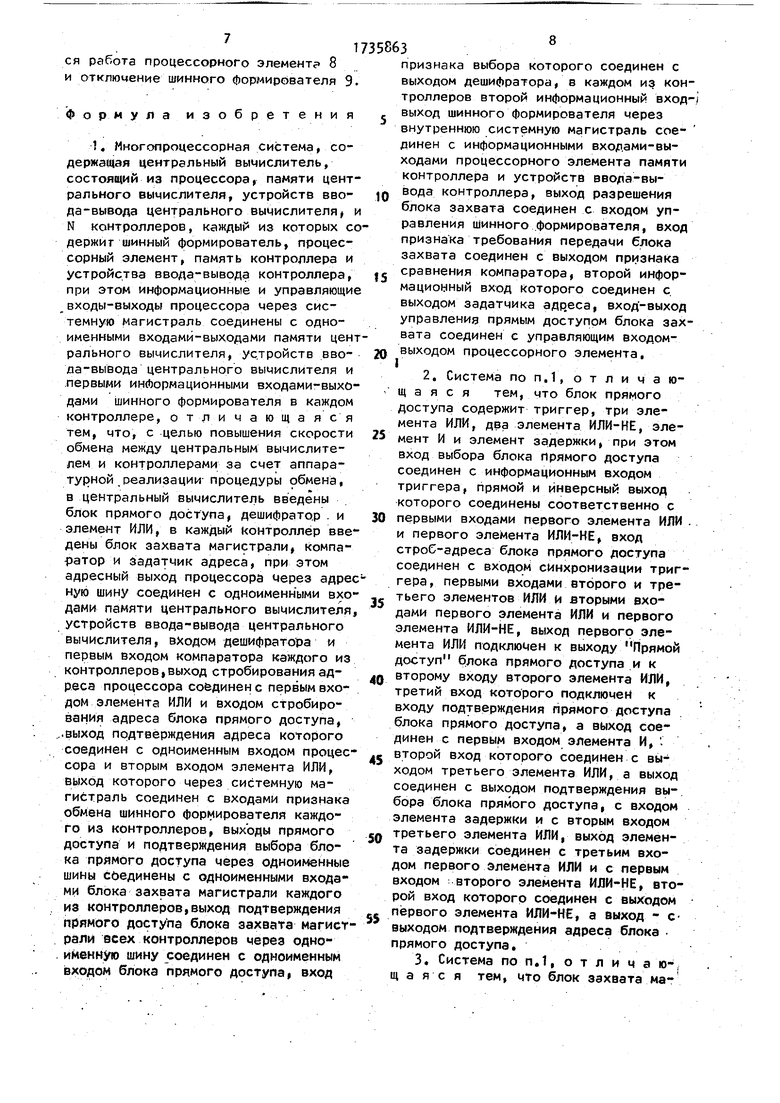

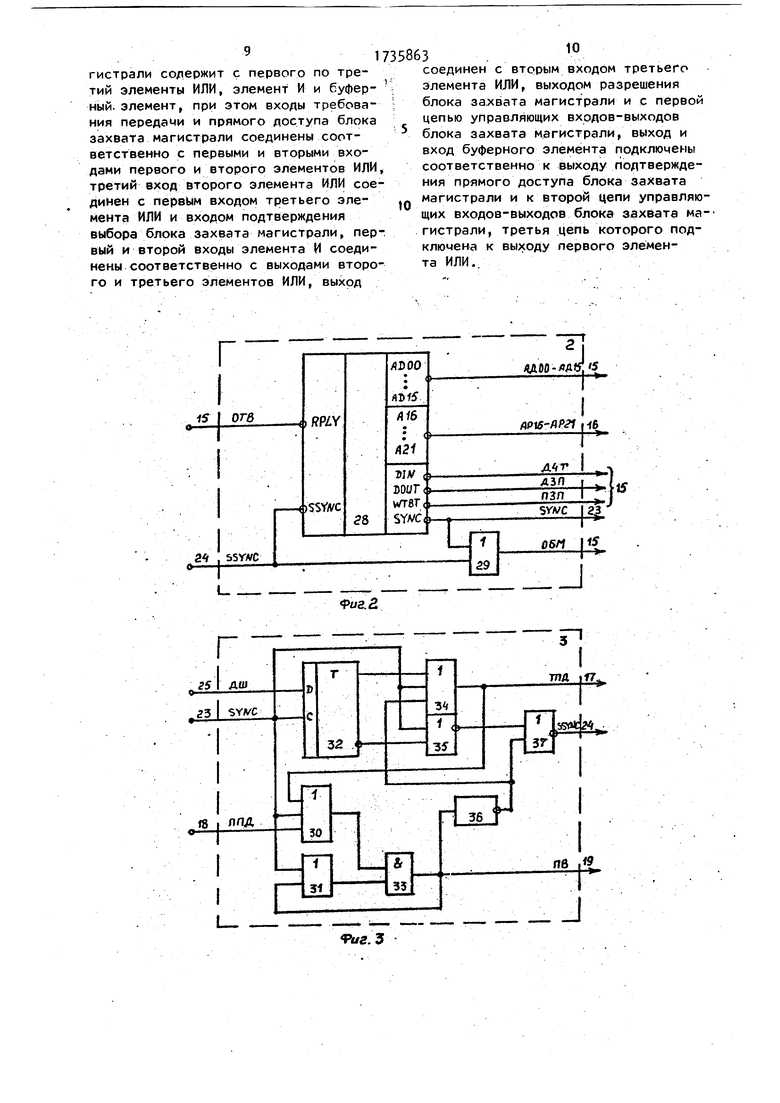

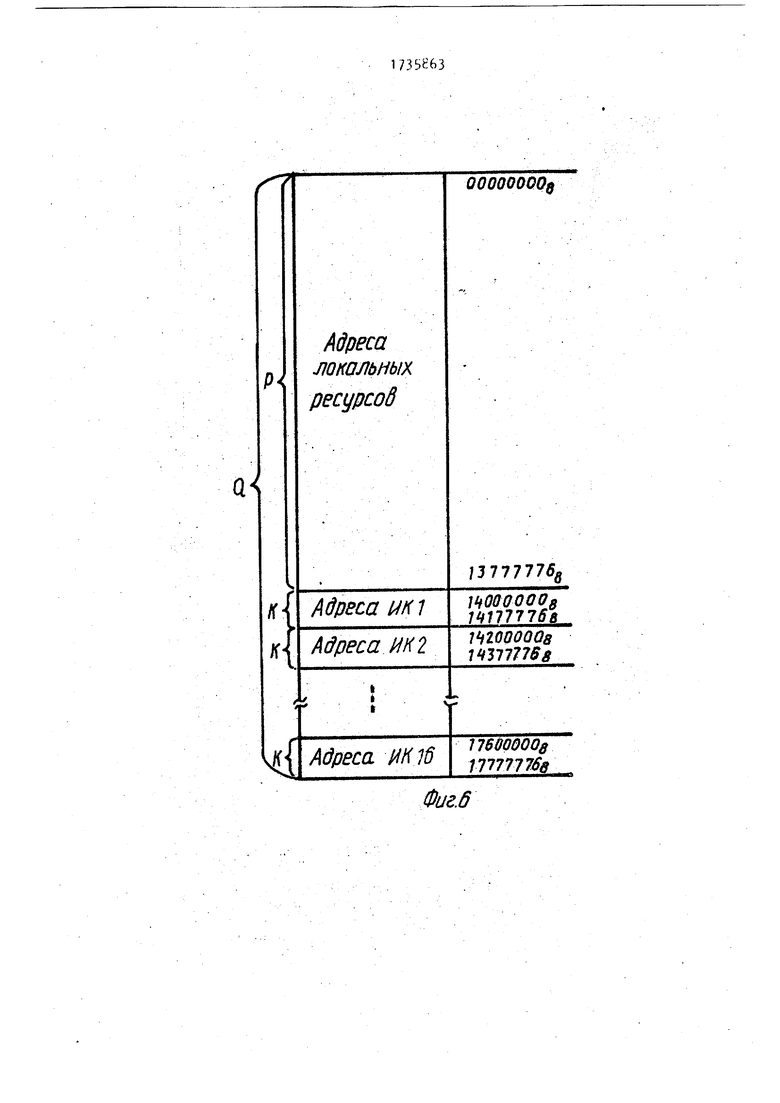

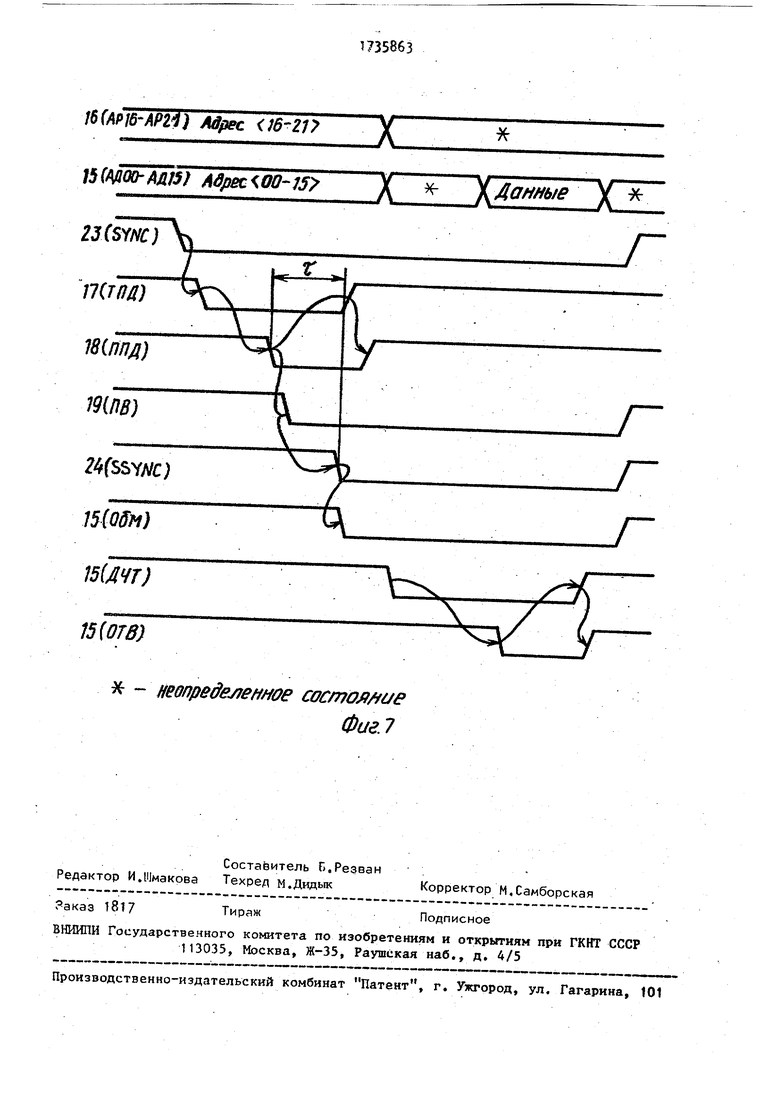

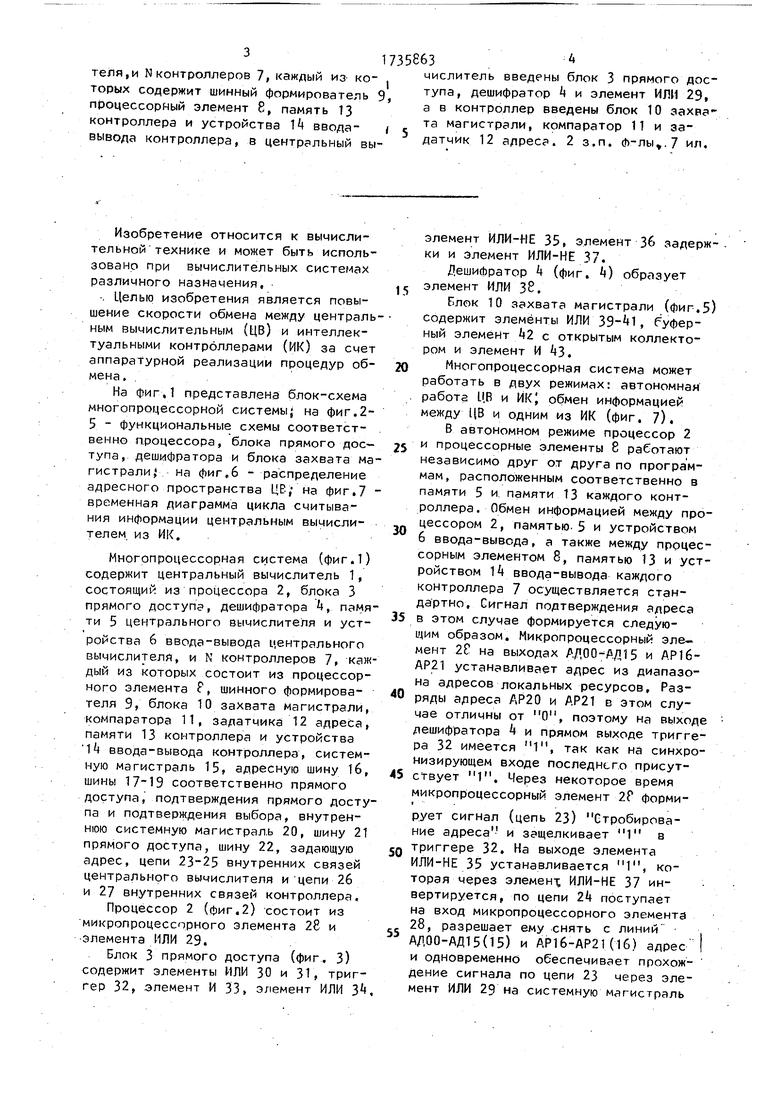

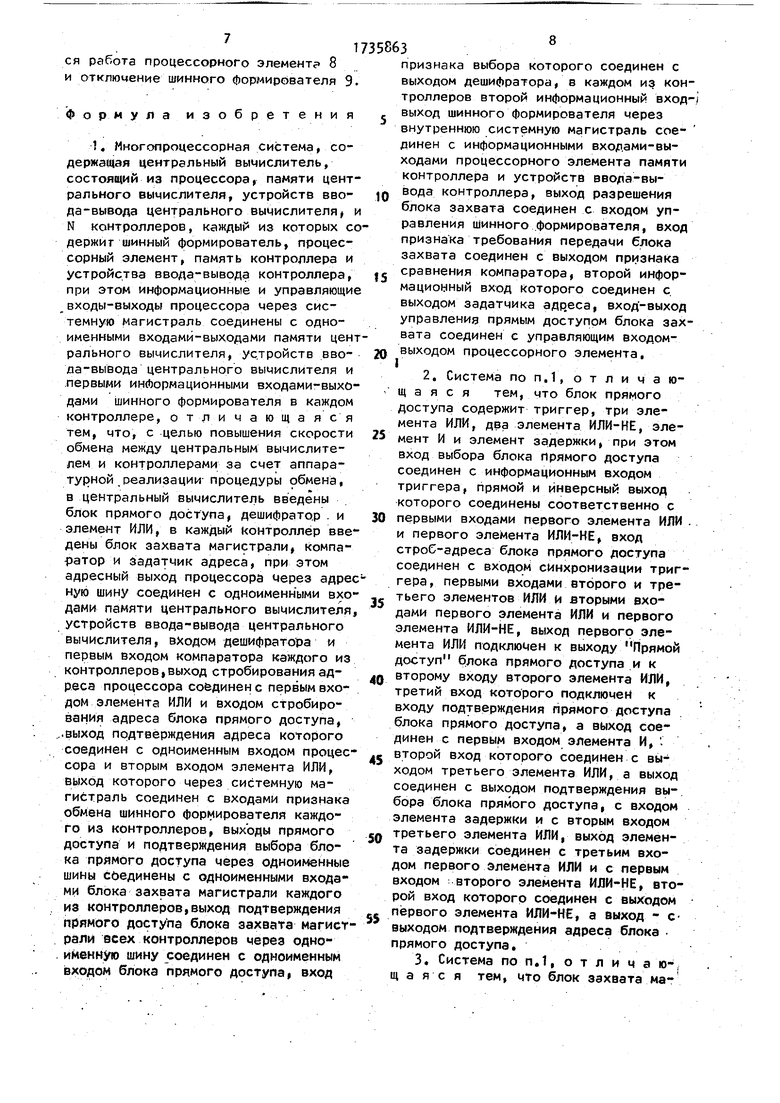

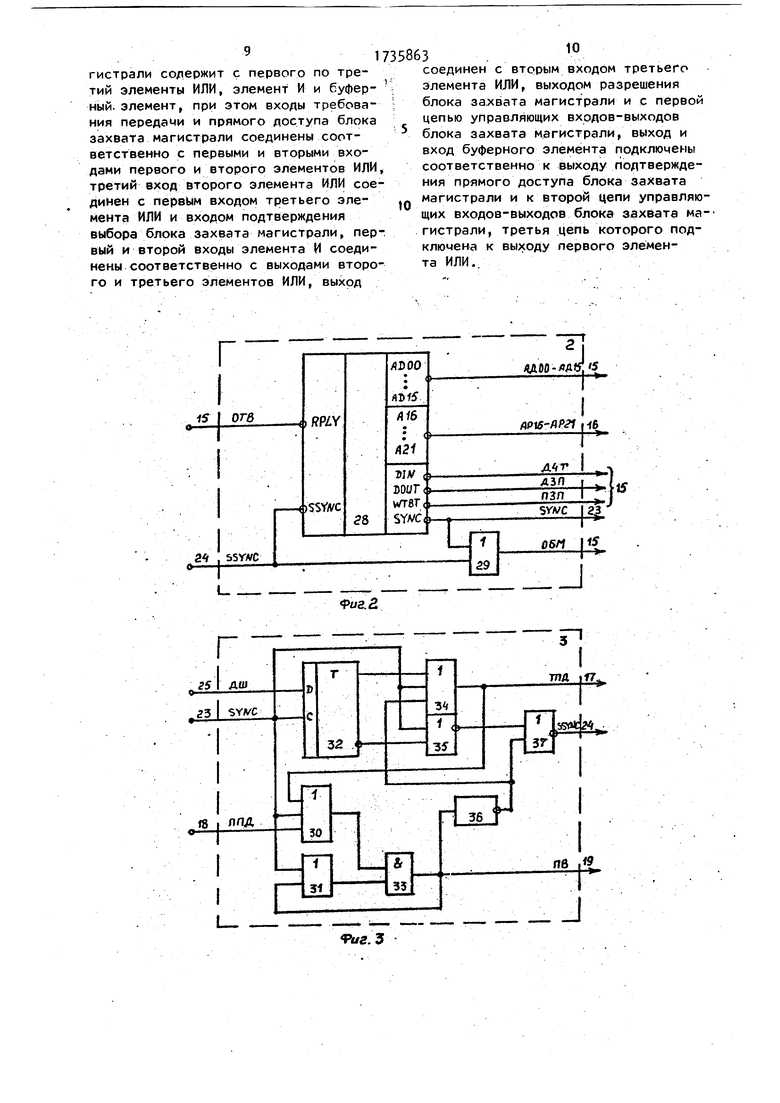

На фиг,1 представлена блок-схема многопроцессорной системы; на фиг.2- 5 - функциональные схемы соответственно процессора, блока прямого доступа, дешифратора и блока захвата ма гистрали} на фиг,6 - распределение адресного пространства ЦВ/ на фиг.7 временная диаграмма цикла считывания информации центральным вычислителем из ИК,

Многопроцессорная система (фиг.1) содержит центральный вычислитель 1, состоящий из процессора 2, блока 3 прямого доступе, дешифратора 4, памяти 5 центрального вычислителя и устройства 6 ввода-вывода центрального вычислителя, и N контроллеров 1, каждый из которых состоит из процессорного элемента Г, шинного формирователя Э, блока 10 захвата магистрали, компаратора 11, задатчика 12 адреса, памяти 13 контроллера и устройства 14 ввода-вывода контроллера, системную магистраль 15, адресную шину 16, шины 17-19 соответственно прямого доступа, подтверждения прямого доступа и подтверждения выбора, внутреннюю системную магистраль 20, шину 21 прямого доступа, шину 22, задающую адрес, цепи 23-25 внутренних связей центрального вычислителя и цепи 26 и 27 внутренних связей контроллера.

Процессор 2 (фиг.2) состоит из микропроцессорного элемента 28 и элемента ИЛИ 29.

Блок 3 прямого доступа (фиг. 3) содержит элементы ИЛИ 30 и 31, триггер 32, элемент И 33, элемент ИЛИ 34

0

элемент ИЛИ-НЕ 35, элемент 36 задержки и элемент ИЛИ-НЕ 37.

Дешифратор 4 (фиг. 4) образует

$ элемент ИЛИ 38.

Блок 10 захвата магистрали (фиг.5) содержит элементы ИЛИ 39-41, буферный элемент 42 с открытым коллектором и элемент И 43.

0 Многопроцессорная система может работать в двух режимах: автономная работа ЦВ и HKJ обмен информацией между ЦВ и одним из ИК (фиг. 7). В автономном режиме процессор 2

5 и процессорные элементы 8 работают независимо друг от друга по программам, расположенным соответственно в памяти 5 и памяти 13 каждого контроллера. Обмен информацией между процессором 2, памятью 5 и устройством 6 ввода-вывода, а также между процессорным элементом 8, памятью 13 и устройством 14 ввода-вывода каждого контроллера 7 осуществляется стандартно. Сигнал подтверждения адреса

5 в этом случае формируется следующим образом. Микропроцессорный элемент 2 на выходах АДОО-АД15 и АР16- АР21 устанавливает адрес из диапазона адресов локальных ресурсов, Раз0 ряды адреса АР20 и АР21 в этом случае отличны от О, поэтому на выходе дешифратора 4 и прямом выходе триггера 32 имеется 1, так как на синхронизирующем входе последнего присут5 ствует 1. Через некоторое время микропроцессорный элемент 2Р формиi

рует сигнал (цепь 23) Стробирова- ние адреса и защелкивает 1 в п триггере 32, На выходе элемента ИЛИ-НЕ 35 устанавливается 1, которая через элемент, ИЛИ-НЕ 37 инвертируется, по цепи 2k поступает на вход микропроцессорного элемента 28, разрешает ему снять с линий АДОО-АД1505) и АР16-АР21(16) адрес и одновременно обеспечивает прохождение сигнала по цепи 23 через элемент ИЛИ 29 на системную магистраль

5

15. В этом состоянии шинные формиро- ватели 9 на всех контроллерах находятся в отключенном состоянии..

Лля иллюстрации обмена в комплек- сном режиме рассматривается процедура считывания информации центральног вычислителя 1 с первого контроллера. Начало обмена происходит аналогично, как и в первом режиме, однако разря- ды адреса АР20 и АР21 имеют значения О. На выходе дешифратора Ь и прямо выходе триггера 32 устанавливается О. Разряды адреса АР16-АР19, выбирающие один из 16 контроллеров, пос- тупают на первые входы компаратора 11. Компараторы 11 всех контроллеров сравнивают код, принимаемый с адресной шины 16, с кодом, установленным в задатчике 12 адреса В случае сов- падения кодов на выходе компаратора выставляется О. После того, как микропроцессорный элемент 28 сформирует сигнал на выходе 23,. на выходе элемента ИЛИ 3 выставляется сигнал требования передачи данных, означающий, что центральный вычислитель требует прямого доступа у контроллера. Этот сигнал поступает на первый вход элемента ИЛИ 33 и в случае, если на его втором входе тоже О (произошло совпадение кодов на компараторе 11), то на его выходе выставляется сигнал требования передачи. Этот сигнал заставляет процессорный элемент 8 закончить текущий канальный цикл и сформировать сигнал разрешения захвата магистрали. иерез буферный элемент k2 с открытым коллектором и через цепь 18 этот сигнал поступает на третий вход элемента ИЛИ 30 блока 3 прямого доступа. На элементах ИЛИ 30 и 31 и элементе И 33 образован триггер, который устанавливается в О, если на всех трех входах элемента ИЛИ 30 присутствует О, и сбрасывается в 1 при снятии О с первого входа элемента ИЛИ 31. Сигнал на входе 1S приводит к установке на выходе элемента И 33 уровня О, так как на первом и втором входах элемента ИЛИ 30 уже присутствуют О. Этот уровень сохраняется до тех пор, пока не снимется О с линии 23, и не зависит от состояния сигналов на входах элемента ИЛИ 30.

Сформированный таким образом он нал на выходе 19 (выход элемента И 33) поступает на входы элементов ИЛИ

735863

,

, JQ jj 2Q 25 55

40 и Н блока 10 захвата магистрлли, а также на вход элемента 36 задержки. На элементах ИЛИ 0 и 1 и элементе И Ц$ образован такой же триггер, как и в блоке прямого доступа, , поэтому у того контроллера, у которого на первых двух входах элемента ИЛИ 0 уже присутствуют О, сигнал на входе 19 ведет к установке О на выходе элемента И +3. Сигнал с выхода элемента И A3 заставляет процессорный элемент 8 перевести в отключенное состояние все свои выходы и включает шинный формирователь 9, тем самым внутренняя магистраль 20 выбранного контроллера подключается к системной магистрали 15. Одновременно с этим сигнал с выхода элемента И 33 (шина 19), задержанный на элементе 36 задержки, запрещает формирование сигнала на выходе 17 и устанавливает в О сигнал на выходе элемента ИЛИ-НЕ 37° Задержка необходима для обеспечения требуемой предустановки адреса по отношению к сигналу обмена на внутренней магистрали выбранного контроллера. Величина задержки зависит от быстродействия шинного формирователя 9 и пропускной способности системной 15 и внутренней 20 магистралей. Микропроцессорный элемент прекращает выдачу адреса, а на выходе элемента ИЛИ 29 формируется сигнал обмена.

35 п

После завершения адресации микропроцессорный элемент 28 выставляет в системную магистраль 15 сигнал Чтение, свидетельствующий.с том, что он готов считать данные с выбранной ячейки контроллера. Затребованные данные выставляются на внутреннюю магистраль 20 и через шинный формирователь 9 и системную магист.f раль 15 поступают на информационные входы микропроцессорного элемента 2Р. Одновременно с данными контроллер 7 формирует в -системную магистраль 15 сигнал Ответ, которым контроллер 7 информирует процессорный элемент 28 о выдаче данных на магистраль. Приняв сигнал Ответ, процессорный элемент 28 считывает данные с системной магистрали и снимает пооче- оедно сигналы |(Чтзние и Подтверждение адреса. Переключение сигнала на выходе 23 из О в 1 вызывает снятие сигналов Обмен и Подтверждение выбора, тем самым разрешают30

40

50

ся работа процессорного элемента 8 и отключение шинного формирователя 9.

Формула изобретения

1

1. Многопроцессорная система, содержащая центральный вычислитель, состоящий из процессора, памяти центрального вычислителя, устройств ввода-вывода центрального вычислителяt и N контроллеров, каждый из которых содержит шинный формирователь, процессорный элемент, память контроллера и устройства ввода-вывода контроллера, при этом информационные и управляющие входы-выходы процессора через системную магистраль соединены с одноименными входами-выходами памяти центрального вычислителя, устройств ввода-вывода центрального вычислителя и первыми информационными входами-выходами шинного формирователя в каждом контроллере, отличающаяся тем, что, с целью повышения скорости обмена между центральным вычислителем и контроллерами за счет аппаратурной реализации процедуры обмена, в центральный вычислитель введены блок прямого доступа, дешифратор и элемент ИЛИ, в каждый контроллер введены блок захвата магистрали, компаратор и задатчик адреса, при этом адресный выход процессора через адресную шину соединен с одноименными входами памяти центрального вычислителя, устройств ввода-вывода центрального вычислителя, входом дешифратора и первым входом компаратора каждого из контроллеров,выход стробирования адреса процессора соединен с первым входом элемента ИЛИ и входом стробирования адреса блока прямого доступа, .выход подтверждения адреса которого соединен с одноименным входом процессора и вторым входом элемента ИЛИ, выход которого через системную магистраль соединен с входами признака обмена шинного формирователя каждого из контроллеров, выходы прямого доступа и подтверждения выбора блока прямого доступа через одноименные шины соединены с одноименными входа ми блока захвата магистрали каждого из контроллеров,выход подтверждения прямого доступа блока захвата магистрали всех контроллеров через одноименную шину соединен с одноименным входом блока прямого доступа, вход

358638

признака выбора которого соединен с выходом дешифратора, в каждом ид контроллеров второй информационный вход-i выход шинного формирователя через внутреннюю системную магистраль соединен с информационными входами-выходами процессорного элемента памяти контроллера и устройств ввода-вывода контроллера, выход разрешения блока захвата соединен с входом управления шинного формирователя, вход признака требования передачи блока захвата соединен с выходом признака сравнения компаратора, второй информационный вход которого соединен с выходом задатчика aflqeca, вход-выход управления прямым доступом блока захвата соединен с управляющим входом- выходом процессорного элемента.

10

15

20

I

25

30

35

2.Система поп.1, отличающаяся тем, что блок прямого доступа содержит триггер, три элемента ИЛИ, два элемента ИЛИ-НЕ, элемент И и элемент задержки, при этом вход выбора блока прямого доступа соединен с информационным входом триггера, прямой и инверсный выход которого соединены соответственно с первыми входами первого элемента ИЛИ . и первого элемента ИЛИ-НЕ, вход строС-адреса блока прямого доступа соединен с входом синхронизации триггера, первыми входами второго и третьего элементов ИЛИ и вторыми входами первого элемента ИЛИ и первого элемента ИЛИ-НЕ, выход первого элемента ИЛИ подключен к выходу Прямой доступ блока прямого доступа и к

40 второму входу второго элемента ИЛИ, третий вход которого подключен к входу подтверждения прямого доступа блока прямого доступа, а выход соединен с первым входом элемента И, . второй вход которого соединен с выходом третьего элемента ИЛИ, а выход соединен с выходом подтверждения выбора блока прямого доступа, с входом элемента задержки и с вторым входом третьего элемента ИЛИ, выход элемента задержки соединен с третьим входом первого элемента ИЛИ и с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ, а выход - с- выходом подтверждения адреса блока . прямого доступа.

3.Система поп.1,отличаю- щ а я с я тем, что блок захвата ма45

50

55

гистрали содержит с первого по третий элементы ИЛИ, aneMeHf И и буфер- ный. элемент, при этом входы требования передами и прямого доступа блока захвата магистрали соединены соответственно с первыми и вторыми входами первого и второго элементов ИЛИ, третий вход второго элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и входом подтверждения выбора блока захвата магистрали, пер-. вый и второй входы элемента И соединены соответственно с выходами второго и третьего элементов ИЛИ, выход

1735863

10

соединен с вторым входом третьего элемента ИЛИ, выходом разрешения блока захвата магистрали и с первой цепью управляющих входов-выходов блока захвата магистрали, выход и вход буферного элемента подключены соответственно к выходу подтверждения прямого доступа блока захвата магистрали и к второй цепи управляющих входов-выходов блока захвата ма-- гистрали, третья цепь которого подключена к выходу первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПРОЦЕССОРНАЯ СИСТЕМА ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2139566C1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179332C1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения процессора с общей магистралью | 1988 |

|

SU1606976A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем различного назначения. Целью изобретения является повышение скорости обмена между центральным вычислителем и контроллерами за счет аппаратурной реализации процедур обмена. Поставленная цель достигается тем, что в многопроцессорной системе, содержащей центральный вычислитель 1, состоящий из процессора 2, памяти 5 центрального вычислителя и устройства % ввода-вывода центрального вычисли-

йс/г.З

Г

IФиг 5

in

J

f93«Sf/l

/б (АР16-АРМ) Адрес 16-21

15(М зо-Адш лфес«ш-я )( Данные X 23(SWC) Vi /

/7Сш;

18(ППД)

W/IB)

Z4fssY c;

15(0&t)

Шчт)

1510ТВ)

- неопределенное сос/пол/tue

Фиг. 7

Составитель Б.Резван Редактор И.Шмакова Техред м.Дидык Корректор М,Самборская

Раказ 1817

Тираж

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

/

Г

г

ъ

Подписное

| Вейцман К | |||

| Распределенные системы мини- и микро-ЭВМ,/Пер, с англ | |||

| В.И.Шяудкулиса и В.А.Шапошникова | |||

| - М.: Финансы и статистика, 1982, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Флейшер Е.Г | |||

| Организация межпроцессорного обмена в УиПУ с подчиненными контроллерами | |||

| - Микропроцессорные средства и системы, 1987, И1 2, с | |||

| . | |||

Авторы

Даты

1992-05-23—Публикация

1988-08-01—Подача