(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования последовательного двоичного кода с интервалами ограниченной длины формата (2,7) | 1989 |

|

SU1741268A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1444762A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для контроля тестопригодных программ | 1990 |

|

SU1751767A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ЭЛЕМЕНТОВ КОНТУРНОГО ИЗОБРАЖЕНИЯ | 1991 |

|

RU2015560C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах регистрации цифровых сигналов, например, на магнитно- оптических дисках. Изобретение позволяет упростить устройство для декодирования последовательного двоичного кода с интервалами ограниченной длины формата (2,7). Устройство содержит сдвигающий регистр 1, элемент 2 памяти и вычислительный блок 3, реализующий булеву функцию И Ж + АД + ГЗ + ГЛ (где А,Г,Д,Ж,3, Л и И - значения логических переменных) , выполненный на элементе 8 2-2-2-2И-4ИЛИ-НЕ. 1 з.п.ф-лы, 3 ил.

Изобретение относится к вычисли- - тельной технике и может быть использовано в системах регистрации цифровых сигналов, например, на магнитно- оптических дисках.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее восьмиразрядный сдвигающий регистр, на выходах которого формируются сигналы, соответствующие восьми последним битам входной кодовой последовательности, последовательный вход сдвигающего регистра является информационным входом устройства, синхровход - первым тактовым входом устройства, а также комбинационную логическую схему, выполняющую логическую операцию с+еЫ- +bdf+af, выход которой подключен к входу элемента памяти, синхровход которого является вторым тактовым

входом устройства, а выход - выходом устройства.

Недостатком известного устройства является сложность.

Цель изобретения - упрощение устройства.

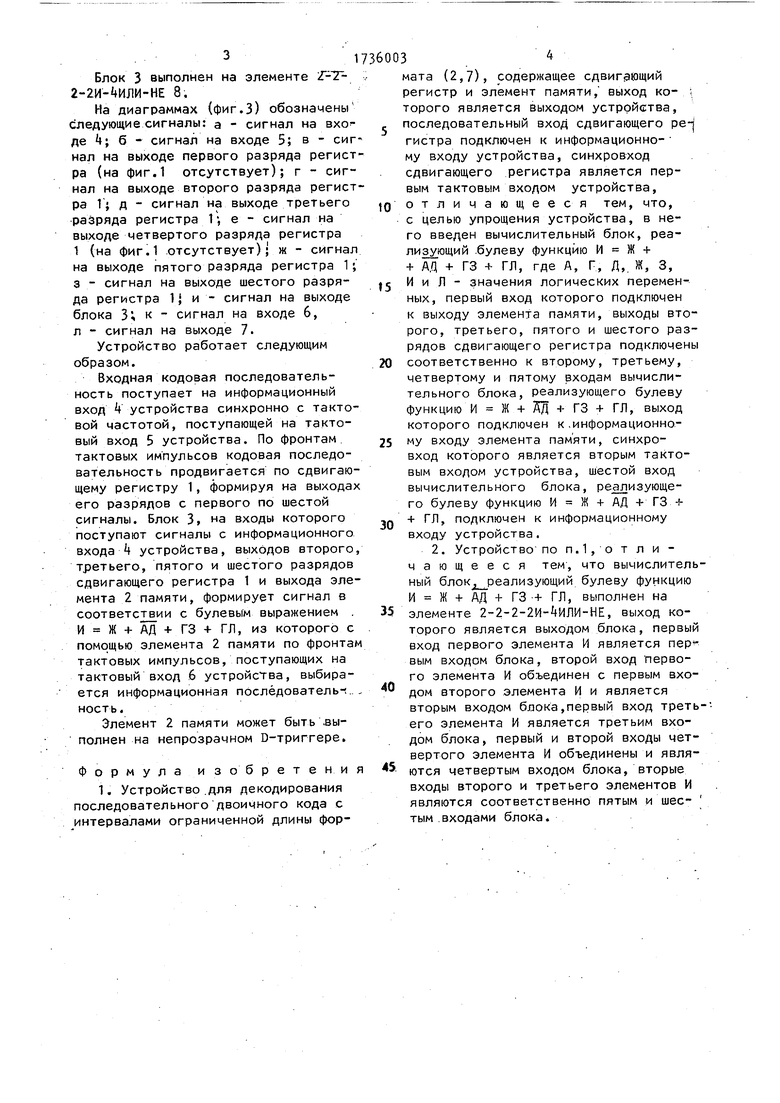

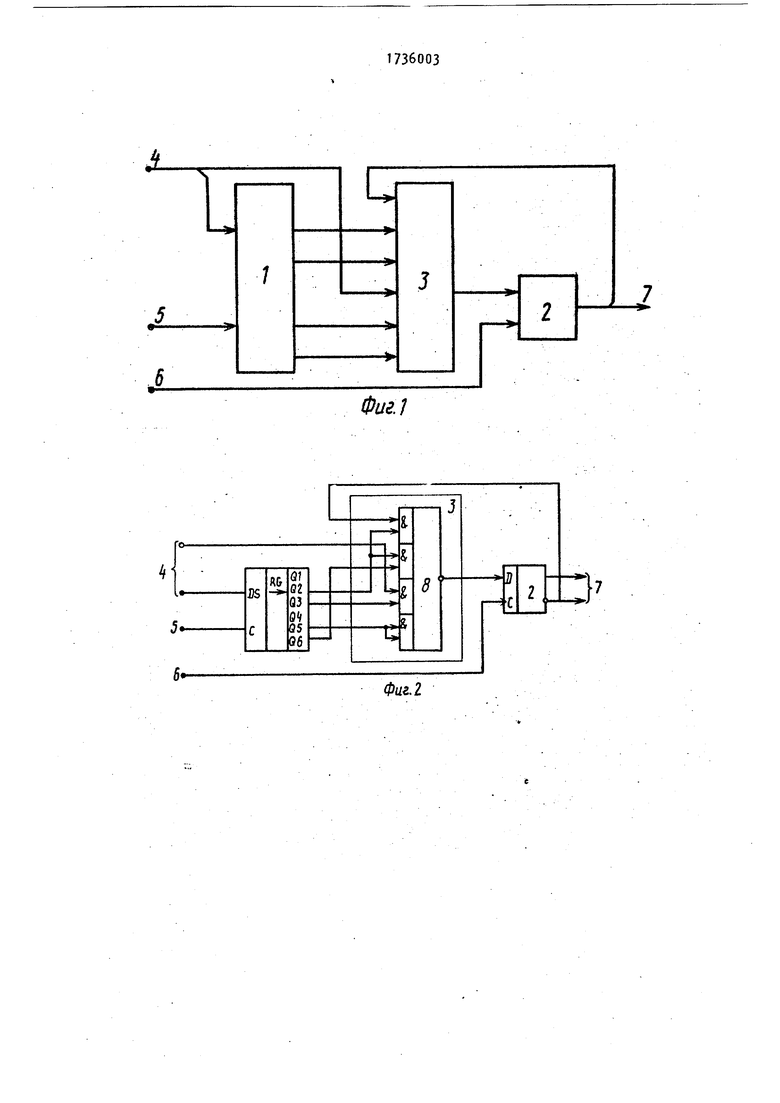

На фиг.1 представлена функциональная схема устройства; на фиг.2 - схема конкретного выполнения устройства; на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство содержит сдвигающий регистр 1, элемент 2 памяти, вычислительный блок 3,реализующий булеву функцию И Ж + АД + ГЗ + ГЛ, где А, Г, Д, Ж, Л и И - значения логических переменных.

Позициями 4-6 обозначены соответственно информационный вход, первый и второй тактовые входы устройства, позицией 7 - выход устройства.

J

со оъ

СдЭ

J 1

Блок 3 выполнен на элементе Е-Т- 2-2И-4 ИЛИ-НЕ 8.

На диаграммах (фиг.З) обозначены следующие сигналы: а - сигнал на входе ; б - сигнал на входе 5; в - сигнал на выходе первого разряда регист- ра (на фиг.1 отсутствует); г - сигнал на выходе второго разряда регистра 1; д - сигнал на выходе третьего разряда регистра Г; е - сигнал на выходе четвертого разряда регистра 1 (на фиг.1 отсутствует); ж - сигнал на выходе пятого разряда регистра 1; з - сигнал на выходе шестого разряда регистра 1} и - сигнал на выходе блока 3; к - сигнал на входе 6, л - сигнал на выходе 7.

Устройство работает следующим образом.

Входная кодовая последовательность поступает на информационный вход k устройства синхронно с тактовой частотой, поступающей на тактовый вход 5 устройства. По фронтам тактовых импульсов кодовая последовательность продвигается по сдвигающему регистру 1, формируя на выходах его разрядов с первого по шестой сигналы. Блок 3, на входы которого поступают сигналы с информационного входа k устройства, выходов второго, третьего, пятого и шестого разрядов сдвигающего регистра 1 и выхода элемента 2 памяти, формирует сигнал в соответствии с булевым выражением И Ж + АД + ГЗ + ГЛ, из которого с помощью элемента 2 памяти по фронтам тактовых импульсов, поступающих на тактовый вход 6 устройства, выбирается информационная последователь-: , ность.

Элемент 2 памяти может быть .выполнен на непрозрачном D-триггере.

Формула изобретения

мата (2,7), содержащее сдвигающий регистр и элемент памяти, выход которого является выходом устройства,

. последовательный вход сдвигающего pe-j гистра подключен к информационному входу устройства, синхровход сдвигающего регистра является первым тактовым входом устройства,

tg отличающееся тем, что, с целью упрощения устройства, в него введен вычислительный блок, реализующий булеву функцию И Ж + + Aq + ГЗ + ГЛ, где А, Г, Д, Ж, 3,

15 И и Л - значения логических переменных, первый вход которого подключен к выходу элемента памяти, выходы второго, третьего, пятого и шестого разрядов сдвигающего регистра подключены

20 соответственно к второму, третьему, четвертому и пятому входам вычислительного блока, реализующего булеву функцию И Ж + Дд н- ГЗ + ГЛ, выход которого подключен к информационно25 му входу элемента памяти, синхровход которого является вторым тактовым входом устройства, шестой вход вычислительного блока, реализующего булеву функцию И Ж + АД + ГЗ +

10 + подключен к информационному входу устройства.

35 элементе 2-2-2-2И-{(ИЛИ-НЕ, выход которого является выходом блока, первый вход первого элемента И является первым входом блока, второй вход первого элемента И объединен с первым входом второго элемента И и является вторым входом блока,первый вход третьего элемента И является третьим входом блока, первый и второй входы четвертого элемента И объединены и явля 5 ются четвертым входом блока, вторые входы второго и третьего элементов И являются соответственно пятым и шее- тым входами блока.

40

Ј009Ш

ФигЗ

| Авторское свидетельство СССР Vt , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Станок с циркулярной пилой | 1928 |

|

SU15768A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-05-23—Публикация

1989-03-28—Подача