Изобретение относится к вычислительной технике и может быть использовано для автоматизации процесса принятия решения при разработке и эксплуатации автоматизированных систем управления. Устройство позволяет повысить степень обоснованности решения за счет получения суммарной оценки на основании частных оценок признаков решения для различных условий функционирования системы

Известно устройство для выбора оптимальных решений, содержащее Е матриц из НХТ блоков памяти, где Е - количество признаков, характеризующих решение; Н - количество рассматриваемых решений; Т - количество параметров для оценки каждого признака и Е матриц из НХТ схем сравнения

Недостатком этого устройства является то, что оно не решает задачу получения суммарной оценки на основании частных оценок признаков решения.

Наиболее близким по технической сущности к предлагаемому является устройство

для выбора оптимальных решений, содержащее Е матриц из НХТ блоков памяти, где Е - количество признаков, характеризующих решение; Н - количество рассматриваемых решений, Т - количество параметров для оценки каждого признака, Е - матриц из НХТ схем сравнения, Т сумматоров, матрицу из НХТ сумматоров Е блоков задания минимального допустимого значения оценки К-го признака решения (К - 1, ,Е), блок индикации, причем выход К-го блока задания минимально допустимого значения оценки К-го признака решений (К 1Е) подключен к первым информационным входам всех схем сравнения К-й матрицы, выход Р-ro блока памяти (, . Н) М-й строки (М 1. .Т) матрицы подключен к второму информационному входу Р-й схемы сравнения М-й строки К-й матрицы, выход которой подключен к входу К-го слагаемого Р-ro сумматора М-й строки матрцы, выход которого подключен к входу М-го слагаемого Р-го сумматора, выход которого является Р-м выходом устройства

ч ел

ю

о о

для индикации суммарной с ценки Р-го решения.

Недостатком данного устройства является то, что оно не способно выбрать оптимальный вариант с учетсм различий в условиях функционирования системы. Кроме того, при сравнительно больших аппаратурных затратах функциональные возможности устройства-прототипа относительно малы.

Цель изобретения - расширение функциональных возможностей устройства, заключающихся в получении нескольких вариантов оценок решений по частным оценкам параметров, объединенных признаками для различных условий функционирования системы.

Известно, что применительно к управлению радиолокационной системой задача управления формируется в следующем общем виде. Пусть Функционирование системы описывается уравнением

Y(t)(T).N(T).M(z), где Y(t) - выходная функция РЛ системы, характеризующая качество рэдиолокацион- ной информации (эффективность РЛ системы) Y{t)eEy;

Х(г ) - функция, характеризующая полезные сигналы, отраженные от реальных объектов, Х(т)ЈЕх. t T;

Т - период цикла управления;

М(т) - функция управления, М( т)ЈЕт;

N(r)- функция, характеризующая помехи на входе системы, N(r)eEn;

в - оператор отображения пространства входа Еп, Ex, Em в пространство выхода Еу.

Пусть задан критерий эффективности системы

. э эг/(т), м(г)

и множество допустимых значений функций управления . Тогда задача оптимального управления состоит в том, чтобы найти такой вектор управления moptfE ™, который обеспечил бы экс ремальное значение критерия эффективности

3(mopt) макСтеЕ т (r), M (г).

Уравнение функционирования системы и критерий эффективности совместно определяют функцию управления М(г), как неявную функцию вида

M(r) ,Y(r), Э(т).

Таким образом, задача оптимизации управления РЛ системой сводится к выбору критерия эффективности системы Э и разработке метода и алгоритма определения оптимального значения вектора управления rrioptCEm.

Устройство позв ляет выбрать опти мальное значение вектора управления m0pt при известности критерия эффективности системы Э. Критерием эффективности фун- кционирования системы является максимум суммы частных оценок решения

i fc i

Э(р) максцк.т.д 2, L L ampki х

L 1k - 1п- 1 X nmpkL (q),

где m - номер параметра для оценки каждого решения, m 1Т;

р - номер рассматриваемого решения; k - номер признака, по которому объединены гл-е параметры,

L т номер условия, в котором рассматривается решение, L 1V;

Т - количество параметров для оценок каждого решения.

Н - количество ра;сматриваемых решений;

Е - количество признаков, по которым объединены параметры;

V - количество условий, в которых рассматривается решение;

ampkL частная оценка гл-го параметра, относящегося к k-му признаку при выборе р-го решения, реализуемого в L-м условии; nmpkL параметр распределения, характеризующий q-й ггриянт оценки, q 17.

, если m-й параметр k-ro nmpki(q) J признака для L-ro условия

Л участвует в оценке р-го I решения,

, в противном случае. Частные оценки ampkL признаков решения задаются экспертным способом на основании априорных данных о системе. Параметр распределения характеризует 7 возможных вариантов реализации оценок р-го решения.

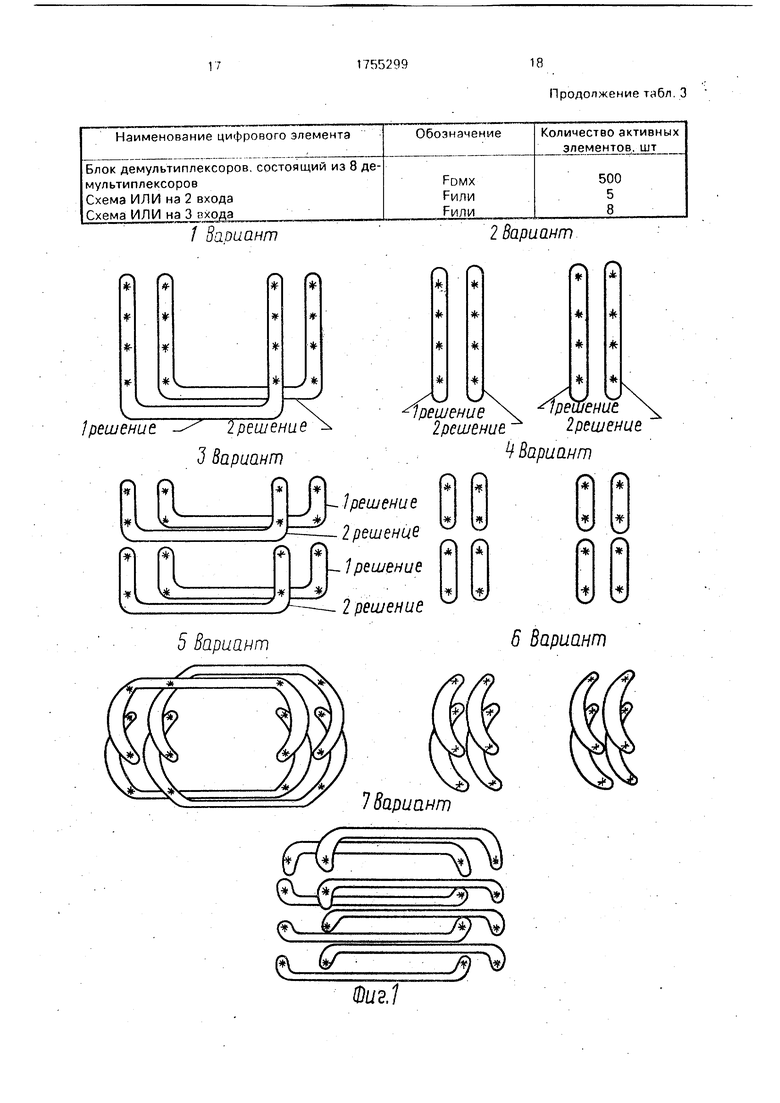

1вариант: оценка р-го решения производится по всем параметрам, по всем признакам и по всем условиям,

2варинт: оценка р-го решения производится по всем параметрам, по всем признакам, но по каждому условию отдельно.

3вариант: оценка р-го решения произ- водится по всем 1араметрам по всем условиям, но отдельно по каждому признаку.

4вариант: оценка р-го решения производится по всем параметрам, но по каждому признаку и по каждому условию отдельно.

5 варинт: оценка р-го решения производится повеем признакам, по всем условиям, но отдельно по каждому параметру

б вариант: оценка р-го решения производится по всем признакам, но по каждому параметру и по каждому условию отдельно,

7 вариант- оценка р-го решения производится по всем условиям, но по каждому параметру и по каждому признаку отдельно.

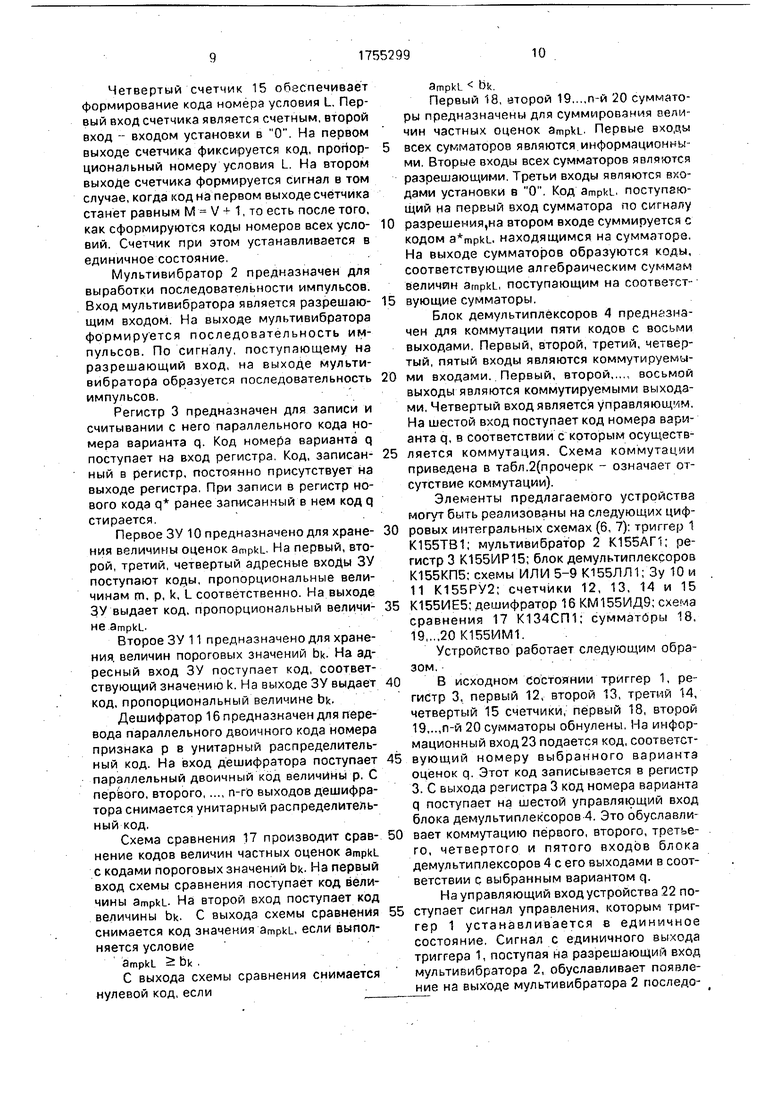

Если принять, что 1 обозначает слово по каждым, а О обозначает слово по всем, то множество вариантов оценки {q} можно проиллюстрировать трехразрядным двоичным кодом, см. табл.1.

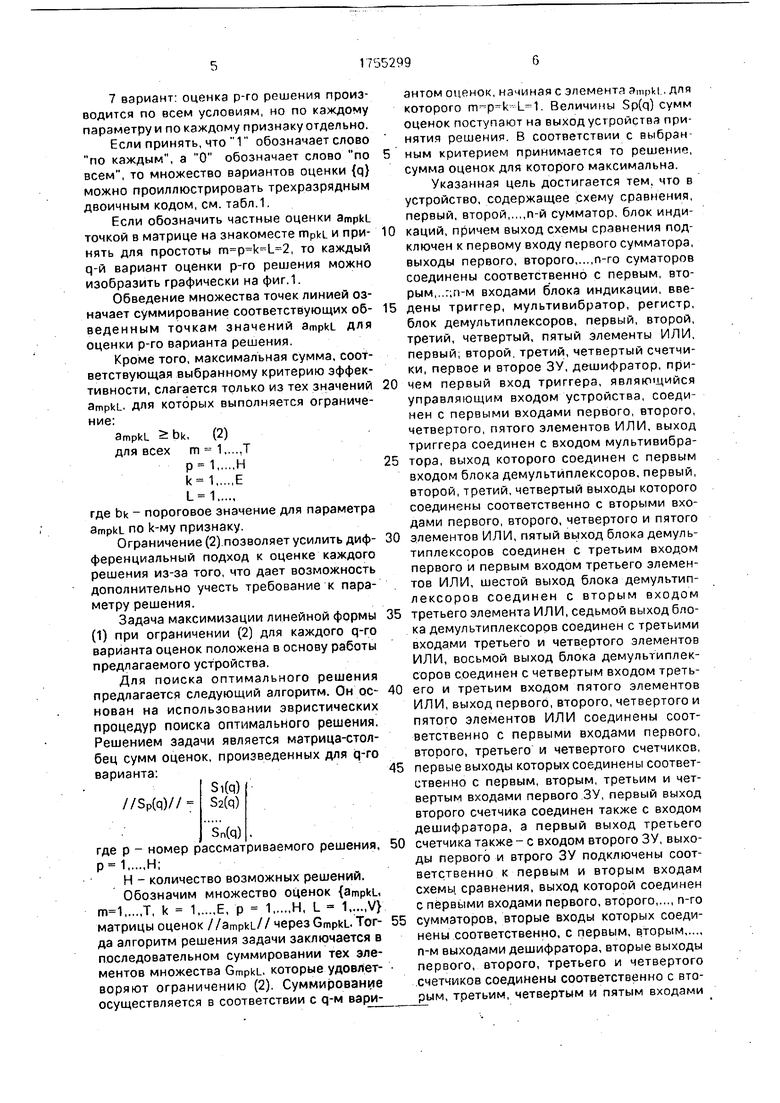

Если обозначить частные оценки ampkL точкой в матрице на знакоместе трк и при- пять для простоты , то каждый q-й вариант оценки р-го решения можно изобразить графически на фиг.1.

Обведение множества точек линией означает суммирование соответствующих об- веденным точкам значений ampkL для оценки р-го варианта решения.

Кроме того, максимальная сумма, соответствующая выбранному критерию эффективности, слагается только из тех значений ampkL. для которых выполняется ограничение:

ampkL bk, (2)

для всех m 1Т

k 1Е

где bk - пороговое значение для параметра ampkL по k-му признаку.

Ограничение (2) позволяет усилить диф- ференциальный подход к оценке каждого решения из-за того, что дает возможность дополнительно учесть требование к параметру решения.

Задача максимизации линейной формы (1) при ограничении (2) для каждого q-ro варианта оценок положена в основу работы предлагаемого устройства.

Для поиска оптимального решения предлагается следующий алгоритм. Он ос- нован на использовании эвристических процедур поиска оптимального решения. Решением задачи является матрица-столбец сумм оценок, произведенных для q-ro варианта:

Si(q)

//SP(q)//

S2(q) Sn(q)

где р - номер рассматриваемого решения,

Н - количество возможных решений.

Обозначим множество оценок {ampkLi

, k 1Е, р 1Н, L 1V}

матрицы оценок //ampkL// через Gmpkb Tor- да алгоритм решения задачи заключается в последовательном суммировании тех элементов множества GmpkL. которые удовлет- воряют ограничению (2). Суммирование осуществляется в соответствии с q-м вари-

5

0

5

0

5

0

5

0 5

0

5

антом оценок, начиная с элемента ЭтРм , для которого m-p-k-L-1. Величины Sp(q) сумм оценок поступают на выход устройства принятия решения. В соответствии с выбранным критерием принимается то решения, сумма оценок для которого максимальна.

Указанная цель достигается тем, что в устройство, содержащее схему сравнения, первый, второйn-й сумматор, блок индикаций, причем выход схемы сравнения подключен к первому входу первого сумматора,

выходы первого, второгоn-го суматоров

соединены соответственно с первым, вторым, ..:,п-м входами блока индикации, введены триггер, мультивибратор, регистр, блок демультиплексоров, первый, второй, третий, четвертый, пятый элементы ИЛИ, первый, второй, третий, четвертый счетчики, первое и второе ЗУ, дешифратор, причем первый вход триггера, являющийся управляющим входом устройства, соединен с первыми входами первого, второго, четвертого, пятого элементов ИЛИ, выход триггера соединен с входом мультивибратора, выход которого соединен с первым входом блока демультиплексоров, первый, второй, третий, четвертый выходы которого соединены соответственно с вторыми входами первого, второго, четвертого и пятого элементов ИЛИ, пятый выход блока демультиплексоров соединен с третьим входом первого и первым входом третьего элементов ИЛИ, шестой выход блока демультиплексоров соединен с вторым входом третьего элемента ИЛИ, седьмой выход блока демультиплексоров соединен с третьими входами третьего и четвертого элементов ИЛИ, восьмой выход блока демультиплексоров соединен с четвертым входом третьего и третьим входом пятого элементов ИЛИ, выход первого, второго, четвертого и пятого элементов ИЛИ соединены соответственно с первыми входами первого, второго, третьего и четвертого счетчиков, первые выходы которых соединены соответственно с первым, вторым, третьим и четвертым входами первого ЗУ, первый выход второго счетчика соединен также с входом дешифратора, а первый выход третьего счетчика также - с входом второго ЗУ, выходы первого и втрого ЗУ подключены соответственно к первым и вторым входам схемы, сравнения, выход которой соединен

с первыми входами первого, второгоп-го

сумматоров, вторые входы которых соединены соответственно, с первым, вторым,..., n-м выходами дешифратора, вторые выходы первого, второго, третьего и четвертого счетчиков соединены соответственно с вторым, третьим, четвертым и пятым входами

блока демультиплексоров, шестой вход которого соединен с выходом регистра, вход которого является информационным входом устройства, вход установки в О соеди- нем с вторыми входами первого, второго, третьего, четвертого счетчиков, третьими входами первого, второго, п-го сумматоров, выходы которых являются выходами устройства, выход третьего элемента ИЛИ соединен с вторым входом триггера.

Введение новых элементов: триггера, мультивибратора, регистра, блока демультиплексоров, пяти схем ИЛИ, четырех счетчиков, дешифратора, двух ЗУ и новых связей позволили получать несколько вариантов оценок решений по частным оценкам параметров, объединенных признаками для раз- личных условий функционирования системы.

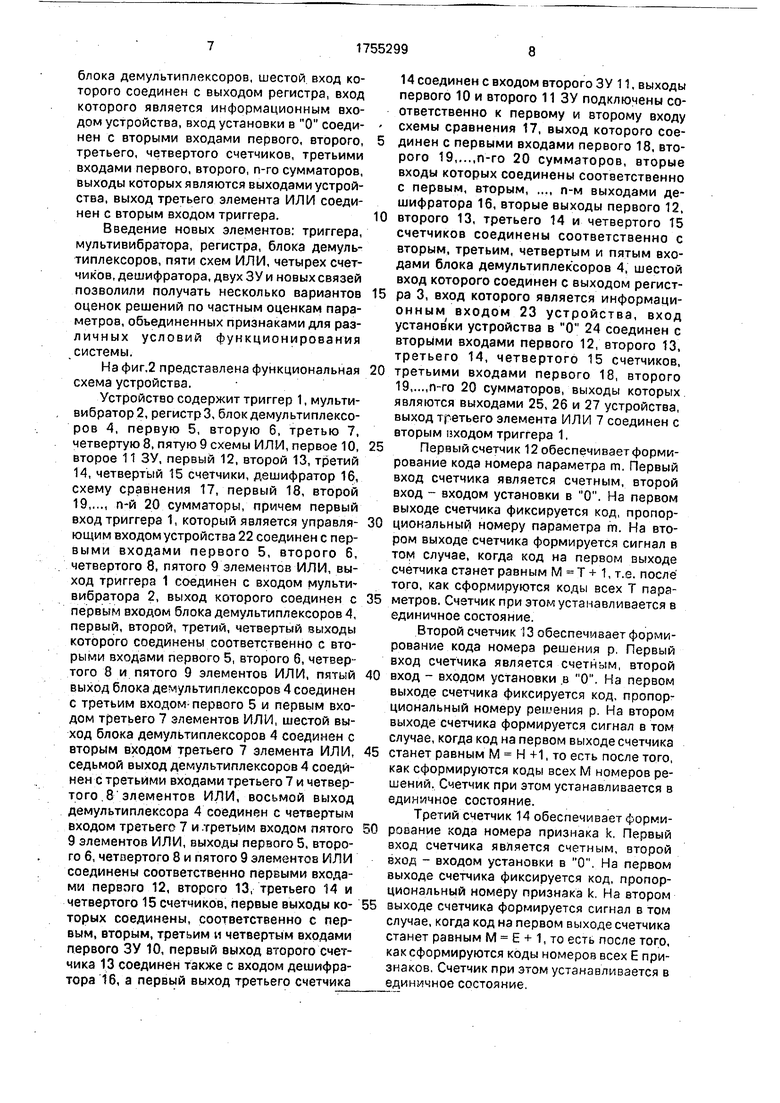

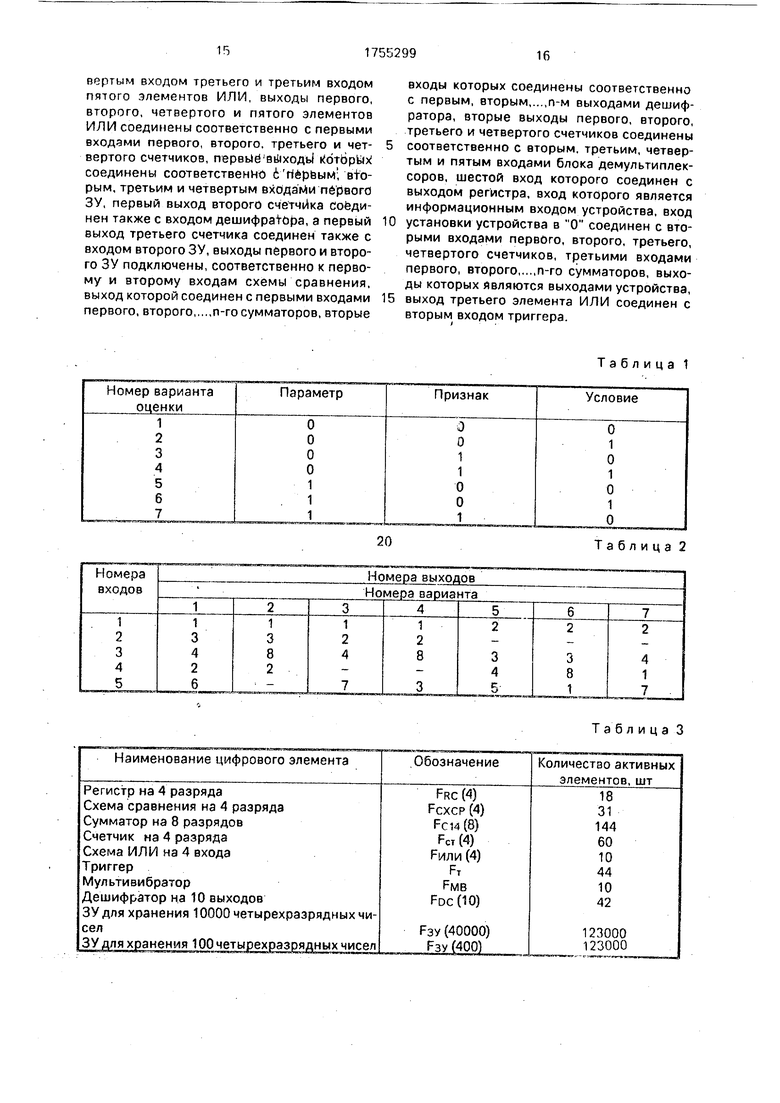

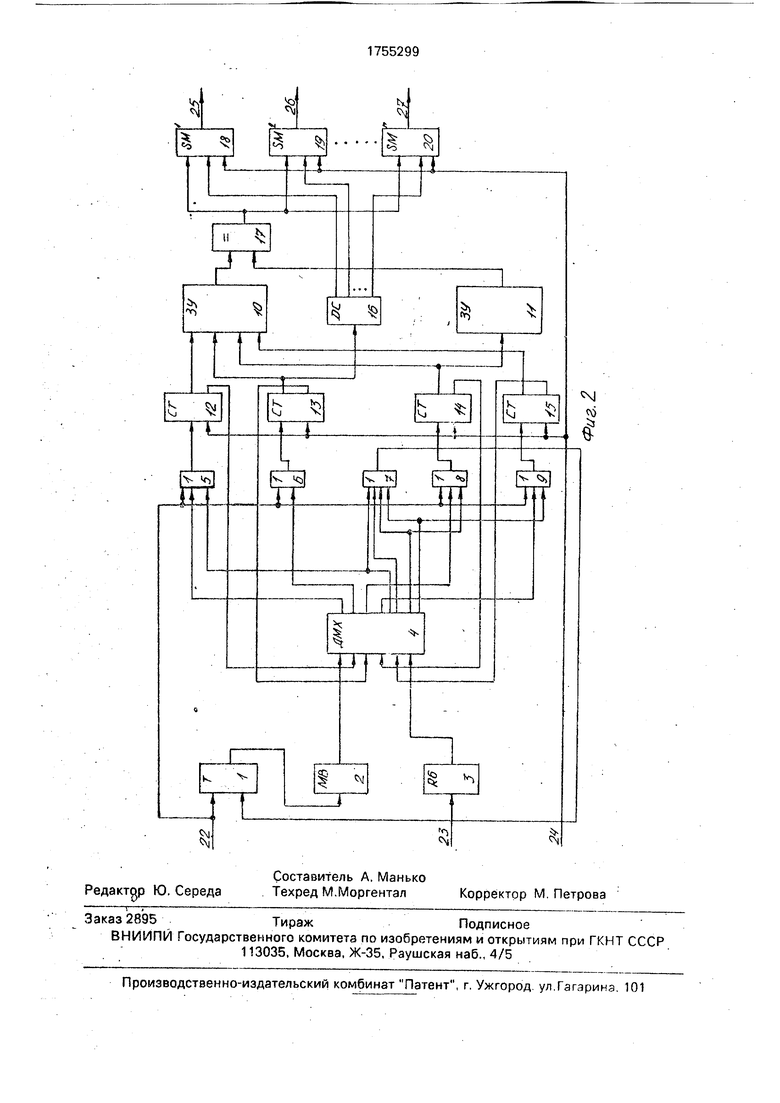

На фиг.2 представлена функциональная схема устройства.

Устройство содержит триггер 1, мультивибратор 2, регистр 3, блок демультиплексоров А, первую 5, вторую 6, третью 7, четвертую 8, пятую 9 схемы ИЛИ, первое 10, второе 11 ЗУ, первый 12, второй 13, третий 14, четвертый 15 счетчики, дешифратор 16, схему сравнения 17, первый 18, второй 19,..., п-й 20 сумматоры, причем первый вход триггера 1, который является управля- ющим входом устройства 22 соединен с пер- выми входами первого 5, второго 6, четвертого 8, пятого 9 элементов ИЛИ, выход триггера 1 соединен с входом мульти- вибратора 2, выход которого соединен с первым входом блока демультиплексоров 4, первый, второй, третий, четвертый выходы которого соединены соответственно с вторыми входами первого 5, второго б, четвертого 8 и пятого 9 элементов ИЛИ, пятый выход блока демультиплексоров 4 соединен с третьим входом первого 5 и первым входом третьего 7 элементов ИЛИ, шестой выход блока демультиплексоров 4 соединен с вторым входом третьего 7 элемента ИЛИ, седьмой выход демультиплексоров 4 соединен с третьими входами третьего 7 и четвертого 8 элементов ИЛИ, восьмой выход демультиплексора 4 соединен с четвертым входом третьего 7 и третьим входом пятого 9 элементов ИЛИ, выходы первого 5, второго 6, четвертого 8 и пятого 9 элементов ИЛИ соединены соответственно первыми входами первого 12, второго 13, третьего 14 и четвертого 15 счетчиков, первые выходы ко- торых соединены, соответственно с первым, вторым, третьим и четвертым входами первого ЗУ 10, первый выход второго счетчика 13 соединен также с входом дешифратора 16, а первый выход третьего счетчика

14 соединен с входом второго ЗУ 11, выходы первого 10 и второго 11 ЗУ подключены соответственно к первому и второму входу схемы сравнения 17, выход которого соединен с первыми входами первого 18, второго 19п-го 20 сумматоров, вторые

входы которых соединены соответственно с первым, вторым, .... n-м выходами дешифратора 16, вторые выходы первого 12, второго 13, третьего 14 и четвертого Т5 счетчиков соединены соответственно с вторым, третьим, четвертым и пятым входами блока демультиплексоров 4, шестой вход которого соединен с выходом регистра 3, вход которого является информационным входом 23 устройства, вход установки устройства в О 24 соединен с вторыми входами первого 12, второго 13, третьего 14, четвертого 15 счетчиков, третьими входами первого 18, второго 19,...,п-го 20 сумматоров, выходы которых являются выходами 25, 26 и 27 устройства, выход третьего элемента ИЛИ 7 соединен с вторым «ходом триггера 1,

Первый счетчик 12 обеспечивает формирование кода номера параметра т. Первый вход счетчика является счетным, второй вход - входом установки в О. На первом выходе счетчика фиксируется код, пропорциональный номеру параметра т. На втором выходе счетчика формируется сигнал в том случае, когда код на первом выходе счетчика станет равным М Т + 1, т.е. после того, как сформируются коды всех Т параметров. Счетчик при этом устанавливается в единичное состояние.

Второй счетчик 13 обеспечивает формирование кода номера решения р Первый вход счетчика является счетным, второй вход - входом установки в О. На первом выходе счетчика фиксируется код, пропорциональный номеру решения р. На втором выходе счетчика формируется сигнал в том случае, когда код на первом выходе счетчика станет равным М Н +1, то есть после того, как сформируются коды всех М номеров решений. Счетчик при этом устанавливается в единичное состояние.

Третий счетчик 14 обеспечивает формирование кода номера признака k. Первый вход счетчика является счетным, второй вход - входом установки в О. На первом выходе счетчика фиксируется код, пропорциональный номеру признака k На втором выходе счетчика формируется сигнал в том случае, когда код на первом выходе счетчика станет равным М Е + 1, то есть после того, как сформируются коды номеров всех Е признаков. Счетчик при этом устанавливается в единичное состояние

Четвертый счетчик 15 обеспечивает формирование кода номера условия L. Первый вход счетчика является счетным, второй вход -- входом установки в О. На первом выходе счетчика фиксируется код, пропор- циональный номеру условия L. На втором выходе счетчика формируется сигнал в том случае, когда код на первом выходе счетчика станет равным М V - 1, то есть после того, как сформируются коды номеров всех уело- вий. Счетчик при этом устанавливается в единичное состояние.

Мультивибратор 2 предназначен для выработки последовательности импульсов. Вход мультивибратора является разрешаю- щим входом. На выходе мультивибратора формируется последовательность импульсов. По сигналу, поступающему на разрешающий вход, на выходе мультивибратора образуется последовательность импульсов.

Регистр 3 предназначен для записи и считывании с него параллельного кода номера варианта q. Код номера варианта q поступает на вход регистра Код, записан- ный в регистр, постоянно присутствует на выходе регистра. При записи в регистр нового кода q ранее записанный в нем код q стирается.

Первое ЗУ 10 предназначено для хране- ния величины оценок ampkL. На первый, второй, третий, четвертый адресные входы ЗУ поступают коды, пропорциональные величинам т, р, k, L соответственно. На выходе ЗУ выдает код, пропорциональный величи- не ampkL.

Второе ЗУ 11 предназначено для хранения, величин пороговых значений bk. На адресный вход ЗУ поступает код, соответствующий значению к. На выходе ЗУ выдает код, пропорциональный величине bk.

Дешифратор 16 предназначен для перевода параллельного двоичного кода номера признака р в унитарный распределительный код. На вход дешифратора поступает параллельный двоичный код величины р. С первого, второгоп-го выходов дешифратора снимается унитарный распределительный код.

Схема сравнения 17 производит срав- нение кодов величин частных оценок ampkL с кодами пороговых значений bk. На первый вход схемы сравнения поступает код величины ampkL. На второй вход поступает код величины bk. С выхода схемы сравнения снимается код значения ampkL, если выполняется условие

ampkL 5: bk .

С выхода схемы сравнения снимается нулевой код, если

3rnpkL bk

Первый 18, второй 19...,п-й 20 сумматоры предназначены для суммирования величин частных оценок ampkL. Первые входы всех сумматоров являются информационными. Вторые входы всех сумматоров являются разрешающими. Третьи входы являются входами установки в О. Код ampkL, поступающий на первый вход сумматора по сигналу разрешения,на втором входе суммируется с кодом . находящимся на сумматоре, На выходе сумматоров образуются коды, соответствующие алгебраическим суммам величин ampkL, поступающим на соответствующие сумматоры.

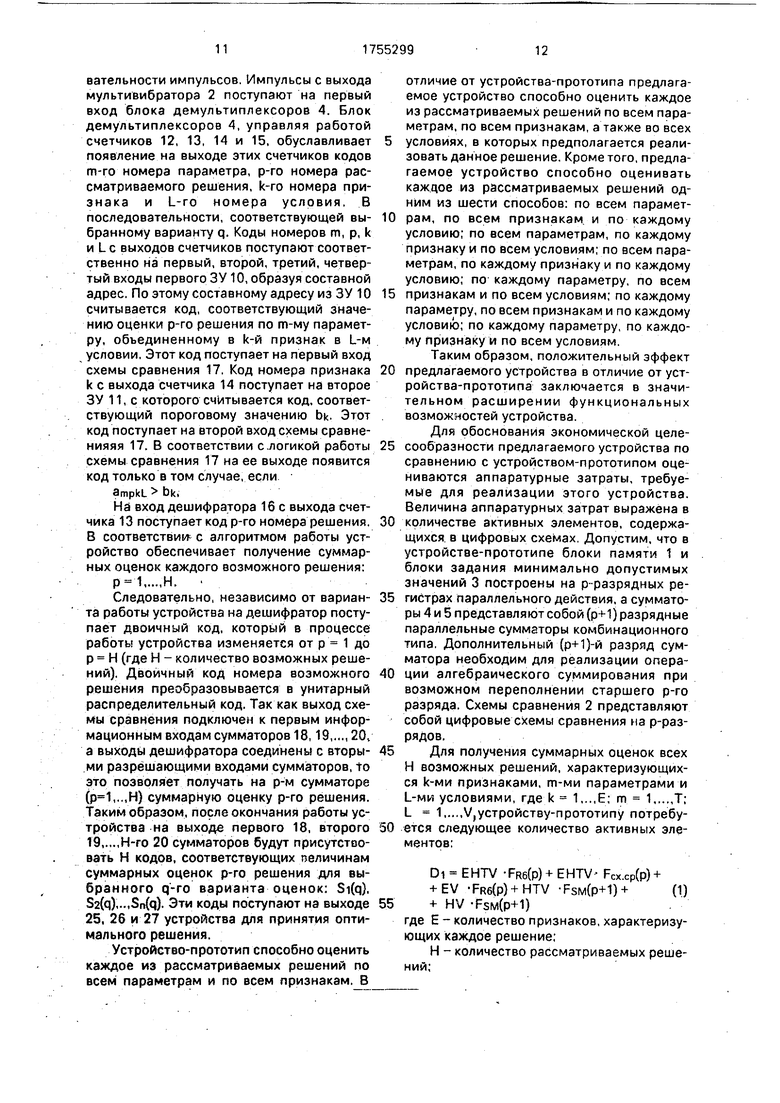

Блок демультиплексоров 4 предназначен для коммутации пяти кодов с восьми выходами. Первый, второй, третий, четвертый, пятый входы являются коммутируемыми входами. Первый, второй,.. , восьмой выходы являются коммутируемыми выходами, Четвертый вход является управляющем. На шестой вход поступает код номера варианта q, в соответствии с которым осуществляется коммутация. Схема коммутации приведена в табл.2(прочерк - означает отсутствие коммутации).

Элементы предлагаемого устройства могут быть реализованы на следующих цифровых интегральных схемах (6, 7): триггер 1 К155ТВ1; мультивибратор 2 К155АГ1; регистр 3 К155ИР15; блок демультиплексоров К155КП5; схемы ИЛИ 5-9 К155ЛЛ1; Зу 10 и 11 К155РУ2; счетчики 12, 13, 14 и 15 К155ИЕ5; дешифратор 16 Ш155ИД9; схема сравнения 17 К134СП1; сумматоры 18, 19,..,20 К155ИМ1.

Устройство работает следующим образом.

В исходном Состоянии триггер 1, регистр 3, первый 12, второй 13, третий 1А, четвертый 15 счетчики, первый 18, второй 19,..,п-й 20 сумматоры обнулены, На информационный вход 23 подается код, соответствующий номеру выбранного варианта оценок q. Этот код записывается в регистр 3. С выхода регистра 3 код номера варианта q поступает на шестой управляющий вход блока демультиплексоров 4. Это обуславливает коммутацию первого, второго, третьего, четвертого и пятого входов блока демультиплексоров 4 с его выходами в соответствии с выбранным вариантом q.

На управляющий вход устройства 22 поступает сигнал управления, которым триггер 1 устанавливается в единичное состояние. Сигнал с единичного выхода триггера 1, поступая на разрешающий вход мультивибратора 2, обуславливает появление на выходе мультивибратора 2 последовательности импульсов. Импульсы с выхода мультивибратора 2 поступают на первый вход блока демультиплексоров 4. Блок демультиплексоров 4, управляя работой счетчиков 12, 13, 14 и 15, обуславливает появление на выходе этих счетчиков кодов т-го номера параметра, р-го номера рассматриваемого решения, k-ro номера признака и L-ro номера условия. В последовательности, соответствующей выбранному варианту q. Коды номеров m, p, k и L с выходов счетчиков поступают соответственно на первый, второй, третий, четвертый входы первого ЗУ 10, образуя составной адрес. По этому составному адресу из ЗУ 10 считывается код, соответствующий значению оценки р-го решения по m-му параметру, объединенному в k-й признак в L-м условии. Этот код поступает на первый вход схемы сравнения 17, Код номера признака k с выхода счетчика 14 поступает на второе ЗУ 11, с которого считывается код, соответствующий пороговому значению bk. Этот код поступает на второй вход схемы сравне- нияяя 17. В соответствии с логикой работы схемы сравнения 17 на ее выходе появится код только в том случае, если

3mpkL bk,

На вход дешифратора 16 с выхода счетчика 13 поступает код р-го номера решения. В соответствие с алгоритмом работы устройство обеспечивает получение суммарных оценок каждого возможного решения:

р 1Н.

Следовательно, независимо от варианта работы устройства на дешифратор поступает двоичный код, который в процессе работы устройства изменяется от р 1 до р Н (где Н - количество возможных решений). Двоичный код номера возможного решения преобразовывается в унитарный распределительный код. Так как выход схемы сравнения подключен к первым информационным входам сумматоров 18, 19,..., 20 а выходы дешифратора соединены с вторыми разрешающими входами сумматоров, to это позволяет получать на р-м сумматоре (,..,Н) суммарную оценку р-го решения. Таким образом, после окончания работы устройства на выходе первого 18, второго 19Н-го 20 сумматоров будут присутствовать Н кодов, соответствующих величинам суммарных оценок р-го решения для выбранного q-ro варианта оценок: Si(q), S2(q),..,Sn(q). Эти коды поступают на выходе 25, 26 и 27 устройства для принятия оптимального решения.

Устройство-прототип способно оценить каждое из рассматриваемых решений по всем параметрам и по всем признакам. В

отличие от устройства-прототипа предлагаемое устройство способно оценить каждое из рассматриваемых решений по всем параметрам, по всем признакам, а также во всех

условиях, в которых предполагается реализовать данное решение. Кроме того, предлагаемое устройство способно оценивать каждое из рассматриваемых решений одним из шести способов: по всем параметрам, по всем признакам и по каждому условию; по всем параметрам, по каждому признаку и по всем условиям; по всем параметрам, по каждому признаку и по каждому условию; по каждому параметру, по всем

признакам и по всем условиям; по каждому параметру, по всем признакам и по каждому условию; по каждому параметру, по каждому признаку и по всем условиям.

Таким образом, положительный эффект

предлагаемого устройства в отличие от устройства-прототипа заключается в значительном расширении функциональных возможностей устройства.

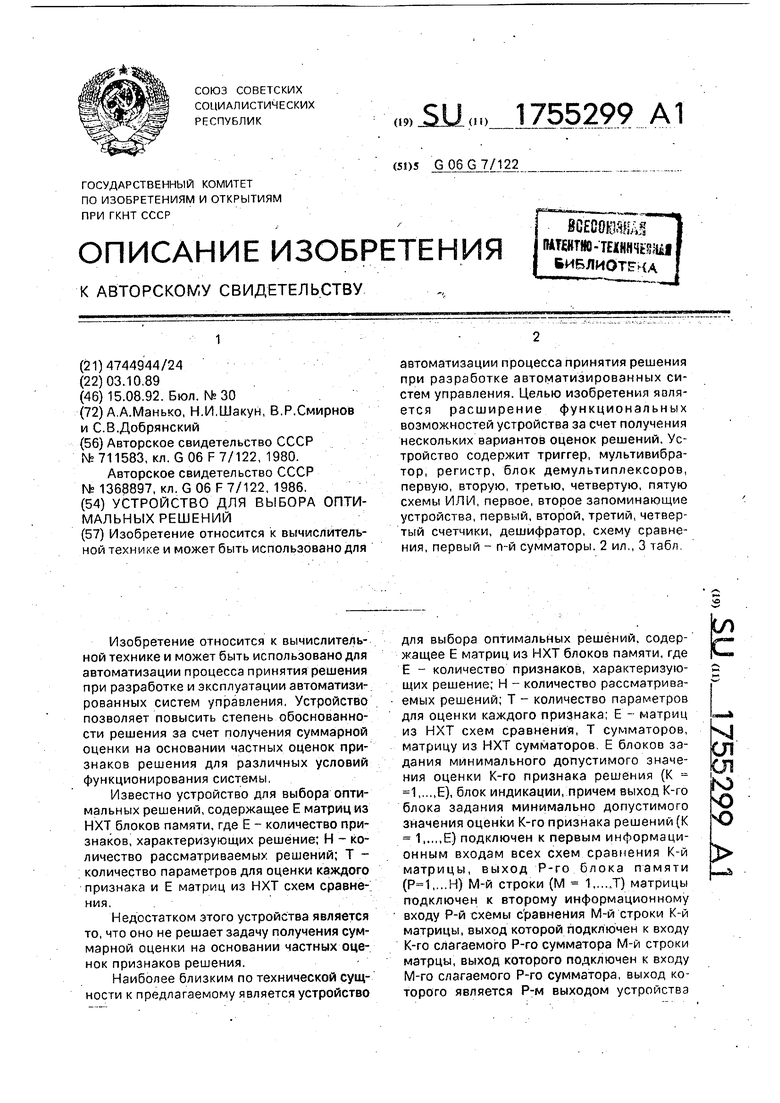

Для обоснования экономической целесообразности предлагаемого устройства по сравнению с устройством-прототипом оцениваются аппаратурные затраты, требуемые для реализации этого устройства. Величина аппаратурных затрат выражена в

количестве активных элементов, содержащихся в цифровых схемах. Допустим, что в устройстве-прототипе блоки памяти 1 и блоки задания минимально допустимых значений 3 построены на р-разрядных регистрах параллельного действия, а сумматоры 4 и 5 представляют собой (р+1) разрядные параллельные сумматоры комбинационного типа. Дополнительный (р+1)-й разряд сумматора необходим для реализации операции алгебраического суммирования при возможном переполнении старшего р-го разряда. Схемы сравнения 2 представляют собой цифровые схемы сравнения на р-раз- рядов.

Для получения суммарных оценок всех Н возможных решений, характеризующихся k-ми признаками, m-ми параметрами и

L-ми условиями, где k 1....Е; m 1Т;

L 1V, устройству-прототипу потребуется следующее количество активных элементов;

Di EHTV -FR6(p) + EHTV- Fcx.cp(p) + + EV -FR6(p} + HTV -FSM(p+1)+(1)

+ HV -FsM(p+1)

где Е - количество признаков, характеризующих каждое решение;

Н - количество рассматриваемых решений;

Т - количество параметров для оценки каждого признака;

V - количество условий, в которых рассматриваются решения;

р - разрядность цифровой схемы;

FRe(p) - количество активных элементов, необходимое для реализации р-разрядного регистра;

Fcx.cp(p) - количество активных элементов, необходимое для реализации р-разряд- ной схемы сравнения;

Fsw(p+1) - количество активных элементов, необходимое для реализации сумматора на (р-Н) разрядов.

Предлагаемому устройству для выпол- нения тех же операций потребуется следующее количество активных элементов;

D2 4FCT(p) + 5Рили(Ц + F3yi(EHTVP) + +F3Y2(EVp) + FRe(p) + FT + FMB + Foc(H) + +FoMX + FCx.cp(p) + HFsM(p+1) ,(2)

где FCT(P) - количество активных элементов, необходимое для реализации р-разрядного счетчика;-

Рили(1) - количество активных элементов, необходимое для реализации схемы ИЛИ на L входов, где L 4 для схемы ИЛИ 3, 1 2 для схемы ИЛИ 2,1 3 для схем ИЛИ 1, 4 и 5;

F3Yi(EHTVp) - количество активных элементов, необходимое для реализации ЗУ 1 для хранения EHTV - количества р-разряд- ных чисел;

Fsy2(EVp) - количество активных зле- ментов, необходимое для реализации ЗУ 2 для хранения EV-количества р-разрядных чисел;

Рвб(р) - количество активных элементов, необходимое для реализации регистра на р-разрядов;

FT- количество активных элементов, необходимое для реализации триггера;

Foc(H) - количество активных элементов, необходимое для реализации дешифра- тора на Н - выходов;

FMB - количество активных элементов, необходимое для реализации мультивибратора;

FDMX - количество активных элементов, необходимое для реализации блока демуль- типлексоров, состоящих из пяти демультиплексоров;

Fcx.cp(p) - количество активных элементов, необходимое для реализации схемы сравнения р-разрядных чисел;

Fsw(p+1) количество активных элементов, необходимое для реализации сумматора на р+1-разрядов.

0

5

0

5

0

.

5

0

5

0

5

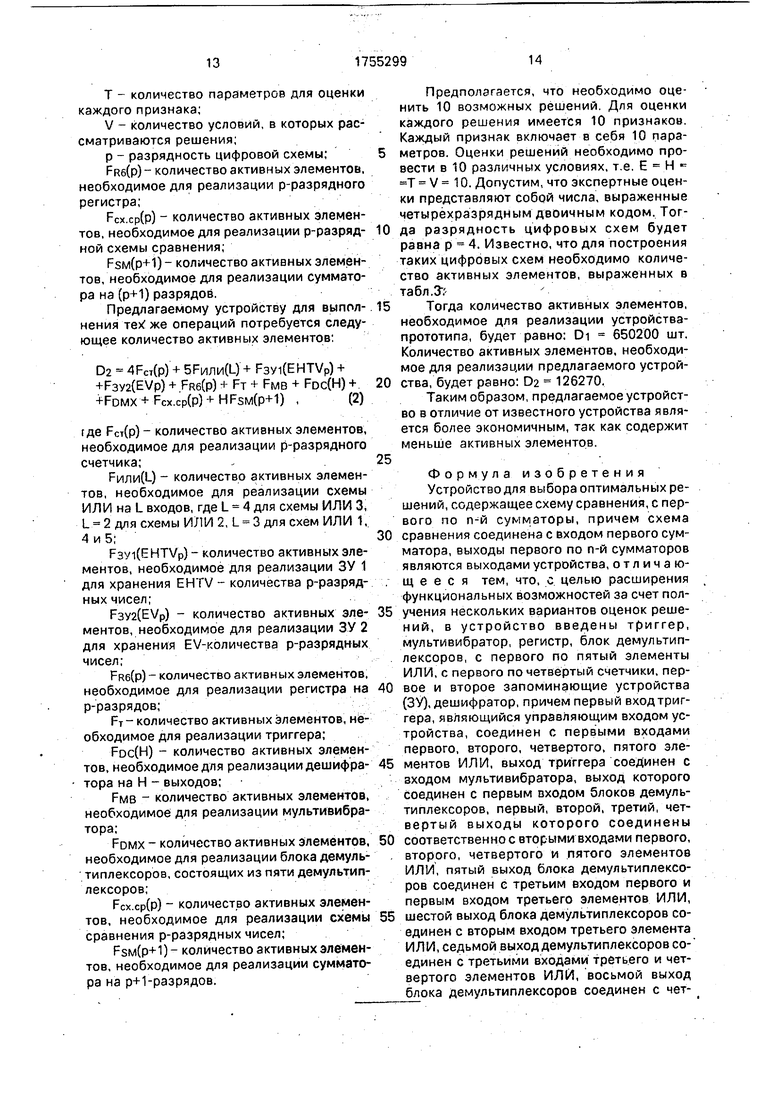

Предполагается, что необходимо оценить 10 возможных решений. Для оценки каждого решения имеется 10 признаков. Каждый признак включает в себя 10 параметров. Оценки решений необходимо провести в 10 различных условиях, т.е. Е Н « Т V 10. Допустим, что экспертные оценки представляют собой числа, выраженные четырехразрядным двоичным кодом. Тогда разрядность цифровых схем будет равна р 4. Известно, что для построения таких цифровых схем необходимо количество активных элементов, выраженных в табл.

Тогда количество активных элементов, необходимое для реализации устройства- прототипа, будет равно: DI 650200 шт. Количество активных элементов, необходимое для реализации предлагаемого устройства, будет равно: D2 126270.

Таким образом, предлагаемое устройство в отличие от известного устройства является более экономичным, так как содержит меньше активных элементов.

Формула изобретения Устройство для выбора оптимальных решений, содержащее схему сравнения, с первого по n-й сумматоры, причем схема сравнения соединена с входом первого сумматора, выходы первого по n-й сумматоров являются выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет получения нескольких вариантов оценок решений, в устройство введены триггер, мультивибратор, регистр, блок демультип- лексоров, с первого по пятый элементы ИЛИ, с первого по четвертый счетчики, первое и второе запоминающие устройства (ЗУ), дешифратор, причем первый вход триггера, являющийся управляющим входом устройства, соединен с первыми входами первого, второго, четвертого, пятого элементов ИЛИ, выход триггера соединен с входом мультивибратора, выход которого соединен с первым входом блоков демуль- типлексоров, первый, второй, третий, четвертый выходы которого соединены соответственно с вторыми входами первого, второго, четвертого и пятого элементов ИЛИ, пятый выход блока демультиплексо- ров соединен с третьим входом первого и первым входом третьего элементов ИЛИ, шестой выход блока демультиплексоров соединен с вторым входом третьего элемента ИЛ И, седьмой выход демультиплексоров со- единен с третьими входами третьего и четвертого элементов ИЛИ, восьмой выход блока демультиплексоров соединен с четвертым входом третьего и третьим входом пятого элементов ИЛИ, выходы первого, второго, четвертого и пятого элементов ИЛИ соединены соответственно с первыми входами первого, второго, третьего и четвертого счетчиков, первые -выходы1 Которых1 соединены соответственно с Первым , вторым, третьим и четвертым входами первого ЗУ, первый выход второго счетчика Соединен также с входом дешифратора, а первый выход третьего счетчика соединен также с входом второго ЗУ, выходы первого и второго ЗУ подключены, соответственно к первому и второму входам схемы сравнения, выход которой соединен с первыми входами первого, второгоn-го сумматоров, вторые

входы которых соединены соответственно с первым, вторым,...,п-м выходами дешифратора, вторые выходы первого, второго, третьего и четвертого счетчиков соединены соответственно с вторым, третьим, четвертым и пятым входами блока демультиплек- соров, шестой вход которого соединен с выходом регистра, вход которого является информационным входом устройства, вход установки устройства в О соединен с вторыми входами первого, второго, третьего, четвертого счетчиков, третьими входами первого, второгоn-го сумматоров, выходы которых являются выходами устройства, выход третьего элемента ИЛИ соединен с вторым входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Измеритель параметров качества электроэнергии трехфазной сети | 1979 |

|

SU1164616A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для обучения | 1981 |

|

SU974395A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

Изобретение относится к вычислительной технике и может быть использовано для автоматизации процесса принятия решения при разработке автоматизированных систем управления. Цепью изобретения яоля- ется расширение функциональных возможностей устройства за счет получения нескольких вариантов оценок решений. Устройство содержит триггер, мультивибратор, регистр, блок демультиплексоров, первую, вторую, третью, четвертую, пятую схемы И ПИ, первое, второе запоминающие устройства, первый, второй, третий, четвертый счетчики, дешифратор, схему сравнения, первый - n-й сумматоры. 2 ил , 3 табл

Наименование цифрового элемента

Регистр на 4 разряда Схема сравнения на 4 разряда Сумматор на 8 разрядов Счетчик на 4 разряда Схема ИЛИ на 4 входа Триггер

Мультивибратор Дешифратор на 10 выходов ЗУ для хранения 10000 четырехразрядных чиселЗУ для хранения 100 четырехразрядных чисел

Таблица 1

20

Таблица 2

Таблица 3

Обозначение

Количество активных элементов, шт

FRC (4)

FCXCP (4)

Few (8)

FCT (4)

Рил и (4)

FT

FMB Foc(10)

ay (40000) F3y (400)

18

31

144

60

10

44

10

42

123000 123000

/ Заоиант

решение - Трешени. е 3 Вариант

5

иант

(

jv

&L

fi W

Продолжение табл, 3

2 Зари ант

решение решение 2решение2решеиие

Ц Вариант

6 Вариант

7 Вариант

Фиг. 7

TJTw TQ

Jjps)

NI

I

| Устройство для выбора оптимальных решений | 1975 |

|

SU711583A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выбора оптимальных решений | 1986 |

|

SU1368897A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1989-10-03—Подача