(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Вычислительное устройство | 1987 |

|

SU1509872A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Цифровой Т-генератор функций комплексного переменного | 1987 |

|

SU1483445A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750484A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Вычислительное устройство для автоматического позиционирования транспортного средства | 1989 |

|

SU1615749A1 |

Изобретение относится к вычислительной технике и может быть использовано автономно или в составе вычислительной машины в качестве вычислителя натурального логарифма в области тейлоровских изображений (Т- . изображений). Целью изобретения является расширение функциональных возможностей путем дополнительного вычисления логарифма в Т-области. Устройство содержит п блоков деления, где п - разрядность значения функции, (п-1) блоков умножения, (п-1) вычислительных (п-2)(п-1) ячеек и Чт- матрицы. 3 ил. вычислительных ячеек

Изобретение относится к вычислительной технике и может быть использовано в различных областях народного хозяйства, где имеется потребность в специализированных вычислителях на основе тейлоровских Т-преобразований.

Известно устройство для вычисления логарифмов по авт. св. СССР № 932491. содержащее три регистра, два элемента ИЛИ, схему сравнения, сдвигающий регистр, два сумматора по модулю два, регистр, блок извлечения корня и параллельный множитель- но-делительный блок.

Недостатком известного устройства являются ограниченные функциональные возможности, так как оно не позволяет вычислить значения дискрет натурального логарифма Т-области.

Известен матричный вычислитель логарифмов по авт. св. СССР № 1012251, содержащий (п-1) сумматоров первой ступени, где п - количество операции вычисления,

первый блок элементов 2И-ИЛИ. п сумма- торов-вычитателей, (п-1) сумматоров второй ступени, п блоков элементов И первой ступени и второй блок элементов 2И-ИЛИ.

Недостатком известного вычислителя являются также ограниченные функциональные возможности в сфере определения Т-дискрет натурального логарифма. ,

Наиболее близким к изобретению является устройство для деления двоичных чисел по авт. сТа. СССР № 748410, содержащее (п-3) параллельных (п+2)-разрядных сумматора, (п- -1) управляемых и один неуправляемый (п+1)-разрядный преобразователь прямого кода в дополнительный.

Цель изобретения - расширение функциональных возможностей путем дополнительного вычисления логарифма в Т-области.

Поставленная цель достигается тем, что в устройство для вычисления функций в Т- области введены дополнительно с второго

VJ

Ч vj

СА СЛ

по n-й блоки деления (где п - разрядность значения функции), (п-1) блоков умножения, (п-1) вычислительных ячеек

.. (п-2)(п-1)

2

вычислительных ячеек

матрицы, причем каждая вычислительная ячейка содержит первый и второй умножители и вычитатель, входы вычитаемого и уменьшаемого которого соединены соответственно с выходами первого и второго умножителей, каждая вычислительная ячейка матрицы содержит первый и второй умножитель и вычитатель, вход вычитаемого которого соединен с выходом второго умножителя, вход множимого которого соединен с выходом первого умножителя, вход нулевой дискреты аргумента устройства соединен с входом делителя первого блока деления и входами множимого 1-х блоков умножения (I 1, 2, 3(п-1)), входы множителя которых соединены с входами 1-х коэффициентов устройства, входами множителя первого умножителя 1-й вычислительной ячейки и входами множителя второго умножителя (k,l)-x ячеек матрицы (к I, 1+1п-1), выходы 1-х блоков умножения соединены с входами делителя (i+1)-x блоков деления, вход первой дискреты аргумента соединен с входом делимого первого блока деления, выход вычитателя первой вычислительной ячейки соединен с входом делимого второго блока деления, вход 1-й дискреты аргумента соединен с входом множимого второго умножителя вычислительной ячейки и входом множимого первого умножителя (т,1)-й ячейки матрицы (т - 1, 2, 3, ..., (п-1), I т, т+1, (п-1)) выход вычитателя (1+1 )-й вычислительной ячейки соединен с входом уменьшаемого вычитателя (1,1) ячейки матрицы, выход вычитателя (i,l}-x ячеек матрицы соединен с входами делимого (i+2)-x блоков деления, выходы вычи- тателей (p,q) ячеек матрицы (р 2,3,.... (п-1),

q - р,р+1 (п-2)) соединены с входами

уменьшаемого вычитателя (p,q+1)-x ячеек матрицы, выход первого блока деления соединен с входами множителя второго умножителя 1-й вычислительной ячейки, вход множимого первого умножителя которой соединен с входом (1+1 )-й дискреты аргумен- та, выходы р-х блоков деления соединены с входами множителя первого умножителя (р-1,р}-й ячейки матрицы, выходы блоков деления соединены с выходами соответствующих дискрет функции устройства.

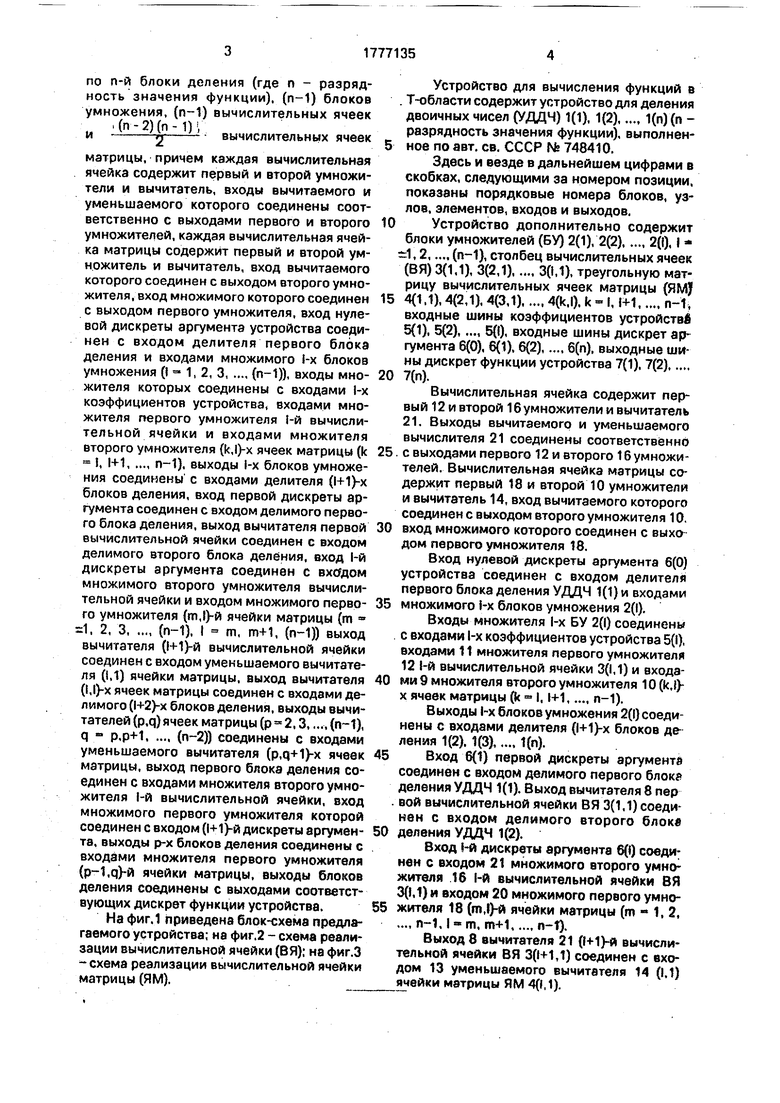

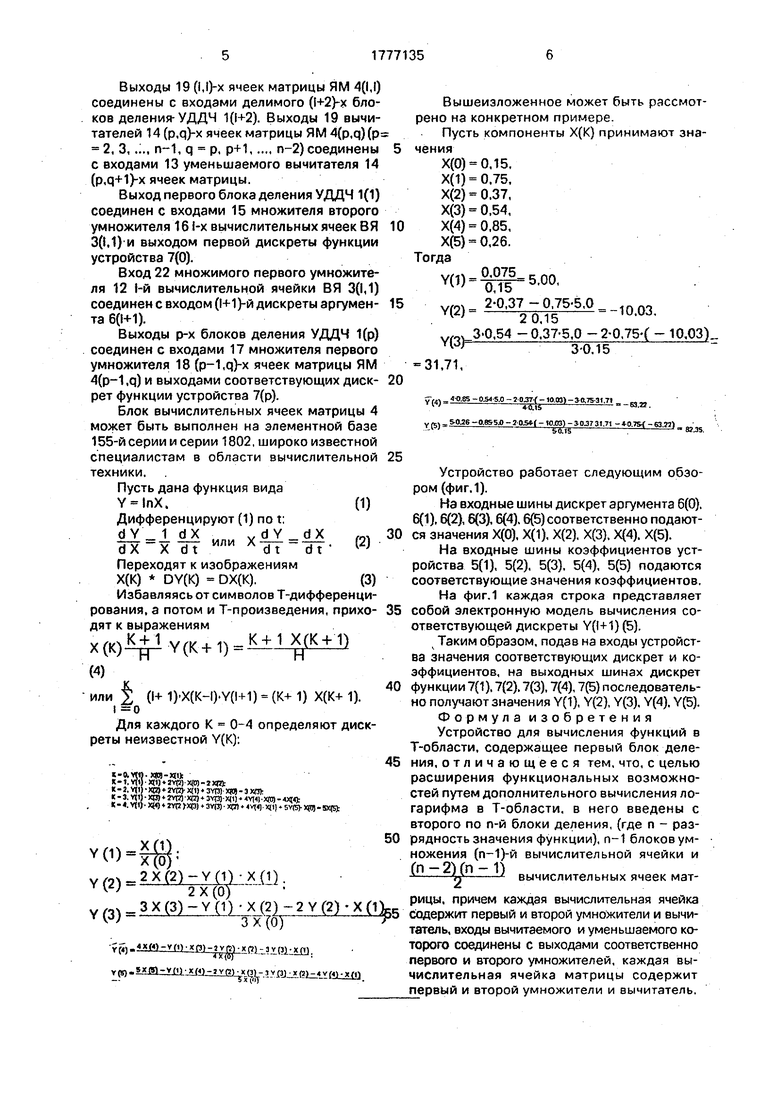

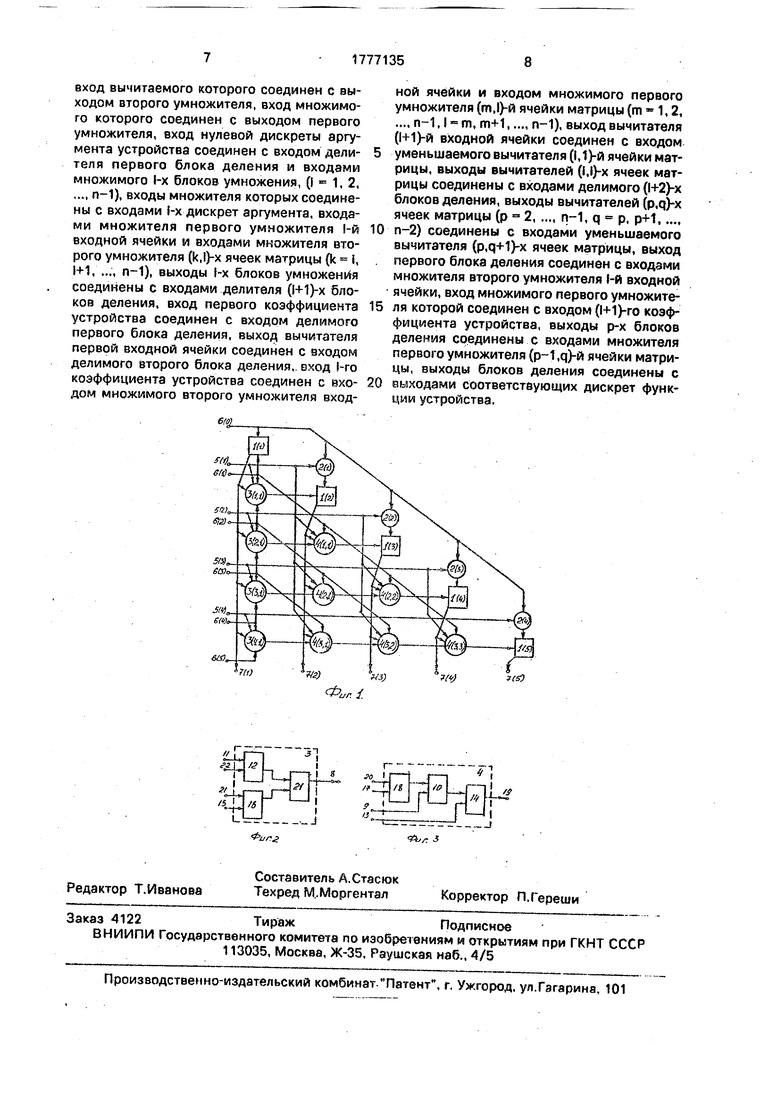

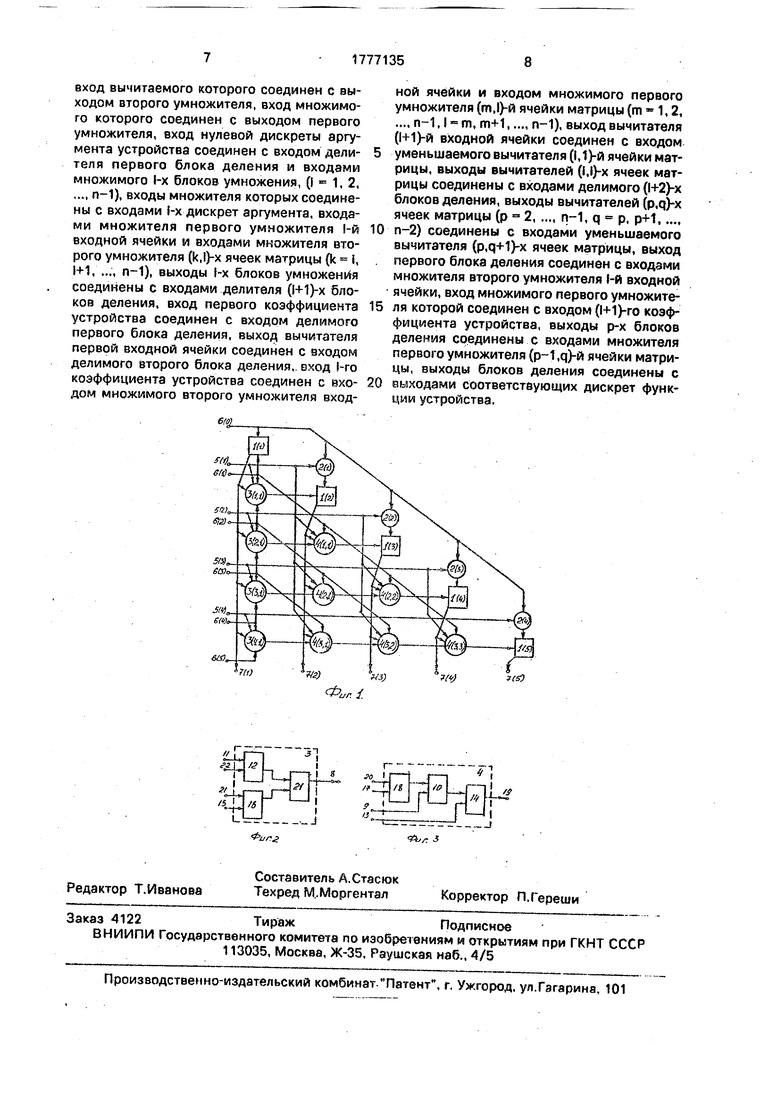

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 - схема реализации вычислительной ячейки (ВЯ); на фиг.З -схема реализации вычислительной ячейки матрицы (ЯМ).

Устройство для вычисления функций в . Т-области содержит устройство для деления

двоичных чисел (УДДЧ) 1(1), 1(2)1(п)(п разрядность значения функции), выполненное по авт. св. СССР № 748410.

Здесь и везде в дальнейшем цифрами в скобках, следующими за номером позиции, показаны порядковые номера блоков, узлов, элементов, входов и выходов.

0 Устройство дополнительно содержит

блоки умножителей (БУ) 2(1), 2(2)2(i), I ±1,2(п-1), столбец вычислительных ячеек

(ВЯ) 3(1,1), 3(2,1)30,1), треугольную матрицу вычислительных ячеек матрицы (ЯМ

5 4(1,1), 4(2,1), 4(3,1)4(k.l). k - 1,1+1n-1,

входные шины коэффициентов устройстве 5(1), 5(2),..., 5(1), входные шины дискрет аргумента 6(0), 6(1), 6(2),.... 6(п), выходные шины дискрет функции устройства 7(1), 7(2)

0 7(п).

Вычислительная ячейка содержит пер- вый 12 и второй 16 умножители и вычитатель 21. Выходы вычитаемого и уменьшаемого вычислителя 21 соединены соответственно

0 вход множимого которого соединен с выходом первого умножителя 18.

Вход нулевой дискреты аргумента 6(0) устройства соединен с входом делителя первого блока деления УДДЧ 1(1) и входами

5 множимого i-x блоков умножения 2(1).

Входы множителя 1-х БУ 2(1) соединены с входами 1-х коэффициентов устройства 5(1), входами 11 множителя первого умножителя 12 1-й вычислительной ячейки 3(1,1) и входа0 ми 9 множителя второго умножителя 10 (к,1)х ячеек матрицы (k -1,1+1п-1).

Выходы 1-х блоков умножения 2(1) соединены с входами делителя (1+1)х блоков деления 1(2). 1(3)1(п).

5 Вход 6(1) первой дискреты аргумента соединен с входом делимого первого блок деления УДДЧ 1(1). Выход вычитателя 8 пер . вой вычислительной ячейки ВЯ 3(1,1) соединен с входом делимого второго блоке

0 деления УДДЧ 1(2).

Вход 1-й дискреты аргумента 6(0 соединен с входом 21 множимого второго умножителя 16 1-й вычислительной ячейки ВЯ 3(1,1) и входом 20 множимого первого умно5 жителя 18 (т,1)-й ячейки матрицы (т - 1, 2, .... п-1,1 - т, т+1,.... п-1).

Выход8 вычитателя 21 (1+1}-й вычислительной ячейки ВЯ 3(1+1,1) соединен с входом 13 уменьшаемого вычитвтеля 14 (1,1) ячейки матрицы ЯМ 4(1,1).

Выходы 19 (U)-x ячеек матрицы ЯМ 4(1,1) соединены с входами делимого (1+2}-х блоков деления-УДДЧ 1(1+2). Выходы 19 вычи- тателей 14 (p.q)-x ячеек матрицы ЯМ 4(p,q)(p

2, 3n-1, q р. р+1п-2) соединены

с входами 13 уменьшаемого вычитателя 14 (p,q+1)-x ячеек матрицы.

Выход первого блока деления УДДЧ 1(1) соединен с входами 15 множителя второго умножителя 161-х вычислительных ячеек ВЯ 3(1,1) и выходом первой дискреты функции устройства 7(0).

Вход 22 множимого первого умножителя 12 1-й вычислительной ячейки ВЯ 3(1,1) соединен с входом ( дискреты аргумен-

та 6(1+1).

Выходы р-х блоков деления УДДЧ 1(р) соединен с входами 17 множителя первого умножителя 18 (p-1, ячеек матрицы ЯМ 4(р-1 ,q) и выходами соответствующих диск- рет функции устройства 7(р).

Блок вычислительных ячеек матрицы 4 может быть выполнен на элементной базе 155-й серии и серии 1802, широкоизвестной специалистам в области вычислительной техники.

Пусть дана функция вида

Y lnX.(1)

Дифференцируют (1) по t;

d Y dX

JL X

dX dt

или X

d Y dt

dX dt

(2)

Переходят к изображениям X(K) DY(K) - DX(K).(3)

Избавляясь от символов Т-дифференци- рования, а потом и Т-произведения, приходят к выражениям

)

(4)

или i (l+ 1)-X(K-I).Y(I+1) (К+ 1) Х(К+ 1).

Для каждого К 0-4 определяют дискреты неизвестной Y(K):

i-fcvro-Wi-W)

K-1.VM X(1)ZYp)x(0)-Zxra:

к - г, УЦ) хи svp)-x(i)«3YO) хд - э xrn«-3.Yl1j-Xp)ZYra Xt2)+3vpj X|1)) Х(0)-ДХ): K-«.YTO XW Y(2№)3Y(3) Х( )-Xro-S C(5):

хт50

уО)Щ;

V т - 2 X (2) - Y (1) X (1) . (0)

у Ы 3X(3)-Y(1)-X(2)-2Y(2)-X(1W

Ywзх(о)

YM.«i)-vo)..)iPb piixfli.

Y (S) « ) Ґ 0) X () -1 Y (2) X (3) - 3 ))t pl ±VЙХОЦЦ

Вышеизложенное может быть рассмотрено на конкретном примере.

Пусть компоненты Х(К) принимают значения

Х(0) 0,15,

Х(1) 0.75,

Х(2) - 0.37,

Х(3) 0,54,

Х(4) 0,85,

Х(5) 0,26. Тогда

Y(1).00,

Y(2)2:°-372-Qf-5-0 -10.03.

.54 -0.37-5.0 -2-0.75-( - 10,03) Y(Jj g jg-31,71,

у,-085-ОД450-гоЛ7 -1003)-Я.753Т71 д ag

у д.-5-0.26-О855Д-г|115«-{-НШ)-Яи73171 - -07Sf-63ЭТ) „ t &ОЛ582,35

25

30

35

40

45

50

Устройство работает следующим обзором (фиг.1).

На входные шины дискрет аргумента 6(0), 6(1), 6(2), 6(3), 6(4). 6(5) соответствен но подаются значения Х(0), Х(1), Х(2), Х(3), Х(4). Х(5).

На входные шины коэффициентов устройства 5(1), 5(2), 5(3), 5(4), 5(5) подаются соответствующие значения коэффициентов.

На фиг.1 каждая строка представляет собой электронную модель вычисления соответствующей дискреты Y(l+1)(5).

Таким образом, подав на входы устройства значения соответствующих дискрет и коэффициентов, на выходных шинах дискрет функции 7(1), 7(2). 7(3), 7(4), 7(5) последовательно получают значения Y(1), Y(2). Y(3). Y(4). Y(5).

Формула изобретения

Устройство для вычисления функций в Т-области, содержащее первый блок деления, отличающееся тем. что, с целью расширения функциональных возможностей путем дополнительного вычисления логарифма в Т-области. в него введены с второго по n-й блоки деления, (где п - разрядность значения функции), п-1 блоков умножения (п-1)-й вычислительной ячейки и (п-2) (п-1)

2

вычислительных ячеек матрицы, причем каждая вычислительная ячейка содержит первый и второй умножители и вычи- татель, входы вычитаемого и уменьшаемого которого соединены с выходами соответственно первого и второго умножителей, каждая вычислительная ячейка матрицы содержит первый и второй умножители и вычитатель,

вход вычитаемого которого соединен с выходом второго умножителя, вход множимого которого соединен с выходом первого умножителя, вход нулевой дискреты аргумента устройства соединен с входом делителя первого блока деления и входами множимого 1-х блоков умножения, (1 1,2, .... п-1), входы множителя которых соединены с входами 1-х дискрет аргумента, входами множителя первого умножителя 1-й входной ячейки и входами множителя второго умножителя (k,l}-x ячеек матрицы (к I,

1+1 п-1), выходы 1-х блоков умножения

соединены с входами делителя (1+1}-х блоков деления, вход первого коэффициента устройства соединен с входом делимого первого блока деления, выход вычитателя первой входной ячейки соединен с входом делимого второго блока деления, вход 1-го коэффициента устройства соединен с входом множимого второго умножителя вход&а,

7П)

ФцГЈ

Редактор Т.Иванова

Составитель А.Стасюк Техред М.Моргентал

ной ячейки и входом множимого первого умножителя (т,1)-й ячейки матрицы (т - 1,2,

.... п-1,1 - т, т+1п-1), выход вычитателя

(1+1)-й входной ячейки соединен с входом

уменьшаемого вычитателя (1,1)-й ячейки матрицы, выходы вычитателей (1,1)-х ячеек матрицы соединены с входами делимого (1+2)-х блоков деления, выходы вычитателей (p,q)-x ячеек матрицы (р 2, ..., n-1, q p, р-И,....

п-2) соединены с входами уменьшаемого вычитателя (p,q+1)-x ячеек матрицы, выход первого блока деления соединен с входами множителя второго умножителя i-й входной ячейки, вход множимого первого умножителя которой соединен с входом (1+1)-го коэффициента устройства, выходы р-х блоков деления соединены с входами множителя первого умножителя (р-1,р)-й ячейки матрицы, выходы блоков деления соединены с

выходами соответствующих дискрет функции устройства.

fbr 3

Корректор П.Гереши

| Матричный вычислитель логарифмов | 1981 |

|

SU1012251A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1990-07-09—Подача