Изобретение относится к цифровой вычислительной технике и может быть использовано при создании систем, ре- ализуюшрнх алгоритмы управления, контроля и диагностики объектов, не имеющих точной математической модели, т.е. в системах, неотъемлемым звеном которых является человек, оценивающий информацию и принимающий решение в лингвистической форме.

Целью изобретения является сокращение аппаратурных затрат процессора.

45 регистра 5, выход 46 мультиплексора 8, управляющий вход 47 мультиплексора 8, информационный вход 48 регистра 1 1 ,, выход 49 регистра 11 , син- хровход 50 регистра 11, первый и второй информационные входы 51 и 52 мультиплексора 9, выход 53 мультиплексора 9, управляющие входы 54 и 55 мультиплексоров 9 и 10, первый и второй информационные входы 56 и 57 мультиплексора 10, выход 58 мультиплексора 10, вход 59 сброса триггера 13, вход 60 установки триггера

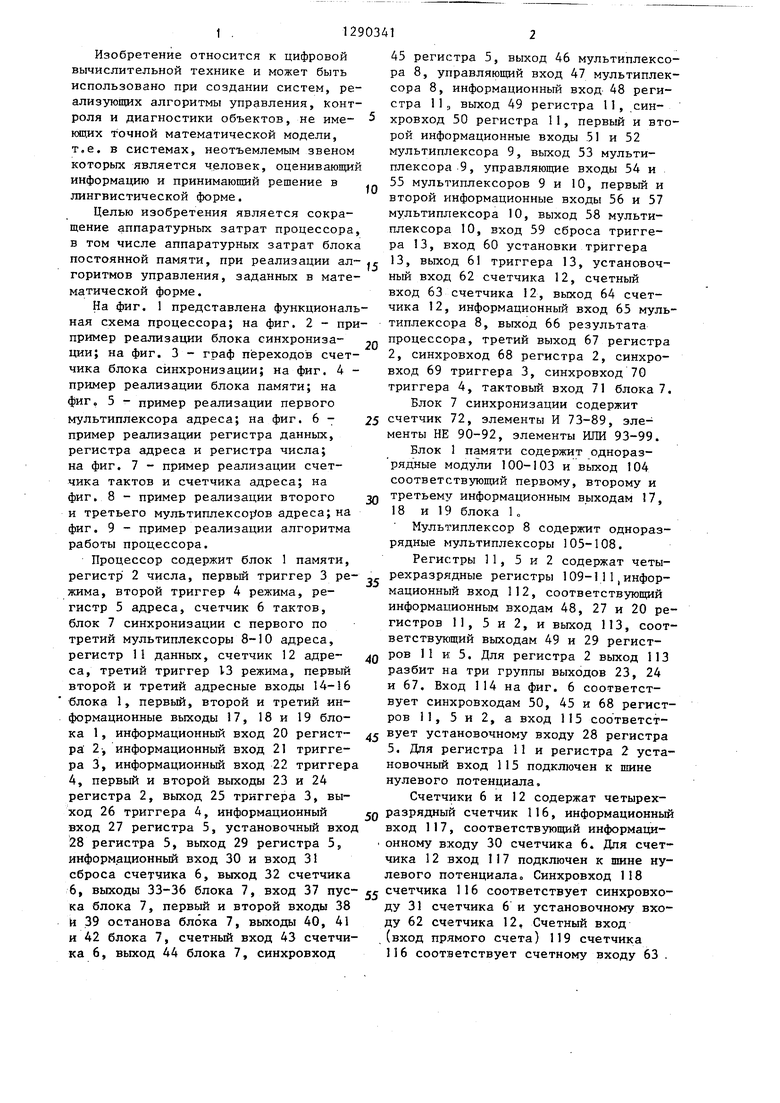

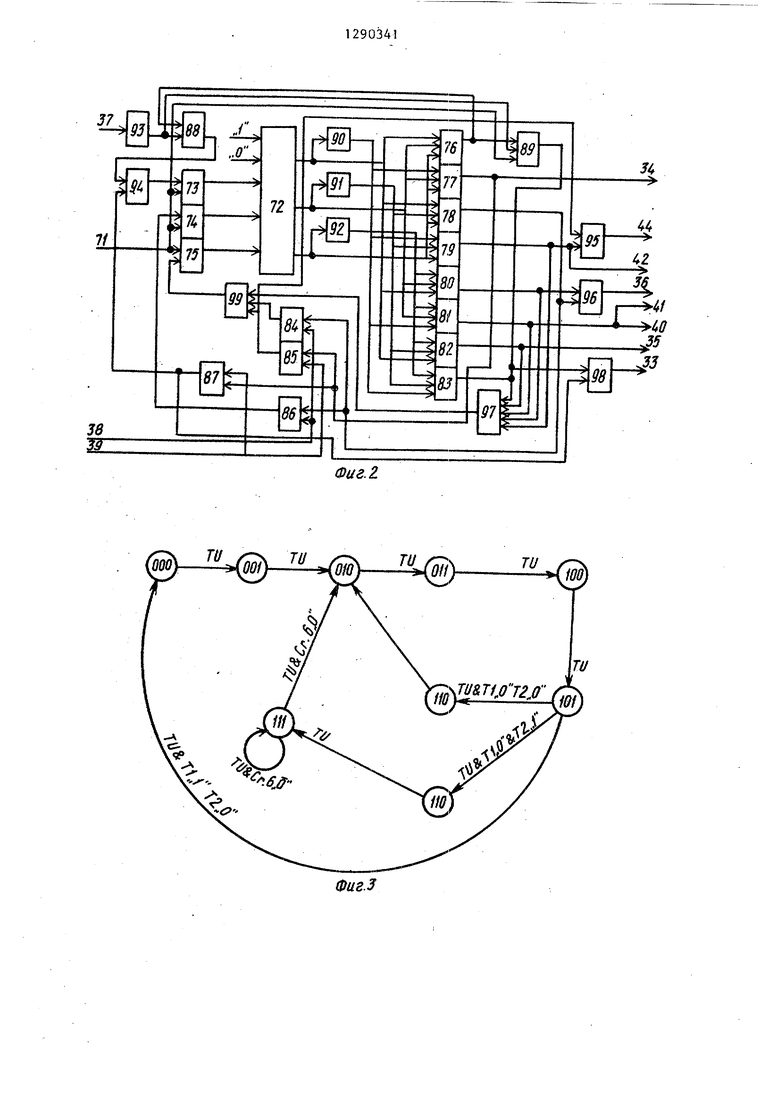

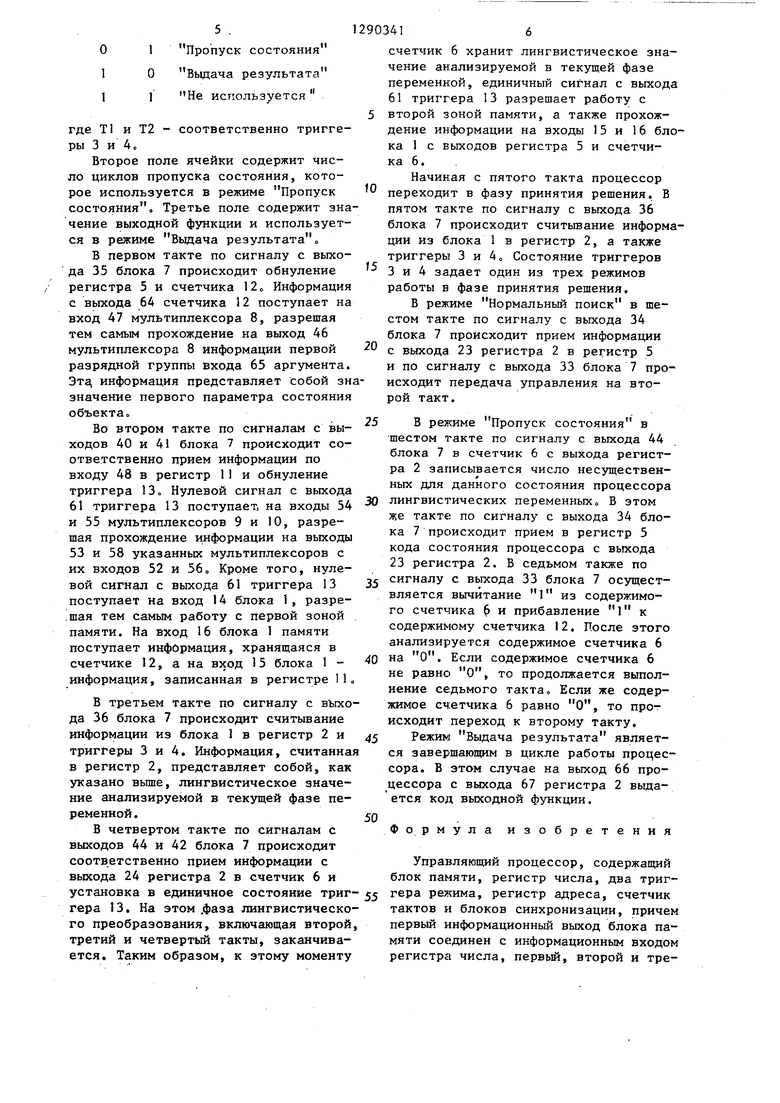

в том числе аппаратурных затрат блока постоянной памяти, при реализации ал- jc 3, выход 61 триггера 13, установоч- горитмов управления, заданных в мате- ный вход 62 счетчика 12, счетный матической форме.вход 63 счетчика 12, выход 64 счетНа фиг. 1 представлена функциональная схема процессора; на фиг. 2 - при- пример реализации блока синхрониза- л

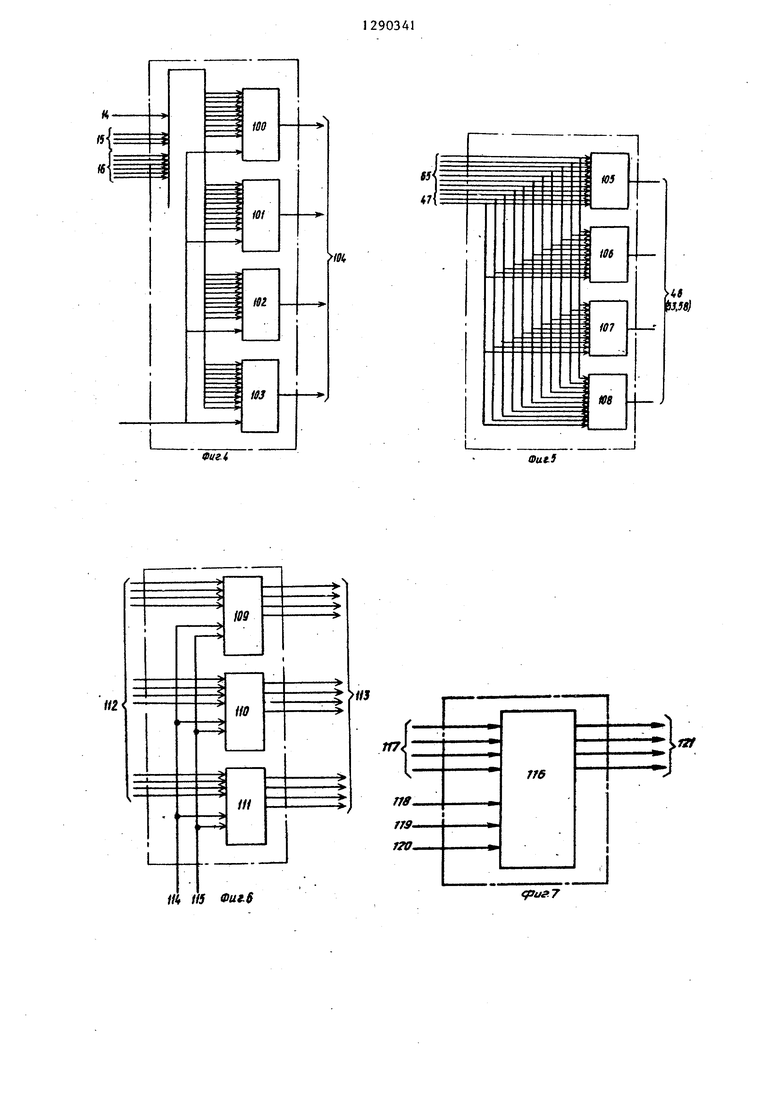

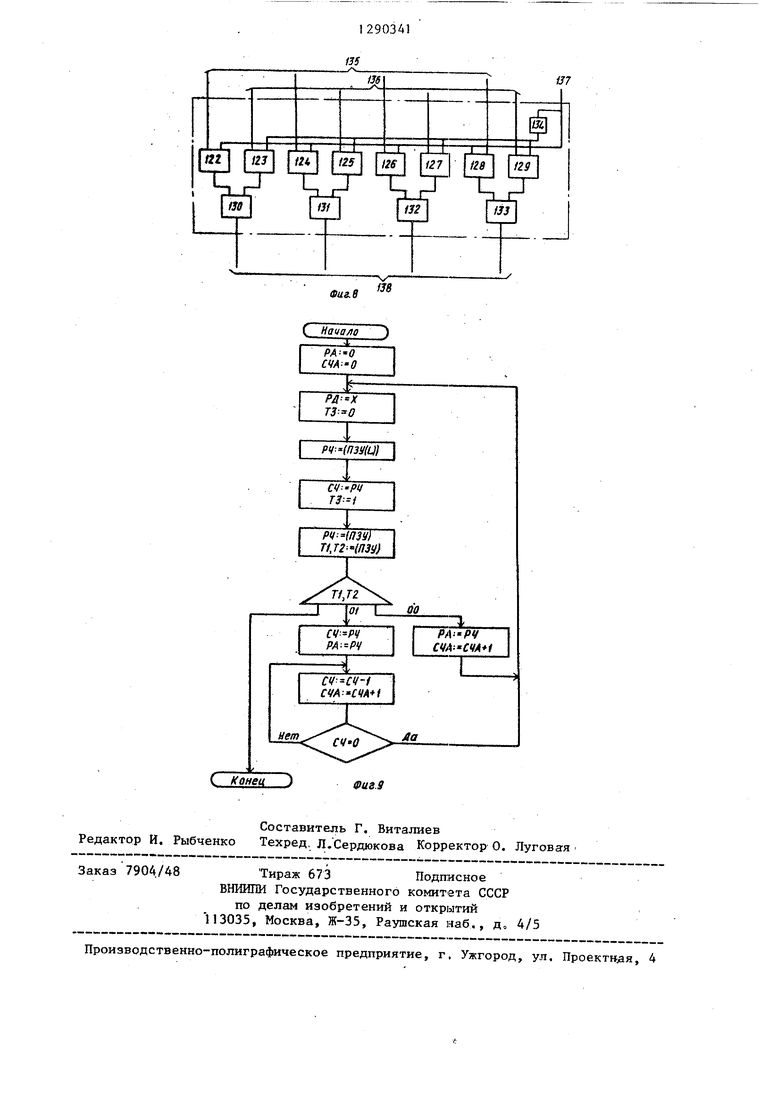

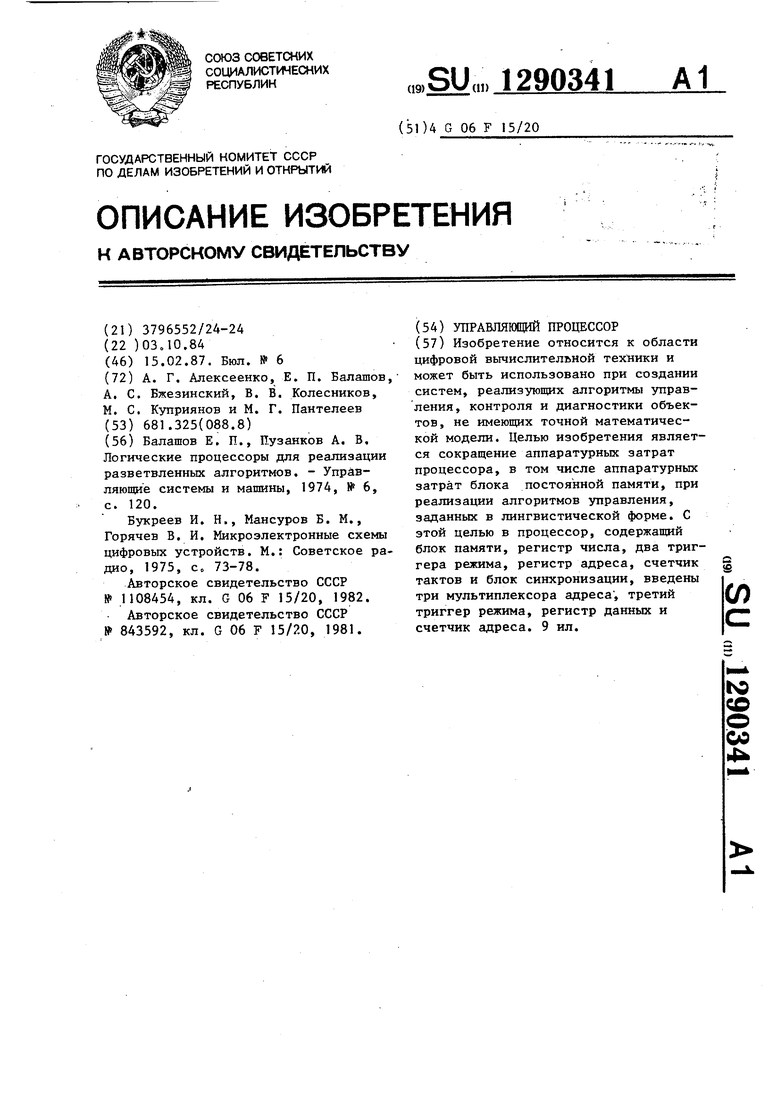

ции; на фиг. 3 - граф переходов счетчика блока синхронизации; на фиг. 4 - пример реализации блока памяти; на фиг о 5 - пример реализации первого мультиплексора адреса; на фиг. 6 - пример реализации регистра данных, регистра адреса и регистра числа; на фиг. 7 - пример реализации счетчика тактов и счетчика адреса; на фиг. 8 - пример реализации второго и третьего мультиплексор ов адреса; на фиг. 9 - пример реализации алгоритма работы процессора.

Процессор содержит блок 1 памяти.

чика 12, информационный вход 65 мультиплексора 8, выход 66 результата процессора, третий выход 67 регистра 2, синхровход 68 регистра 2, синхро- вход 69 триггера 3, синхровход 70 триггера 4, тактовый вход 71 блока 7.

Блок 7 синхронизации содержит 25 счетчик 72, элементы И 73-89, элементы НЕ 90-92, элементы ИЛИ 93-99. Блок 1 памяти содержит однораз- рядные модули 100-103 и выход 104 соответствующий первому, второму и JQ третьему информационным выходам 17, 18 и 19 блока 1„

Мультиплексор 8 содержит одноразрядные мультиплексоры 105-108.

Регистры 1, 5 и 2 содержат четырегистр 2 числа, первый триггер 3 ре- , рехразрядные регистры 109-111,информационный вход 112, соответствующий

информационным входам 48, 27 и 20 регистров 11, 5 и 2, и вьпсод 113, соответствующий выходам 49 и 29 регистров 11 и 5. Для регистра 2 выход 113 разбит на три группы выходов 23, 24 и 67. Вход 114 на фиг. 6 соответствует синхровходам 50, 45 и 68 регистров 11, 5 и 2, а вход 115 соответстжима, второй триггер 4 режима, регистр 5 адреса, счетчик 6 тактов, блок 7 синхронизации с первого по третий мультиплексоры 8-10 адреса, регистр П данных, счетчик 12 адре- д са, третий триггер 13 режима, первый второй и третий адресные входы 14-16 блока 1, первый, второй и третий информационные выходы 17, 18 и 19 блока 1, информационный вход 20 регист- 5 У установочному входу 28 регистра ра: 2-, информационный вход 21 тригге- 5. Для регистра 11 и регистра 2 уста- ра 3, информационный вход 22 триггера новочный вход 115 подключен к шине 4, первый и второй выходы 23 и 24 нулевого потенциала, регистра 2, выход 25 триггера 3, вы- Счетчики 6 и 12 содержат четырех- ход 26 триггера 4, информационный 50 Разрядный счетчик 116, информационный вход 27 регистра 5, установочный вход вход 117, соответствующий информаци- 28 регистра 5, выход 29 регистра 5, онному входу 30 счетчика 6. Для счет- информационный вход 30 и вход 31 чика 12 вход 117 подключен к шине ну- сброса счетчика 6, выход 32 счетчика левого потенциала Синхровход 118 6, выходы 33-36 блока 7, вход 37 пус- 55 счетчика 116 соответствует синхровхо- ка блока 7, первый и второй входы 38 ду 31 счетчика 6 и установочному вхо- k 39 останова блока 7, выходы 40, 41 ду 62 счетчика 12, Счетный вход и 42 блока 7, счетный вход 43 счетчи- .(вход прямого счета) 119 счетчика ка 6, выход 44 блока 7, синхровход 116 соответствует счетному входу 63 ,

45 регистра 5, выход 46 мультиплексора 8, управляющий вход 47 мультиплексора 8, информационный вход 48 регистра 1 1 ,, выход 49 регистра 11 , син- хровход 50 регистра 11, первый и второй информационные входы 51 и 52 мультиплексора 9, выход 53 мультиплексора 9, управляющие входы 54 и 55 мультиплексоров 9 и 10, первый и второй информационные входы 56 и 57 мультиплексора 10, выход 58 мультиплексора 10, вход 59 сброса триггера 13, вход 60 установки триггера

3, выход 61 триггера 13, установоч- ный вход 62 счетчика 12, счетный вход 63 счетчика 12, выход 64 счет

чика 12, информационный вход 65 мультиплексора 8, выход 66 результата процессора, третий выход 67 регистра 2, синхровход 68 регистра 2, синхро- вход 69 триггера 3, синхровход 70 триггера 4, тактовый вход 71 блока 7.

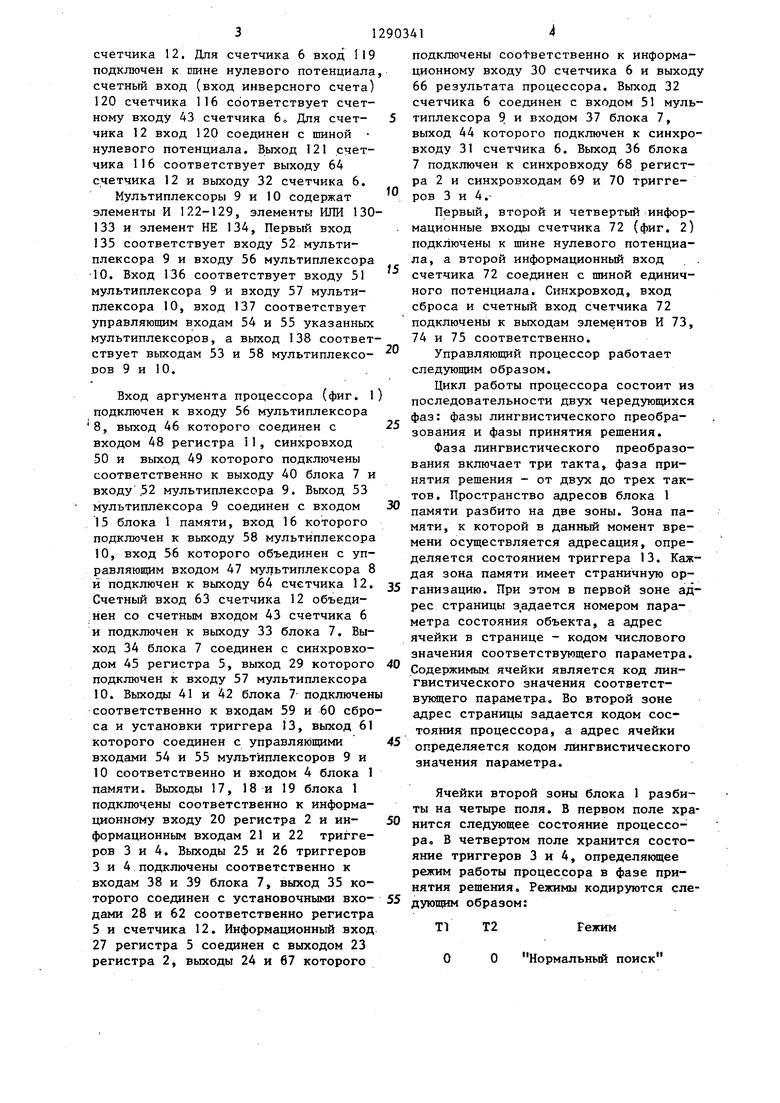

Блок 7 синхронизации содержит счетчик 72, элементы И 73-89, элементы НЕ 90-92, элементы ИЛИ 93-99. Блок 1 памяти содержит однораз- рядные модули 100-103 и выход 104 соответствующий первому, второму и третьему информационным выходам 17, 18 и 19 блока 1„

Мультиплексор 8 содержит одноразрядные мультиплексоры 105-108.

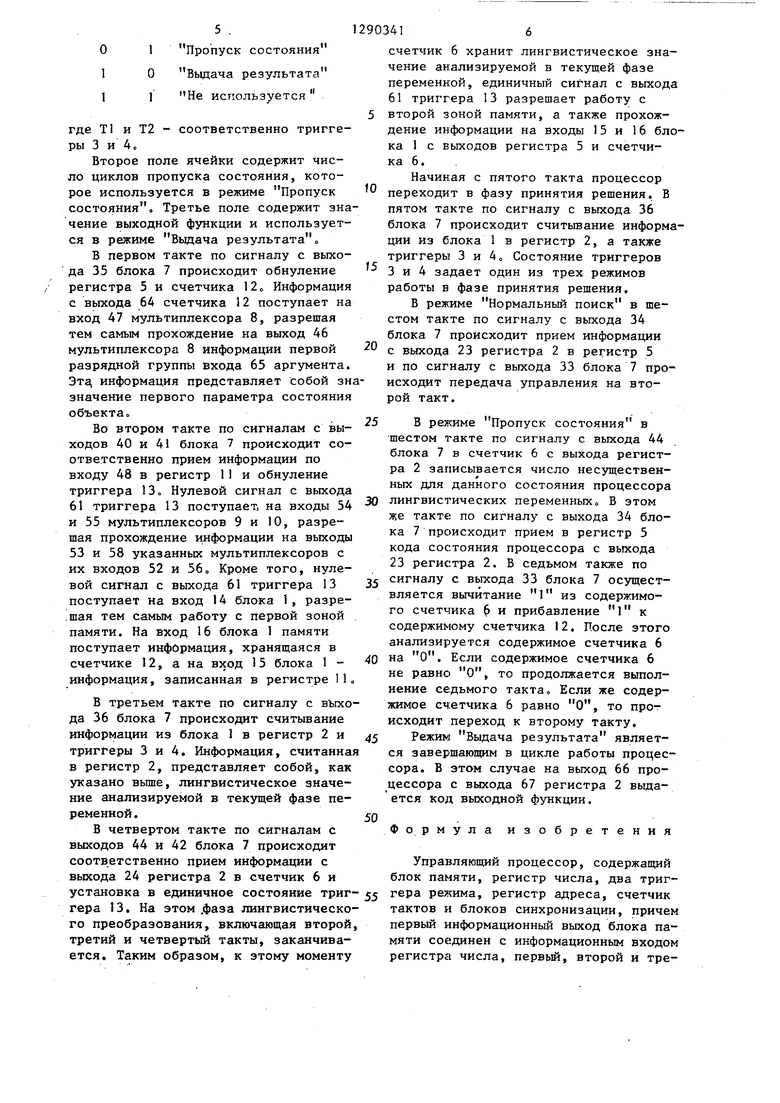

Регистры 1, 5 и 2 содержат четыинформационным входам 48, 27 и 20 регистров 11, 5 и 2, и вьпсод 113, соответствующий выходам 49 и 29 регистров 11 и 5. Для регистра 2 выход 113 разбит на три группы выходов 23, 24 и 67. Вход 114 на фиг. 6 соответствует синхровходам 50, 45 и 68 регистров 11, 5 и 2, а вход 115 соответст У установочному входу 28 регистра 5. Для регистра 11 и регистра 2 уста- новочный вход 115 подключен к шине нулевого потенциала, Счетчики 6 и 12 содержат четырех- Разрядный счетчик 116, информационный вход 117, соответствующий информаци- онному входу 30 счетчика 6. Для счет- чика 12 вход 117 подключен к шине ну- левого потенциала Синхровход 118 счетчика 116 соответствует синхровхо- ду 31 счетчика 6 и установочному вхо- ду 62 счетчика 12, Счетный вход (вход прямого счета) 119 счетчика 116 соответствует счетному входу 63 ,

счетчика 12, Для счетчика 6 вход 119 подключен к пшне нулевого потенциала счетный вход (вход инверсного счета) 120 счетчика 116 соответствует счетному входу 43 счетчика 6 о Для счетчика 12 вход 120 соединен с шиной нулевого потенциала. Выход 121 счетчика 116 соответствует выходу 64 счетчика 12 и выходу 32 счетчика 6.

Мультиплексоры 9 и 10 содержат элементы И 122-129, элементы ИЛИ 130- 133 и элемент НЕ 134, Первый вход 135 соответствует входу 52 мультиплексора 9 и входу 56 мультиплексора 10. Вход 136 соответствует входу 51 мультиплексора 9 и входу 57 мультиплексора 10, вход 137 соответствует управляюпщм входам 54 и 55 указанных мультиплексоров, а выход 138 соответствует выходам 53 и 58 мультиплексоDOB 9 и 10.

Вход аргумента процессора (фиг. 1 подключен к входу 56 мультиплексора 8, выход 46 которого соединен с входом 48 регистра 11, синхровход 50 и выход 49 которого подключены соответственно к выходу 40 блока 7 и входу 52 мультиплексора 9. Выход 53 мультиплексора 9 соединен с входом 15 блока 1 памяти, вход 16 которого подключен к выходу 58 мультиплексора 10, вход 56 которого объединен с управляющим входом 47 мультиплексора 8 и подключен к выходу 64 счетчика 12. Счетный вход 63 счетчика 12 объединен со счетным входом 43 счетчика 6 и подключен к выходу 33 блока 7. Выход 34 блока 7 соединен с синхровхо- дом 45 регистра 5, выход 29 которого подключен к входу 57 мультиплексора 10. Выходы 41 и 42 блока 7 подключены соответственно к входам 59 и 60 сброса и установки триггера 13, выход 61 которого соединен с управляющими входами 54 и 55 мультиплексоров 9 и 10 соответственно и входом 4 блока 1 памяти. Выходы 17, 18 и 19 блока 1 подключены соответственно к информационному входу 20 регистра 2 и информационным входам 21 и 22 триггеров 3 и 4. Выходы 25 и 26 триггеров 3 и 4 подключены соответственно к входам 38 и 39 блока 7, выход 35 которого соединен с установочными входами 28 и 62 соответственно регистра 5 и счетчика 12. Информационный вход 27 регистра 5 соединен с выходом 23 регистра 2, выходы 24 и 67 которого

fO

15

2903414

подключены сооФветственно к информационному входу 30 счетчика 6 и выходу 66 результата процессора. Вьгход 32 счетчика 6 соединен с входом 51 мультиплексора 9 и входом 37 блока 7, выход 44 которого подключен к синхро- входу 31 счетчика 6. Вьгход 36 блока 7 подключен к синхровходу 68 регистра 2 и синхровходам 69 и 70 триггеров 3 и 4.Первый, второй и четвертый информационные входы счетчика 72 (фиг. 2) подключены к шине нулевого потенциала, а второй информационный вход . . счетчика 72 соединен с шиной единичного потенциала. Синхровход, вход сброса и счетный вход счетчика 72 подключены к выходам элементов И 73, 74 и 75 соответственно.

Управляюш 1й процессор работает следующим образом.

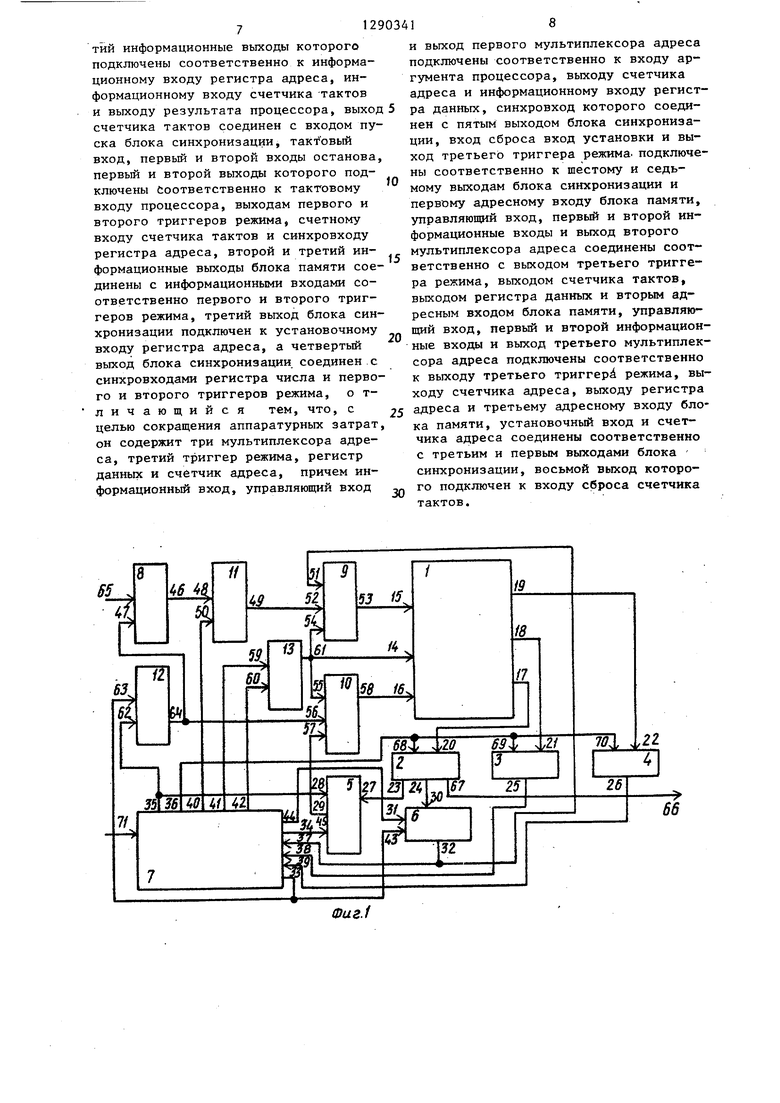

Цикл работы процессора состоит из последовательности двух чередующихся фаз: фазы лингвистического преобразования и фазы принятия решения.

Фаза лингвистического преобразования включает три такта, фаза принятия решения - от двух до трех тактов. Пространство адресов блока 1 памяти разбито на две зоны. Зона памяти, к которой в данный момент времени осуществляется адресация, определяется состоянием триггера 13. Каждая зона памяти имеет страничную организацию. При этом в первой зоне адрес страницы задается номером параметра состояния объекта, а адрес ячейки в странице - кодом числового значения соответствующего параметра. Содержимым ячейки является код лингвистического значения соответствующего параметра. Во второй зоне адрес страницы задается кодом состояния процессора, а адрес ячейки определяется кодом лингвистического значения параметра.

25

30

35

40

45

Ячейки второй зоны блока 1 разбиты на четыре поля. В первом поле хранится следующее состояние процессора, В четвертом поле хранится состояние триггеров 3 и 4, определякядее режим работы процессора в фазе принятия решения. Режимы кодируются следующим образом:

П

Т2

Режим

О

О Нормальный поиск

о 1 1

1 Пропуск состояния о Выдача результата 1 Не используется

где Т1 и Т2 - соответственно триггеры 3 и 4с

Второе поле ячейки содержит число циклов пропуска состояния, которое используется в режиме Пропуск состояния. Третье поле содержит значение выходной функции и используется в режиме Вьщача результата

В первом такте по сигналу с выхода 35 блока 7 происходит обнуление регистра 5 и счетчика 12о Информация с выхода 64 счетчика 12 поступает на вход 47 мультиплексора 8, разрешая тем самым прохождение на выход 46 мультиплексора 8 информации первой разрядной группы входа 65 аргумента. Эта, информация представляет собой зн значение первого параметра состояния объекта

Во втором такте по сигналам с выходов 40 и 41 блока 7 происходит соответственно прием информации по входу 48 в регистр 11 и обнуление триггера 13 Нулевой сигнал с выхода 61 триггера 13 поступает, на входы 34 и 55 мультиплексоров 9 и 10, разрешая прохождение информации на выходы 53 и 58 указанных мультиплексоров с их входов 52 и 56о Кроме того, нулевой сигнал с выхода 61 триггера 13 поступает на вход 14 блока 1, разре- .тая тем самым работу с первой зоной памяти. На вход 16 блока 1 памяти поступает информация, хранящаяся в счетчике 12, а на вход 15 блока 1 - информация, записанная в регистре 11

В третьем такте по сигналу с въпсо- да 36 блока 7 происходит считывание информации из блока 1 в регистр 2 и триггеры 3 и 4. Информация, считанная в регистр 2, представляет собой, как указано вьш1е, лингвистическое значение анализируемой в текущей фазе переменной .

В четвертом такте по сигналам с выходов 44 и 42 блока 7 происходит соответственно прием информации с выхода 24 регистра 2 в счетчик 6 и установка в единичное состояние триг- гера 13, На этом .фаза лингвистического преобразования, включающая второй, третий и четвертый такты, заканчивается. Таким образом, к зтому моменту

-

10

2903416

счетчик 6 хранит лингвистическое значение анализируемой в текущей фазе переменной, единичный сигнал с выхода 61 триггера 13 разрешает работу с 5 второй зоной памяти, а также прохождение информации на входы 15 и 16 блока 1 с выходов регистра 5 и счетчика 6. .

Начиная с пятого такта процессор переходит в фазу принятия решения. В пятом такте по сигналу с выхода 36 блока 7 происходит считывание информации из блока 1 в регистр 2, а также триггеры 3 и 4о Состояние триггеров 3 и 4 задает один из трех режимов работы в фазе принятия решения.

В режиме Нормальный поиск в шестом такте по сигналу с выхода 34 блока 7 происходит прием информации с выхода 23 регистра 2 в регистр 5 и по сигналу с выхода 33 блока 7 происходит передача управления на второй такт.

f5

20

В режиме Пропуск состояния в шестом гакте по сигналу с выхода 44 блока 7 в счетчик 6 с выхода регистра 2 записывается число несуществен«

ных для данного состояния процессора лингвистических переменныхо В этом же такте по сигналу с выхода 34 блока 7 происходит прием в регистр 5 кода состояния процессора с выхода 23 регистра 2, В седьмом также по сигналу с выхода 33 блока 7 осуществляется вычитание 1 из содержимого счетчика и прибавление 1 к содержимому счетчика 12, После этого анализируется содержимое счетчика 6 на О. Если содержимое счетчика 6 не равно О, то продолжается выполнение седьмого такта. Если же содержимое счетчика 6 равно О, то прот исходит переход к второму такту.

Режим Выдача результата является завершающим в цикле работы процессора, В этом случае на выход 66 процессора с выхода 67 регистра 2 выдается код выходной функции.

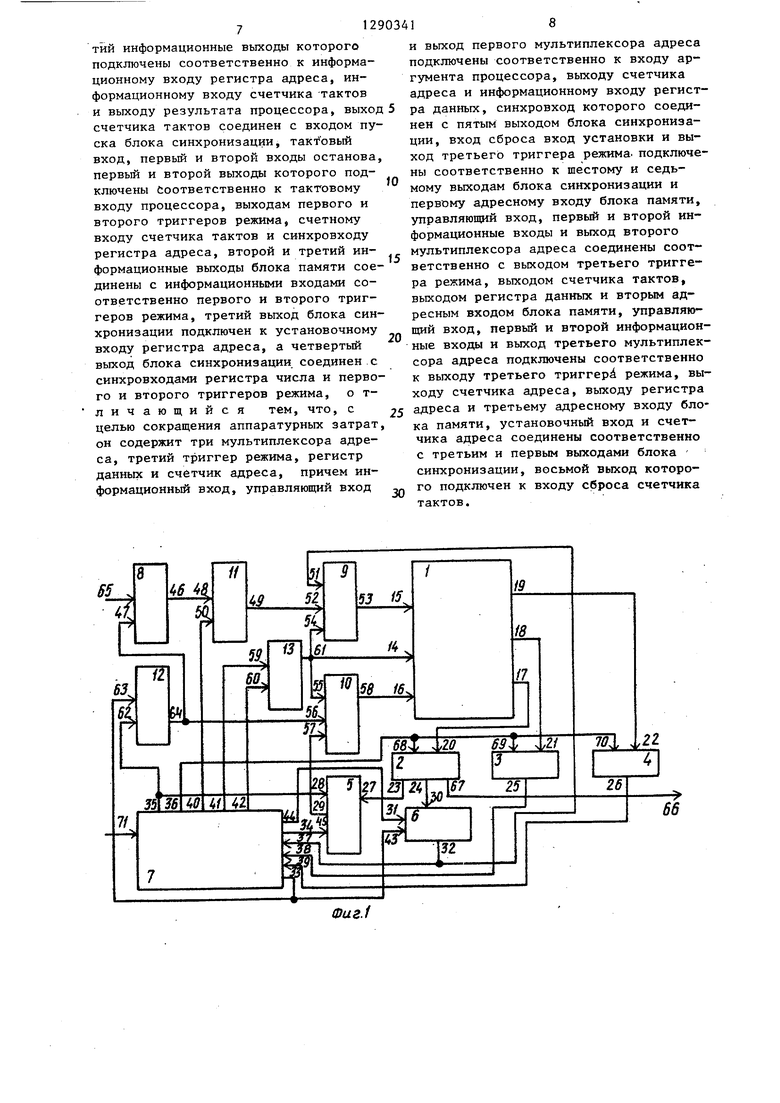

Формула изобретения

Управляющий процессор, содержащий блок памяти, регистр числа, два триггера режима, регистр адреса, счетчик тактов и блоков синхронизации, причем первый информационный выход блока памяти соединен с информационным входом регистра числа, первый, второй и тре

712

тий информационные выходы которого подключены соответственно к информационному входу регистра адреса, информационному входу счетчика тактов и выходу результата процессора, выход счетчика тактов соединен с входом пуска блока синхронизации, тактовый вход, первый и второй входы останова первый и второй выходы которого подключены Соответственно к тактовому входу процессора, выходам первого и второго триггеров режима, счетному входу счетчика тактов и синхровходу регистра адреса, второй и третий информационные выходы блока памяти соединены с информационными входами соответственно первого и второго триггеров режима, третий выход блока синхронизации подключен к установочному входу регистра адреса, а четвертый выход блока синхронизации, соединен с синхровходами регистра числа и первого и второго триггеров режима, о т- личающийся тем, что, с целью сокращения аппаратурных затрат он содержит три мультиплексора адреса, третий триггер режима, регистр данньрс и счетчик адреса, причем информационный вход, управляющий вход

8

O

5 .

5

0

и выход первого мультиплексора адреса подключены соответственно к входу аргумента процессора, выходу счетчика адреса и информационному входу регистра данных, синхровход которого соединен с пятым выходом блока синхронизации, вход сброса вход установки и выход третьего триггера режима, подключены соответственно к шестому и седьмому выходам блока синхронизации и первому адресному входу блока памяти, управляющий вход, первый и второй информационные входы и выход второго мультиплексора адреса соединены соответственно с выходом третьего триггера режима, выходом счетчика тактов, выходом регистра данных и вторым адресным входом блока памяти, управляющий вход, первый и второй информационные входы и выход третьего мультиплексора адреса подключены соответственно к выходу третьего триггер режима, выходу счетчика адреса, выходу регистра адреса и третьему адресному входу блока памяти, установочный вход и счетчика адреса соединены соответственно с третьим и первым выходами блока синхронизации, восьмой выход которого подключен к входу сброса счетчика тактов.

Фaг.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Логический процессор | 1985 |

|

SU1305704A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Лингвистический процессор для обработки диагностической информации | 1989 |

|

SU1672417A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано при создании систем, реализующих алгоритмы управления, контроля и диагностики объектов, не имеюш;их точной математической модели. Целью изобретения является сокращение аппаратурных затрат процессора, в том числе аппаратурных затрат блока постоянной памяти, при реализации алгоритмов управления, заданных в лингвистической форме. С этой целью в процессор, содержащий блок памяти, регистр числа, два триггера режима, регистр адреса, счетчик тактов и блок синхронизации, введены три мультиплексора адреса , третий триггер режима, регистр данных и счетчик адреса. 9 ил. (Л со со 4

Фиг.

Фuг.

W2

т us .f

(Out.5

«J

117

1ff

ne

ГГ9. 12O.

cpuf.7

( Hava/io ) HI

С Коней

Составитель Г, Виталиев Редактор И. Рыбченко Техред, Л. Сердюкова Корректор О. Луговая

Заказ 7904/48

Тираж 673 Подгеисное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектндя, 4

0US.S

| Балашов Е | |||

| П., Пузанков А | |||

| В | |||

| Логические процессоры для реализации разветвленных алгоритмов | |||

| - Управляюшие системы и машины, 1974, № 6, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| Букреев И | |||

| Н., Мансуров Б | |||

| М., Горячев В | |||

| И | |||

| Микроэлектронные схемы цифровых устройств | |||

| М.: Советское радио, 1975, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 843592, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1984-10-03—Подача