11

П

;j #

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля счетчиков | 1988 |

|

SU1548787A1 |

| Устройство для контроля параметров | 1989 |

|

SU1735871A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Многофункциональный модуль для устройств встроенного контроля | 1987 |

|

SU1529222A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

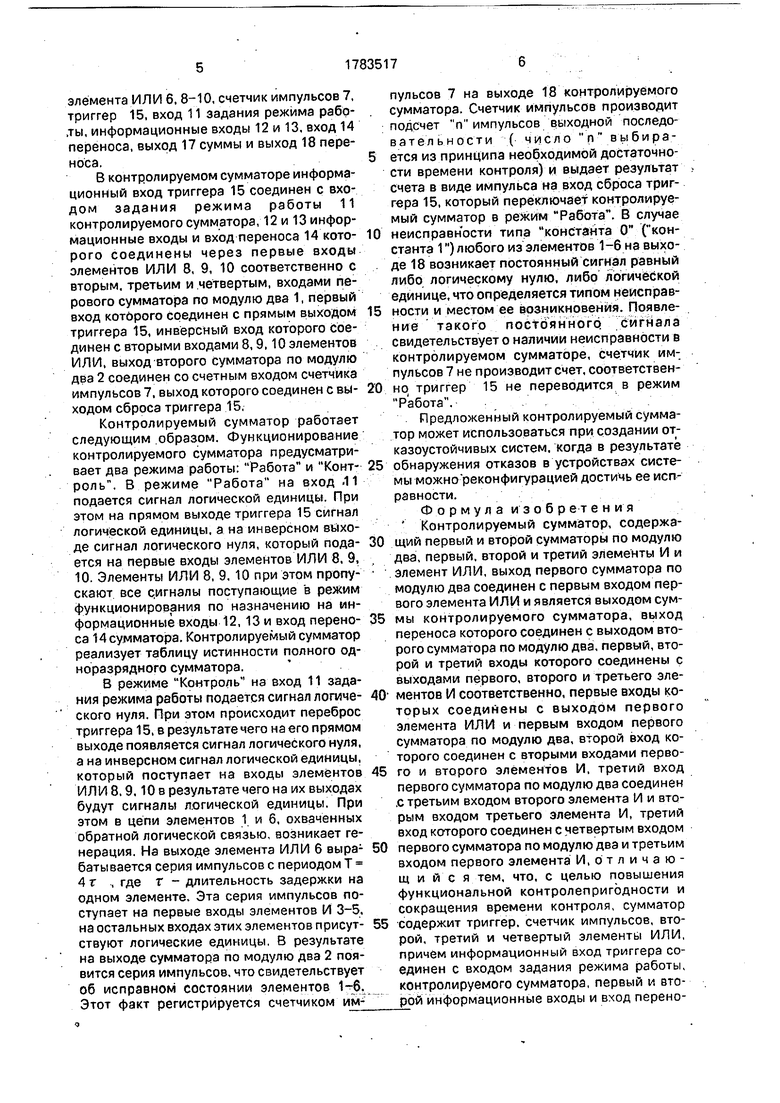

Контролируемый сумматор относится к автоматике и вычислительной технике. Целью изобретения является повышение функциональной контролепригодности и сокращение времени контроля. В устройство, содержащее два сумматора 1, 2 по модулю два, три элемента 3-5 И, элемент 6 ИЛИ, дополнительно введены триггер 15, три элемента 8-10 ИЛИ и счетчик 7 импульсов. Изо- бретение может быть использовано в устройствах, где предъявляются высокие требования к качеству функционирования, что обеспечивается оперативной их проверкой. 1 ил.

fe

XI 00

GO ел

X

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем с высокой степенью контролепригодности.

Известен сумматор, содержащий два элемента сложения по модулю два, три элемента И. Недостатком этого сумматора является необходимость исключения его из системы, в которой он функционирует, для осуществления контроля, т.е. низкая контролепригодность.

Наиболее близким к предлагаемому техническим решением является контролируемый сумматор, содержащий первый и второй сумматоры по модулю два, первый, второй и третий элементы И, элемент ИЛИ, причем выход первого сумматора по модулю два является выходом суммы контролируемого сумматора, выход переноса которого соединен с выходом второго сумматора по модулю два, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов И, первые входы которых объединены, первый вход элемента ИЛИ соединен с первым входом первого сумматора по модулю два и является входом задания режима работы контролируемого сумматора, вход переноса которого соединен с вторыми вх одами первого и второго элементов И и первого сумматора по модулю два, третий вход которого соединен с третьим входом второго элемента И, вторым входом третьего элемента И и является первым информационным входом контролируемого сумматора, второй информационный вход которого соединен с третьими входами первого и третьего элементов И и с четвертым входом первого сумматора по модулю два, пятый вход которого соединен с первым входом третьего элемента И и с выходом элемента ИЛИ, второй вход которого соединен с выходом первого сумматора по модулю два.

Недостатком этого устройства является необходимость исключения его из системы в которой он функционирует для осуществления контроля, т.е. подачи на информационные входы и вход переноса сигнала логической 1, что связано с низкой контролепригодностью. При контроле без исключения контролируемого сумматора из системы в которой он функционирует, на информационных входах и входе переноса сложно создать сигналы логической 1 поскольку система функционирует, И сигналы на этих входах постоянно меняются, а также возможны отказы других узлов системы с которыми функционирует контролируемый сумматор. При отсутствии сигналов логиче

ской 1 на информационных входах и входе переноса проверить контролируемый сумматор за очень малый промежуток времени невозможно.

Цель изобретения - повышение функциональной контролепригодности и сокращение времени контроля.

Указанная цель достигается тем, что контролируемый сумматор, содержащий

0 первый и второй сумматоры по модулю два, первый, второй и третий элементы И, элемент ИЛИ, причем выход первого сумматора по модулю два является выходом суммы контролируемого сумматора, выход перено5 са которого соединен с выходом второго сумматора по модулю два, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов И, первые входы кото0 рых объединены, первый вход элемента ИЛИ соединен с первым входом первого сумматора по модулю два и является входом задания режима работы контролируемого сумматора, вход переноса которого соеди5 нен с вторыми входами первого и второго элементов И и первого сумматора по модулю два, третий вход которого соединен с третьим входом второго элемента И вторым входом третьего элемента И и является пер0 вым информационным входом контролируемого сумматора, второй информационный вход которого соединен с третьими входами первого и третьего элементов И и с четвертым входом первого сумматора по модулю

5 два, пятый вход которого соединен с первым входом третьего элемента И и с выходом элемента ИЛИ, второй вход которого соединен с выходом первого сумматора по модулю два. содержит триггер, четвертый

0 элемент ИЛИ и счетчик импульсов, причем информационный вход триггера соединен с входом задания режима работы контролируемого сумматора, первый и второй информационные входы и вход переноса которого

5 соединены через первые входы второго, третьего и четвертого элементов ИЛИ соответственно с вторым, третьим и четвертым входами первого сумматора по модулю два, первый вход которого соединен с прямым

0 выходом триггера, инверсный выход которого соединен с вторыми входами второго, третьего и четвертого элементов ИЛИ, выход второго сумматора по модулю два соединен с счетным входом счетчика

5 импульсов, выход которого соединен с входом сброса триггера.

На чертеже представлена структурная схема контролируемого сумматора. Устройство включает два сумматора 1 и 2 по моду- два, три элемента И 3-5, четыре

элемента ИЛИ 6. 8-10, счетчик импульсов 7, триггер 15, вход 11 задания режима рабо- ,ты, информационные входы 12 и 13, вход 14 переноса, выход 17 суммы и выход 18 переноса.

В контролируемом сумматоре информационный вход триггера 15 соединен с входом задания режима работы 11 контролируемого сумматора, 12 и 13 информационные входы и вход переноса 14 которого соединены через первые входы элементов ИЛИ 8, 9, 10 соответственно с вторым, третьим и четвертым, входами перового сумматора по модулю два 1, первый вход которого соединен с прямым выходом триггера 15, инверсный вход которого соединен с вторыми входами 8,9,10 элементов ИЛИ, выход второго сумматора по модулю два 2 соединен со счетным входом счетчика импульсов 7, выход которого соединен с выходом сброса триггера 15,

Контролируемый сумматор работает следующим образом. Функционирование контролируемого сумматора предусматривает два режима работы: Работа и Контроль. В режиме Работа на вход .11 подается сигнал логической единицы. При этом на прямом выходе триггера 15 сигнал логической единицы, а на инверсном выходе сигнал логического нуля, который подается на первые входы элементов ИЛИ 8. 9, 10. Элементы ИЛИ 8, 9, 10 при этом пропускают все сигналы поступающие в режим функционирования по назначению на информационные входы 12, 13 и вход переноса 14 сумматора. Контролируемый сумматор реализует таблицу истинности полного одноразрядного сумматора.

В режиме Контроль на вход 11 задания режима работы подается сигнал логического нуля. При этом происходит переброс триггера 15, в результате чего на его прямом выходе появляется сигнал логического нуля, а на инверсном сигнал логической единицы, который поступает на входы элементов ИЛИ 8.9.10 в результате чего на их выходах будут сигналы логической единицы. При этом в цепи элементов 1 и 6, охваченных обратной логической связью, возникает генерация. На выходе элемента ИЛИ б выра1 батывается серия импульсов с периодом Т 4 т , где т - длительность задержки на одном элементе. Эта серия импульсов поступает на первые входы элементов И 3-5, на остальных входах этих элементов присутствуют логические единицы. В результате на выходе сумматора по модулю два 2 появится серия импульсов, что свидетельствует об исправном состоянии элементов 1-6. Этот факт регистрируется счетчиком импульсов 7 на выходе 18 контролируемого сумматора. Счетчик импульсов производит подсчет п импульсов выходной последо- вательности ( число гГ выбира- 5 ется из принципа необходимой достаточности времени контроля) и выдает результат счета в виде импульса на вход сброса триггера 15, который переключает контролируемый сумматор в режим Работа. В случае

0 неисправности типа константа 0 (константа 1) любого из элементов 1-6 на выходе 18 возникает постоянный сигнал равный либо логическому нулю, либо логической единице, что определяется типом неисправ5 ности и местом ее возникновения. Появление такого постоянного сигнала свидетельствует о наличии неисправности в контролируемом сумматоре, счетчик импульсов 7 не производит счет, соответствен0 но триггер 15 не переводится в режим Работа.

Предложенный контролируемый сумматор может использоваться при создании отказоустойчивых систем, когда в результате

5 обнаружения отказов в устройствах системы можно реконфигурацией достичь ее исправности.

Формула изобретения Контролируемый сумматор, содержа0 щий первый и второй сумматоры по модулю два, первый, второй и третий элементы И и элемент ИЛИ, выход первого сумматора по модулю два соединен с первым входом первого элемента ИЛИ и является выходом сум5 мы контролируемого сумматора, выход переноса которого соединен с выходом второго сумматора по модулю два, первый, второй и третий входы которого соединены с выходами первого, второго и третьего эле0- ментов И соответственно, первые входы которых соединены с выходом первого элемента ИЛИ и первым входом первого сумматора по модулю два, второй вход которого соединен с вторыми входами перво5 го и второго элементов И, третий вход первого сумматора по модулю два соединен с третьим входом второго элемента И и вторым входом третьего элемента И, третий вход которого соединен с четвертым входом

0 первого сумматора по модулю два и третьим входом первого элемента И.отличаю- щ и и с я тем, что, с целью повышения функциональной контролепригодности и сокращения времени контроля, сумматор

5 содержит триггер, счетчик импульсов, второй, третий и четвертый элементы ИЛИ, причем информационный вход триггера соединен с входом задания режима работы, контролируемого сумматора, первый и второй информационные входы и вход перено7 17835178

са которого соединены с первыми входамира, инверсный выход которого соединен с

второго, третьего и четвертого элементоввторыми входами второго, третьего и четИЛИ соответственно, выходы которых сое-вертого элементов ИЛИ, выход второго

динены с третьим, четвертым и вторым вхо-сумматора по модулю два соединен со

дами сумматора по модулю два, пятый вход5 .счетным входом счетчика импульсов, выкоторого соединен с вторым входом перво-ход которого соединен с входом сброса

го элемента ИЛИ и прямым выходом тригге-триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контролируемый сумматор | 1984 |

|

SU1242955A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Контролируемый сумматор | 1986 |

|

SU1328818A1 |

Авторы

Даты

1992-12-23—Публикация

1990-12-18—Подача