(54) ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ ВЕЛИЧИН

В КОД ФИБОНАЧЧИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь напряжение-код с коррекцией динамической погрешности | 1975 |

|

SU898609A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ - КОД | 1971 |

|

SU291225A1 |

| Преобразователь двоичного кода в код с постоянным весом | 1984 |

|

SU1229964A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

1

Изобретение относится к вычислительной технике.

Известен преобразователь аналоговых величин в код Фибоначчи,содержащий генератор импульсов, логические, элементы, резисторы, триггер 1.

Однако устройство имеет низкое быстродействие.

Известен преобразователь аналоговых величин в код Фибоначчи, содержащий двухфазный генератор тактовых импульсов, первый выход которого через последовательно, соединенные распределитель тактовых импульсов, первый блок логических элементов, регистр результата, вспомогательный регистр и второй блок логических элементов соединен с S-входом R-Sтриггера, второй выход соединен с тактовым входом вспомогательного регистра , вслход которого через последовательно соединенные преобразователь кода в напряжение и устроййтво сравнения соединен с информационным входом первого блока логических элементов 12.

Недостатком устройства является сложность и большая трудоемкость проверки линейности выходной характеристики устройства.

Цель изобретения - упрощение процесса проверки преобразователя.

Указанная цель достигается тем, что в преобразователь аналоговых величин в код Фибоначчи, содержащий двухфазный генератор тактовых импульсов, устройс во сравнения, преобразователь кода в напряжение, распределитель тактовых импульсов,

0 два блока логических элементов, регистр результата, вспомогательный регистр, R-S-триггер, введены регистр ошибки и блок вентилей, причем вход регистра ошибки через блок

5 вентилей соединен с вхсздом результата и выходом R-S-триггера.

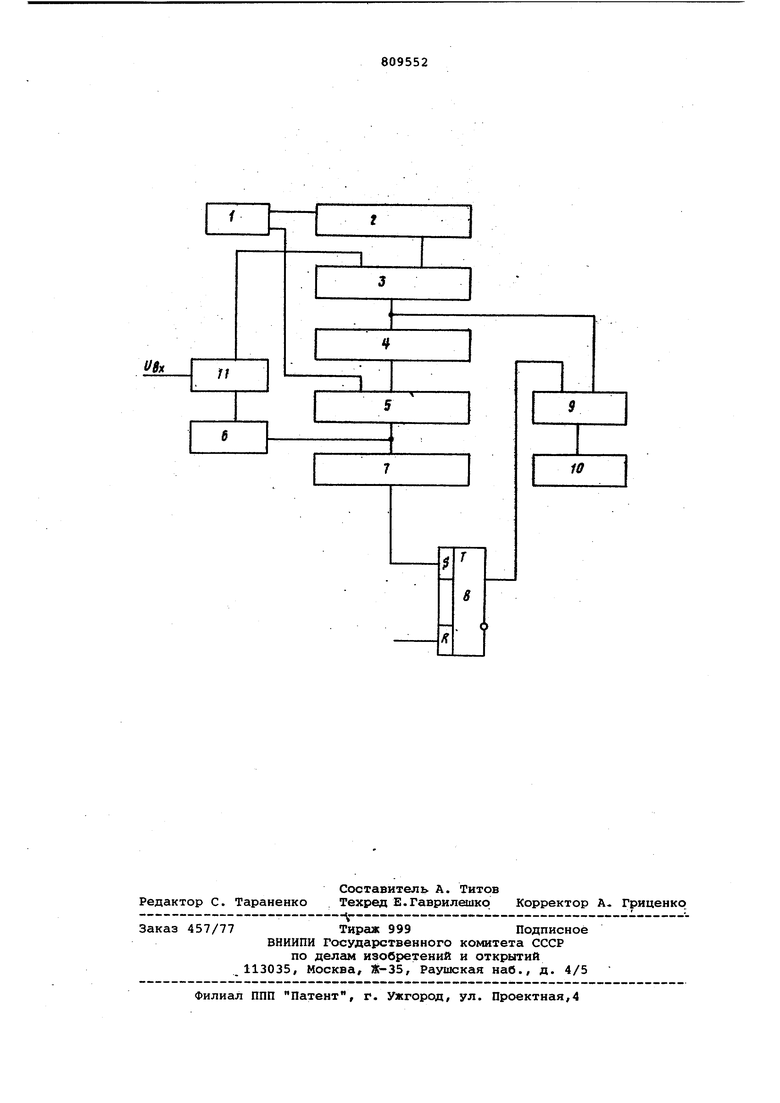

На чертеже приведена структурная электрическая схема устройства.

Устройство содержит двухфазный

0 генератор 1 тактовых импульсов, распределитель 2 тактовых импульсов, блок 3 логических элементов, регистр 4 результата, вспомогательный регистр 5, преобразователь 6 кода в

5 напряжение, блок 7 логических элементов, R-S-триггер 8, блок 9 вентилей, регистр 10 ошибки, устройство 11 сравнения.

Начало работы синхронизируется 0;фазой двухфазного генератора 1.

При поступлениизапускающего импульса Пуск синхронно с фазой двухфазного генератора 1 триггеры регистра 4 и вспомогательного регистра 5 устанавливаются в исходное состояние а R-S-триггер 8 - в нулевое состояние. На выходе преобразователя 6 ;формируется вес старшего разряда.В следующем полутакте происходит опрос устройства 11 и формирование первого продвигающего импульса в распределителе 2,

Так как входной сигнал больше сигнала с преобразователя 6, сигнал на выходе, устройства 11 отсутствует и в первый триггер регистра 4 с помощью распределителя 2 и блока 3 запшется 1. Во втором полутакте первого такта сравнения код из регистра 4 перепишется в вспомогательный регистр 5. Аналогичным образом кодируются и последующие двоичные разряды, при этом работа устройства практически повторяет функционирование классической структуры преобразователя поразрядного кодирования. Отличие заключается лишь в изменении весовых коэффициентов кодируемых разрядов преобразователя 6 и перезаписи в каждом такте содержимого регистра 4 в вспомогательный регистр 5

В случае, если за время кодирования произойдет одиночная помеха, то ее наличие будет обнаружено с помощью блока 7 по присутствии единиц в двух соседних разрядах результата и R-S-триггера 8, который изменит свое состояние-.

Но причиной появления единиц в . дву: соседних разрядах результата может послужить не только одиночная помеха, но и отклонение веса одного из разрядов преобразователя б от тре буемого значения на величину, превышающую квант, в этом случае кОди-г рование осуществляется следующим образом. При роступлении запускающег им-:ульса Пуск синхронно с фазой двухфазного генератора 1 триггеры регистра 4 и 5 устанавливаются в исходное состояние, а R-S-триггер 8 в нулевое со«;тояние. На выходе преобразователя б формируется вес старшего .разряда. В следующем полутакте происходит опрос устройства 11 и формирование .первого продвигающего имйульса в распределителе 2. Так

как входной сигнал меньше сигнала с преобразователя б, что соответствует наличию сигнала на выходе устройства 11, первый триггер регистра 4 перейдет в нулевое состояние, а в последующий триггер регистра 4 запишется 1 .

На втором и третьем тактах в регистре 4 сформируется во втором и третьем разрядах две единицы, которые переписавшись в вспомогательный регистр 5, через второй блок 7 сформируют сигнал, переводящий .R-S-триггер 8 в единичное состояние. С этого момента R-S-триггер 8 через блок 9 осуществляет подключение регистра 10 к блоку 3, в котором,начиная с третьего такта, формируется код, идентичный коду в младших разрядах. Значение кода в регистре 10 и соответствует величине погрешности старшего разряда.

Формула изобретения

Преобразователь аналоговых величи в код Фибоначчи, содержащий двухфазный генератор тактовых импульсов, первый выход которого через последовательно соединенные распределитель тактовых импульсов, первый блок логических элементов, регистр результата, вспомогательный регистр и второй блок логических элементов соединен с S-входом R-S-триггера, второй выход соединен с тактовым входом вспомогательного регистра, выход которого через последовательно соединенные преобразователь кода в напряжение и устройство сравнения соединен с информационным входом первого блока логических элементов, отличающийся тем, что, с целью .упрощения процесса проверки преобразователя, в него введены регистр ошибки и блок вентилей, причем вход регистра ошибки через блок вентилей соединен с входом регистра результата и выходом R-S-триггера.

Источники информации, принятые во внимание при экспертизе

341158, кл. Н 03 К 13/17,06.11.70.

А

8 О

К

Авторы

Даты

1981-02-28—Публикация

1977-03-17—Подача