Изобретение относится к вычислительной технике и может быть использовано для связи процессоров с запоминающими или периферийными устройствами.

Целью изобретения является повышение достоверности передачи информации в двух направлениях.

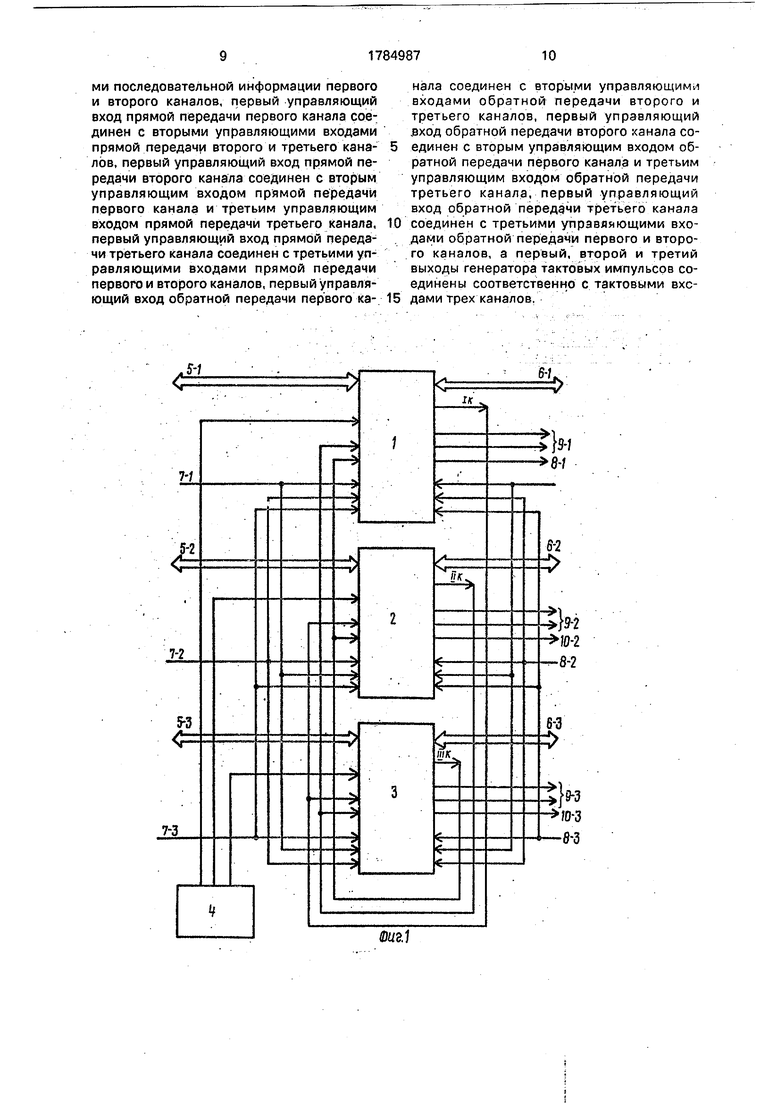

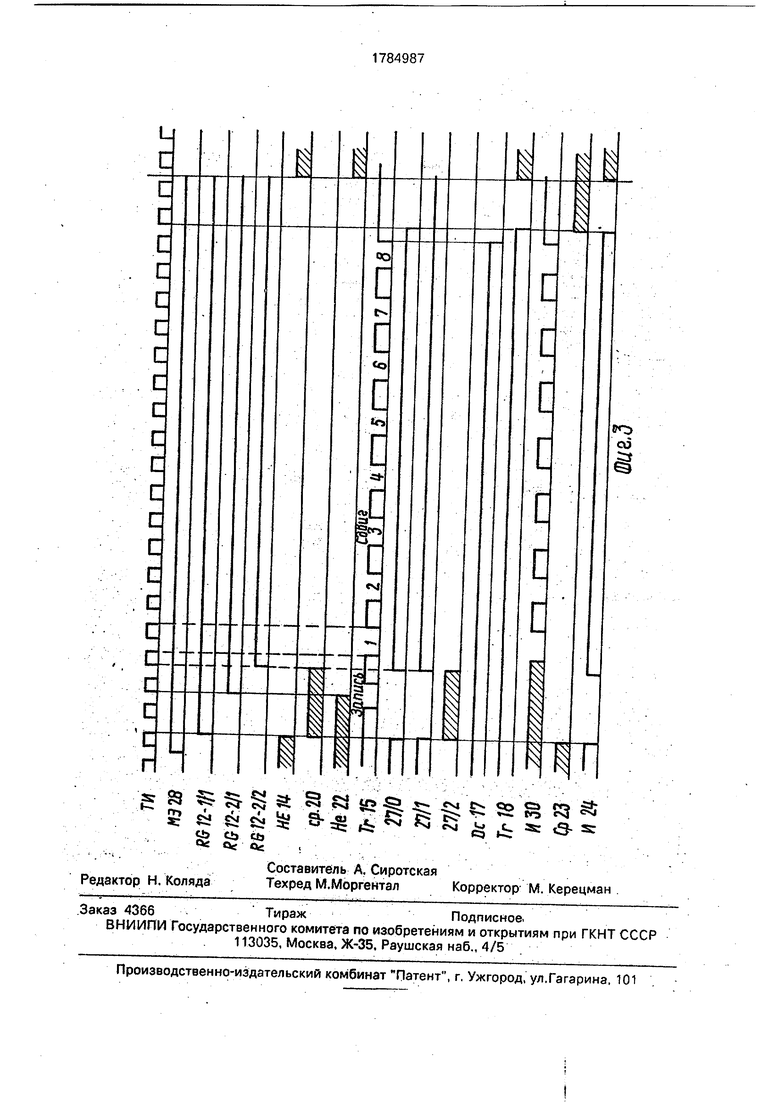

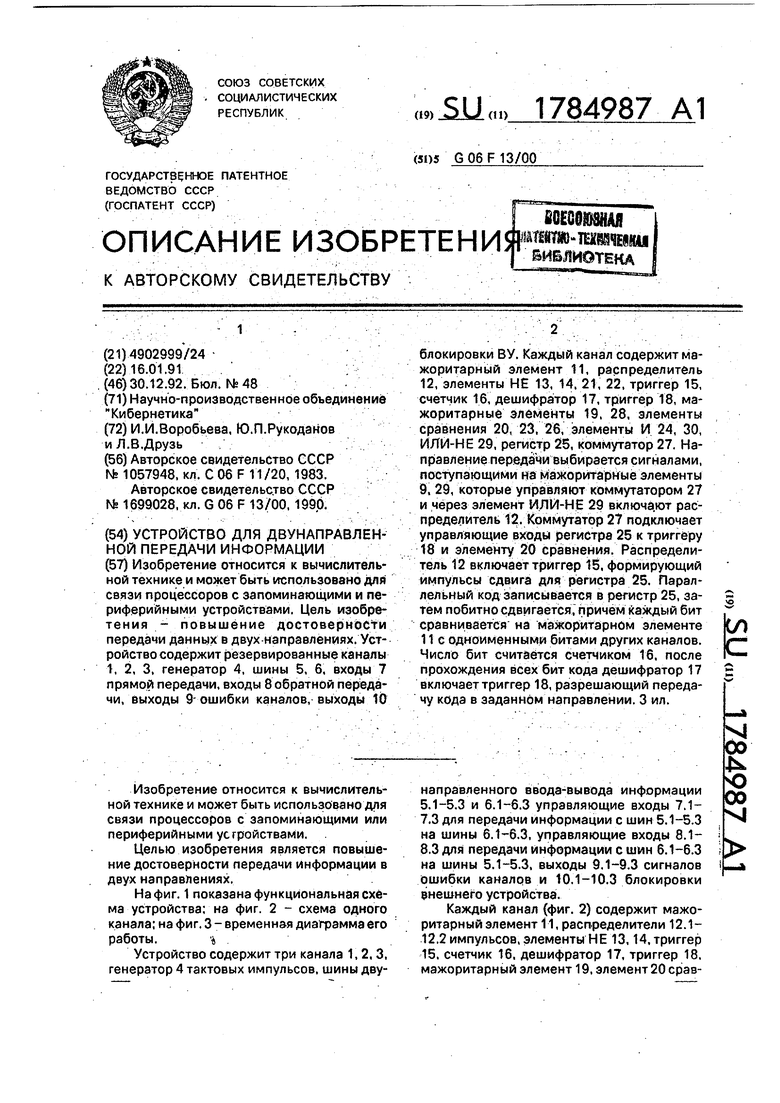

На фиг. 1 показана функциональная схема устройства; на фиг. 2 - схема одного канала; на фиг. 3 - временная диаграмма его работы.i

Устройство содержит три канала 1,2, 3, генератор 4 тактовых импульсов, шины двунаправленного ввода-вывода информации 5.1-5.3 и 6.1-6.3 управляющие входы 7.1- 7.3 для передачи информации с шин 5.1-5.3 на шины 6.1-6.3, управляющие входы 8.1- 8.3 для передачи информации с шин 6.1-6.3 на шины 5.1-5.3, выходы 9.1-9.3 сигналов ошибки каналов и 10.1-10.3 блокировки внешнего устройства.

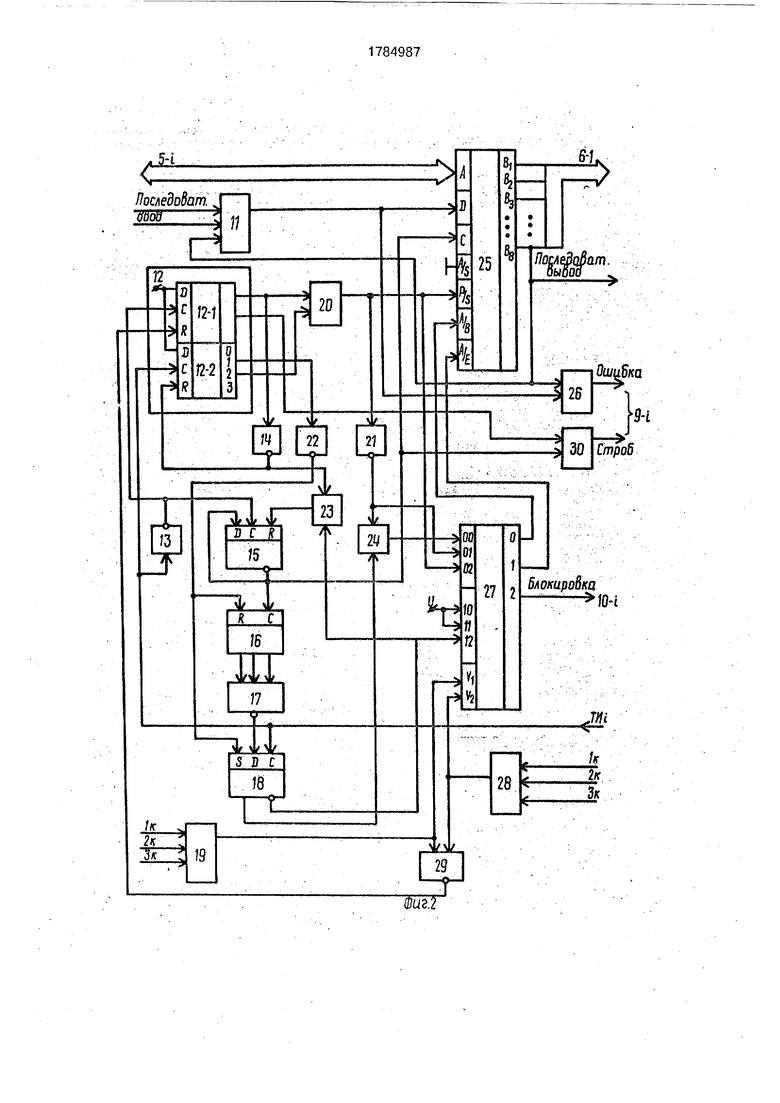

Каждый канал (фиг. 2) содержит мажоритарный элемент 11, распределители 12.1- 12.2 импульсов, элементы НЕ 13,14, триггер 15, счетчик 16, дешифратор 17, триггер 18. мажоритарный элемент 19, элемент 20 сравЧ|00

ь ю

00 VI

нения (ИСКЛЮЧАЮЩЕЕ ИЛИ), элементы НЕ 21, 22, элемент 23 сравнения, элемент И 24, регистр 25, элемент 26 сравнения, коммутатор 27, мажоритарный элемент 28, элемент ИЛИ-НЕ 29, элемент И 30.

Распределитель 12,1 и 12.2 выполнены на сдвигающих регистрах, например микросхемах серии 564ИР2. Регистр 25 выполнен на восьмиразрядном универсальном регистре 564ИР6. Коммутатор 27 - 564ЛС2, мажоритарные элементы 11,19, 28-564ЛП13, элементы 20, 23 сравнения - 564ЛП2. Генератор 4 тактовых импульсов является резервированным генератором, формирует три синхронные последовательности тактовых импульсов.

Устройство работает следующим образом. В исходном состоянии при отсутствии сигналов на всех вы водах устройства в каждом канале на выходе элемента ИЛИ-НЕ 29 устанавливается единичный сигнал, который удерживает в нулевом состоянии распределитель 12-1. При этом, на выходе элемента НЕ 14 также формируется единичный сигнал, который устанавливает в нуль распределитель 12-2. На входах элемента 20 сравнения совпадают нулевые сигналы, поэтому на выходе элемента 20 сигнал не формируется и на управляющем входе P/S регистра 25 установлен нулевой сигнал. На выходе элемента НЕ 22 также сформирован единичный сигнал, который устанавливает в нуль счетчик 16 и триггер 18 - в единичное состояние. Триггер 18 подготавливает к открыванию элемент И 24 и со своего инверсного выхода подает нулевой сигнал на один вход элемента 23 сравнения, на второй вход которого подается единичный сигнал с выхода элемента НЕ 14, На входах элемента 23 сигналы не совпадают, и на его выходе формируется единичный сигнал, устанавливающий в нулевое состояние триггер 15.

Режим передачи информации в направлении с шин 6 на шины 5 задается управля- ющими сигналами, которые кодом синхронно поступают на входы 8-1, 8-2, 8-3 трех каналов. В этом режиме в каждом канале выполняются следующие операции: запись параллельного кода байта информации с шин 6 в регистр 25; преобразование этого параллельного кода в последовательный путем его сдвигов с регистре 25. побитное сравнение этого кода с кодами других каналов и запись результирующего кода снова в регистр 25; выдача параллельного результирующего кода из регистра 25 на шины 5.

Для выполнения этих операций на управляющие входы А/Е, P/S, А/В регистра

26 подаются комбинации соответствующих потенциальных сигналов, а именно набор 010 - для выполнения первой операции, набор 101 - второй операции, набор 100 третьей операции. Одновременно с управляющими сигналами параллельные коды информации также синхронно поступают на шины 6-1, 6-2, 6-3. В каждом канале управляющие сигналы через входы 8 поступают

на можоритарный элемент 28, который срабатывает при наличии хотя бы двух сигналов из трех. Сигнал с выхода мажоритарного элемента 28 через элемент ИЛИ-НЕ 29 снимает сигнал с входа сброса распределителя 12-1 сдвига и подключает группу входов коммутаторов 27 к управляющим входам А/В, А/Е регистра 25. После снятия сигнала сброса распределителя 12-1 инверсные тактовые импульсы генератора 4 с выхода элемента НЕ 13 обеспечивают в нем запись и сдвиг сигнала логической 1, который постоянно подан на D-вход этого регистра.

При этом, на первом выходе распределителя 12-1 формируется потенциальный сигнал, который закрывает элемент НЕ 14 и формирует на выходе элемента 20 сравнения единичный сигнал. Этот сигнал поступает на вход P/S регистра 25 и закрывает

элемент НЕ 21, который, в свою очередь, закрывает элемент И 24. При этом на входы А/В, А/Е регистра 25 через коммутатор 27 подаются нулевые сигналы.

Таким образом, на управляющих входах

регистра 25 устанавливается код 010, разрешающий запись кода в регистр 25. Закрытый элемент НЕ 14 снимает сигнал с входа сброса в нуль регистра 12-2, который начинает сдвиг сигнала лог. 1 пофронтутактовых

импульсов генератора 4. Кроме того, после подачи нулевого сигнала с выхода элемента НЕ 14 на вход элемента 23 сравнения, на выходах последнего сигналы совпадают и на его выходе формируется нулевой сигнал,

разрешающий работу триггера 15.

Триггер 15 работает в счетном режиме от инверсных тактовых импульсов элемента НЕ 13 и формирует на своем инверсном выходе отрицательные импульсы, поступающие на тактовый вход регистра 25 и регулирующие заданный режим работы регистра 25. Первый импульс триггера 15 обеспечивает запись параллельного кода информации в регистр 25. После этого, по

фронту текущего тактового импульса генератора 4 формируется единичный сигнал на первом выходе распределителя 12-2, который закрывает элемент НЕ 22 и тем самым снимает сигнал с входа сброса счетчика 16 и единичного входа триггера 18. По

фронту следующего тактового импульса формируется единичный сигнал на втором выходе распределителя 12-2, который подается на вход элемента 20 сравнения, Так как у него совпадают единичные сигналы, то на его выходе и, следовательно, на P/S входе регистра 25 устанавливается нулевой сигнал.

Этот сиг-нал через коммутатор 27 выдается по выходу 10 канала во внешнее устройство и блокирует подачу им следующего байта информации на шины 6. При этом, на выходе элемента НЕ 21 формируется единичный сигнал, который открывает элемент И 24, подготовленный триггером 18. и на входы А/В, А/Е регистра 25 через коммутатор 27 подаются единичные сигналы.

На управляющих входах регистра 25 устанавливается код 101, реализующий режим сдвига кода в регистре 25. Импульсы сдвига формируются триггером 15, который подает их на тактовый вход регистра 25 и на вход счетчика 16.

Сдвигаемые биты кода с выхода регистра 25 подаются через информационный выход данного канала и соответствующие входы других каналов на мажоритарный элемент 11.

Таким образом, в каждом канале на мажоритарном элементе 11 сравниваются биты кода всех трех каналов. При совпадении бит хотя бы двух каналов из трех на выходе мажоритарного элемента 11 формируется соответствующее значение бита кода, которое записывается текущим импульсом сдвига в регистр 25. После сдвига всех бит кода в регистре 25 вновь записан параллельный код, совпадающий с аналогичными кодами по брльшинству каналов (в двух из трех). Число импульсов сдвига равно числу бит в байте параллельного кода, записанного ранее в регистре 25. Это число подсчитывается счетчиком 16 и декодируется дешифратором 17, на инверсном выходе кЪторого формируется нулевой сигнал. Это сигнал подается на D-вход триггера 18, и текущий тактовый импульс генератора 4 устанавливает триггер 18 в нулевое положение.

Триггер 18 сигналом со своего инверсного выхода через элемент 23 сравнения сбрасывает в нуль триггер 15, а сигналом со своего прямого выхода закрывает элемент И 24. При этом, на управляющих входах регистра 25 устанавливается код 100, соответствующий выдаче параллельного кода из регистра 25 на шины 5.

В процессе сдвига кода в регистре 25 его биты непрерывно сравниваются с битами мажоритарного элемента 11 с помощью элемента 26 сравнения. При несовпадении

этих бит на выходе элемента 26 сравнения формируется сигнал ошибки, который выдается во внешнее устройство по выходу 9 канала.

5Для стробирования сигналов ошибки во

внешнее устройство также выдаются импульсы сдвига через Элемент НЕ 30.

Режим передачи информации в направлении с шин 5 на шины 6 задается управля- 10 ющими сигналами, которые синхронно поступают на входы 7-1, 7-2, 7-3 трех каналов. В этом режиме в Каждом канале выполняются следующее операции: запись параллельного кода байта с шин 5 в регистр

5 25; преобразование параллельного кода в последовательный путем его сдвига в регистре 25, побитное сравнение этого кода с кодами других каналов и запись результирующего кода снова в регистр 25; вывод па0 раллельного результирующего кода из регистра 25 на шины 6.,

Для выполнения этих операций на управляющие входы А/Е, P/S, А/В регистра 25 подаются следующие коды: 111,101. Сиг5 налы с входов 7 поступают на мажоритарный элемент 19 каждого канала, который срабатывает при наличии хотя бы двух сигналов из трех сигналов. Сигнал с выхода мажоритарного элемента 19 через элемент

0 ИЛИ-НЕ 29, аналогично описанному выше запускает распределитель 12-1, 12-2. Кроме того, этот сигнал подается во второй управляющий вход коммутатора 27 и подключает его группу входов к управляющим входам

5 А/В, А/Е регистра 25, на которые постоянно поступают сигналы уровня лог 1м. В дальнейшем устройство работает аналогично описанному выше. Единичный сигнал с выхода элемента 20 сравнения

0 обеспечивает подачу кода 111 на управляющие входы регистра 25 и запись кода с шин 5 в регистр 25.

Далее на выходе элемента 20 сравнения формируется нулевой сигнал, на управляю5 щих входах регистра 25 устанавливается код 101, производится сдвиг информационного кода, сравнение его бит и запись результирующих бит снова в регистр 25 При этом, триггер 18 остается в единичном со0 стоянии и нулевой сигнал с его инверсного выхода поступает через коммутатор 27, выход 10 канала во внешнее устройство и запрещает прием информации с шин 6

По окончании контроля кода триггер 18

5 устанавливается в нулевое состояние, на выход 10 подается единичный сигнал, который разрешает внешнему устройству прием кода с шин 6, При этом управляющий код 101 на управляющих входах регистра 25 обеспечивает вывод информационного кода

на шины В при отключенных шинах А регистра 25.

После приема кода внешнее устройство сбрасывает управляющие сигналы с входов 7 или 8 устройства. При этом на выходе элемента ИЛИ-НЕ 29 формируется единичный сигнал, и устройство возвращается в исходное состояние.

Формула изобретения Устройство для двунаправленной передачи информации, содержащее генератор тактовых импульсов и первый (Йнал, содержащий счетчик, разрядные выходы которого соединены с информационными входами дешифратором, инверсный выход которого соединен с информационным входом первого триггера, второй триггер, коммутатор, первый выход которого является выходом признака блокировки канала, отличающееся тем, что, с целью повышения достоверности передачи данных в двух материалах, в него введены два канала, а в каждый канал - два распределителя импульсов, регистр, три мажоритарных элемента, три элемента сравнения, два элемента И, элемент ИЛИ-НЕ, четыре элемента НЕ, причем в каждом канале информационные входы-выходы регистра являются соответствующими информационными входами-выходами канала, тактовый вход каждого канала соединен с тактовым входом первого триггера, тактовым входом первого распределителя импульсов и через первый элемент НЕ - с тактовым входом второго триггера и тактовым входом второго распределителя импульсов, информационные входы двух распределителей импульсов соединены с шиной логической единицы канала, первый вход первого распределителя импульсов соединен с первым входом первого элемента сравнения и через второй элемент НЕ - с первым входом второго элемента сравнения и входом сброса в О первого распределителя, второй выход которого соединен с первым входом первого элемента И, выход которого является выходом строба соответствующего канала, второй вход первого элемента И соединен с тактовыми входами регистра, счетчика, информационным входом и инверсным выходом второго триггера, вход сброса которого соединен с выходом Равно1 второго элемента ; сравнения, второй вход которого соединен с первым входом пербой группы информационных входов коммутатора и инверсным выходом первого триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с первым еходом второй группы информационных

входой коммутатора, первый выход второго распределителя импульсов соединен через третий элемент НЕ с входом сброса счетчика и входом установки первого триггера,

5 второй выход второго распределителя импульсов соединен с вторым входом первого элемента сравнения, выход Равно которого соединен с входом управления последовательного ввода регистра, вторым

0 входом второй группы информационных входов коммутатора и через четвертый элемент НЕ - с вторым входом второго элемен- та И и третьим входом второй группы информационных входов коммутатора, вто5 рой и третий входы первой группы информационных входов которого соединены с шиной логической единицы канала, второй и третий выходы коммутатора соединены соответственное первым и вторым разряда0 ми входа управления параллельного синхронно-асинхронного ввода регистра, выход последовательной информации которого является одноименным выходом соответствующего канала и соединен с

5 первым входом третьего элемента сравнения и первым входом первого мажоритарного элемента, второй и третий входы которого образуют вход последовательной информации соответствующего канала,

0 выход первого мажоритарного элемента соединен с входом последовательной информации регистра и вторым входом третьего элемента сравнения, выход Равно которого является выходом сигнала ошибки соот5 ветсгвующего канала, первый, второй и третий разряды управляющего входа прямой передачи соответствующего канала соединены соответственно с первым, вторым и третьим входами второго мажоритарного

0 элемента, первый, второй и третий разряды входа обратной передачи. соответствующего канала соединены соответственно с первым, вторым и третьим входами третьего мажоритарного элемента, выходы второго и

5 третьего мажоритарных элементов соединены соответственно с первым и вторым управляющими входами коммутатора и первым и вторым входами элемента ИЛИ-НЕ, выход которого соединен с входом сброса

0 второго распределителя импульсов, выход последовательной информации первого канала соединен с первыми входами последовательной информации второго и третьего каналов, выход последовательной

5 информации второго канала - с первым входом последовательной информации первого канала и вторым входом последовательной информации третьего канала, выход последовательной информации

третьего канала соединен с вторыми входами последовательной информации первого и второго каналов, первый управляющий вход прямой передачи первого канала соединен с вторыми управляющими входами прямой передачи второго и третьего каналов, первый управляющий вход прямой передачи второго канала соединен с вторым управляющим входом прямой передачи первого канала и третьим управляющим входом прямой передачи третьего канала, первый управляющий вход прямой передачи третьего канала соединен с третьими управляющими входами прямой передачи первого и второго каналов, первый управляющий вход обратной передачи первого ка0

5

нала соединен с вторыми управляющими входами обратной передачи второго и третьего каналов, первый управляющий вход обратной передачи второго канала соединен с вторым управляющим входом обратной передачи первого канала и третьим управляющим входом обратной передачи третьего канала, первый управляющий вход обратной передачи третьего канала соединен с третьими управляющими входами обратной передачи первого и второго каналов, а первый, второй и третий выходы генератора тактовых импульсов соединены соответственно с тактовыми входами трех каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для тестового контроля группы цифровых блоков | 1984 |

|

SU1238084A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальное устройство для обмена данными микропроцессорной системы | 1985 |

|

SU1264193A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

Изобретение относится к вычислительной технике и может быть использовано для связи процессоров с запоминающими и периферийными устройствами. Цель изобретения - повышение достоверности передачи данных в двух направлениях. Устройство содержит резервированные каналы 1, 2, 3, генератор 4, шины 5, 6, входы 7 прямой передачи, входы 8 обратной передачи, выходы 9- ошибки каналов, выходы 10 блокировки ВУ. Каждый канал содержит мажоритарный элемент 11, распределитель 12, элементы НЕ 13, 14, 21, 22, триггер 15, счетчик 16, дешифратор 17, триггер 18, мажоритарные элементы 19, 28, элементы сравнения 20, 23, 26, элементы И 24, 30, ИЛИ-НЕ 29, регистр 25, коммутатор 27. Направление передачи выбирается сигналами, поступающими на мажоритарные элементы 9, 29, которые управляют коммутатором 27 и через элемент ИЛИ-НЕ 29 включа.ют распределитель 12. Коммутатор 27 подключает управляющие входы регистра 25 к триггеру 18 и элементу 20 сравнения. Распределитель 12 включает триггер 15, формирующий импульсы сдвига для регистра 25. Параллельный код записывается в регистр 25, затем побитно сдвигается, причем каждый бит сравнивается на мажоритарном элементе 11с одноименными битами других каналов. Число бит считается счетчиком 16, после прохождения всех бит кода дешифратор 17 включает триггер 18, разрешающий передачу кода в заданном направлении. 3 ил.

| Резервированный генератор тактовых импульсов | 1982 |

|

SU1057948A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный резервированный генератор | 1989 |

|

SU1699028A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1991-01-16—Подача