1

Изобретение относится к вычислительной технике и может быть использовано для формирования испытательных сигналов при контроле функционирования и диагностике неисправностей цифровых объектов.

Цель изобретения - расширение области применения за счет возможности изменения длины формируемой последовательности.

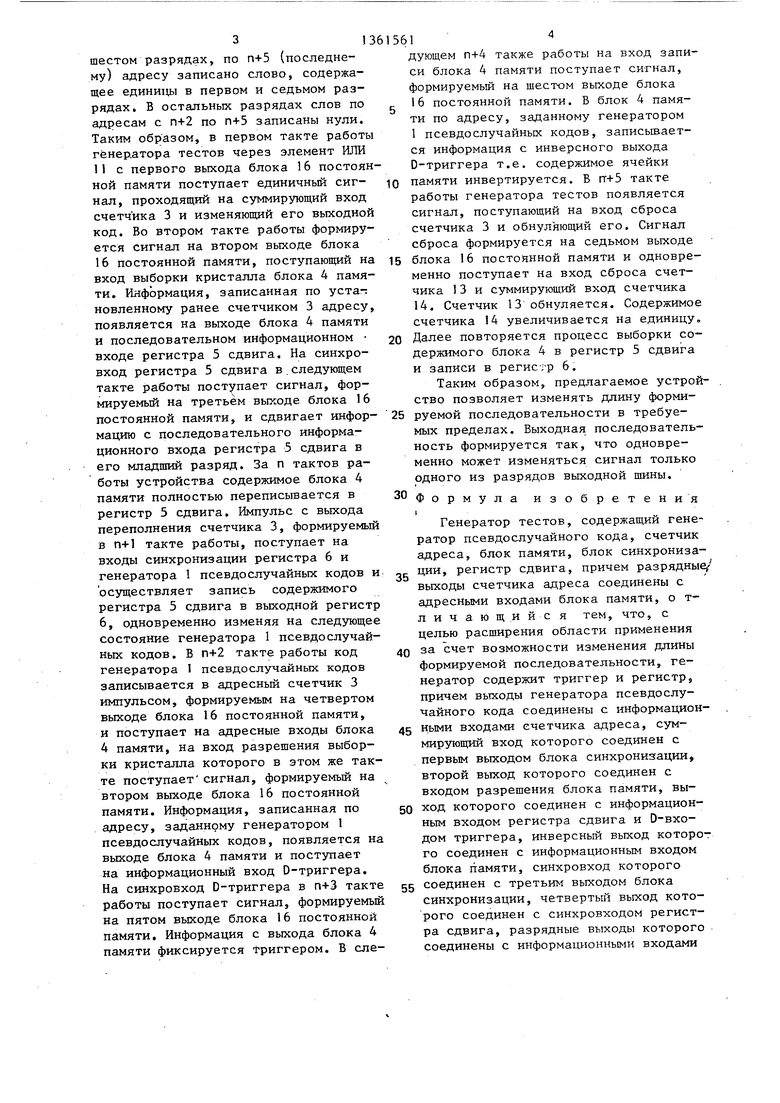

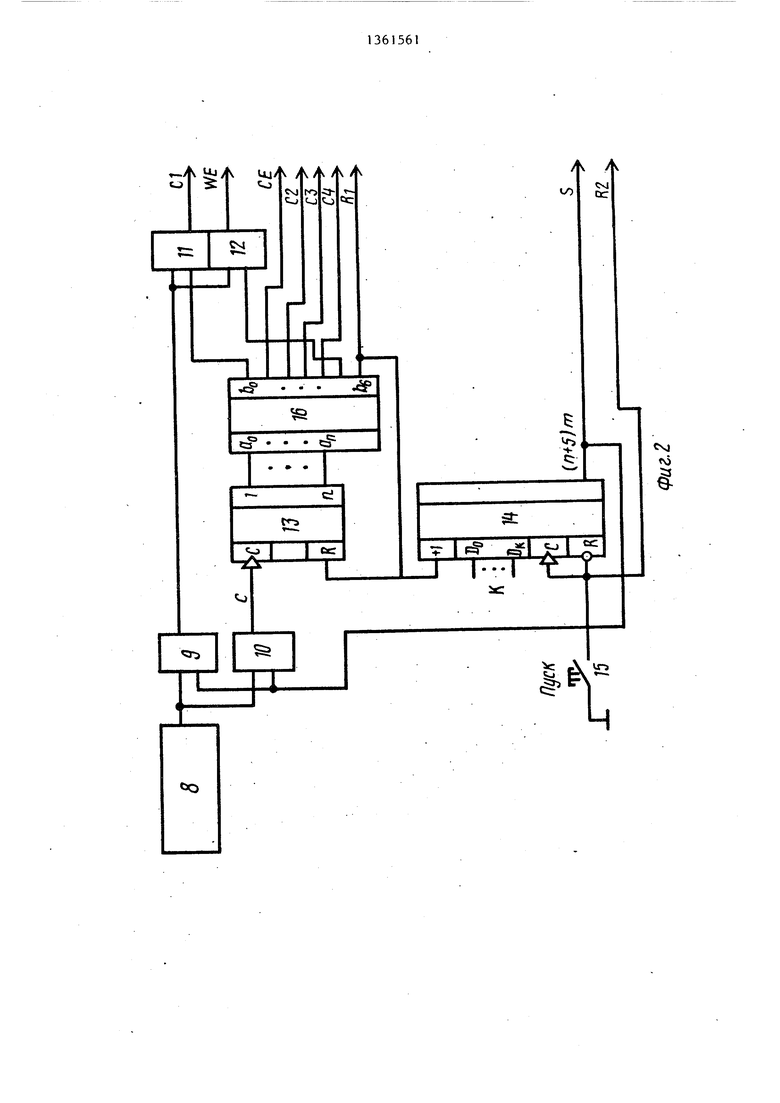

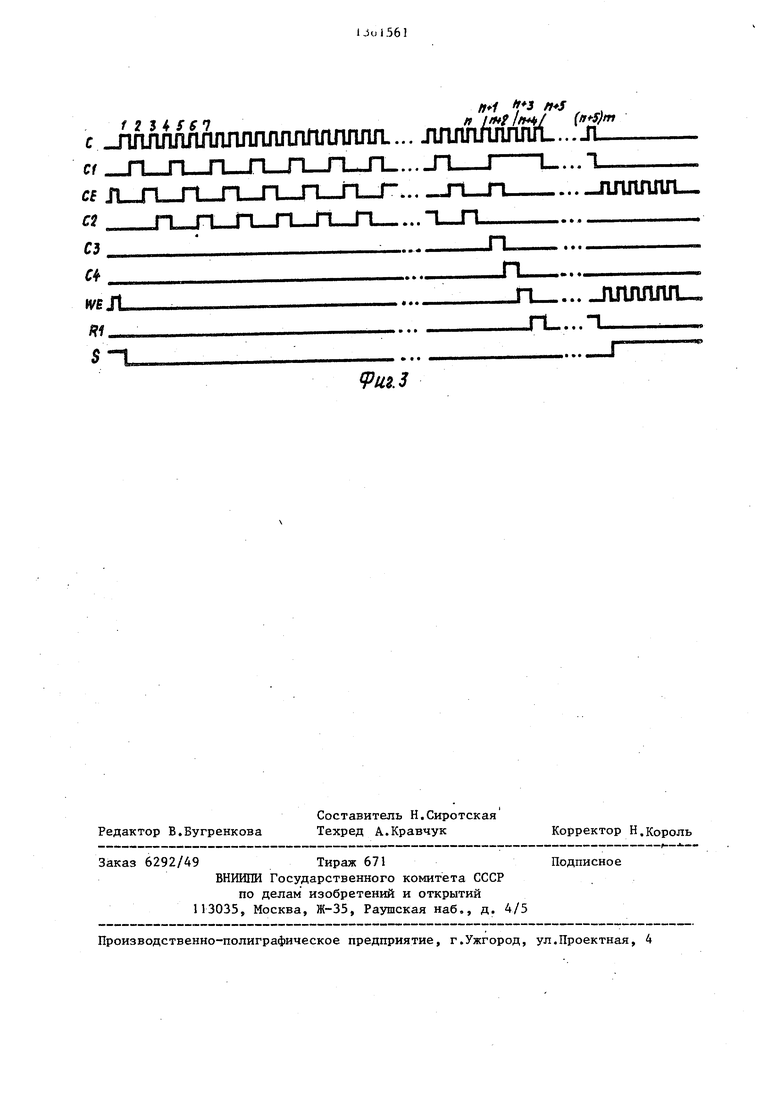

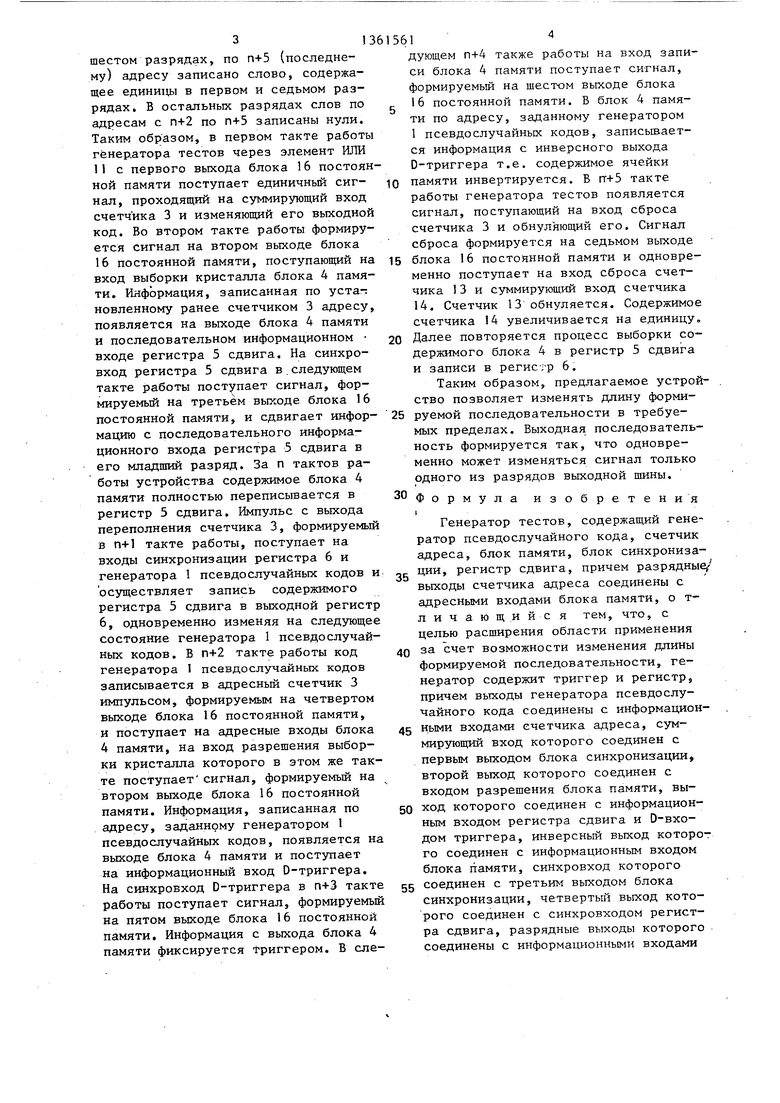

На фиг.1 изображена схема генератора; на фиг.2 - пример технической реализации блок а синхронизации; на фиг,3,- временные диаграммы работы блока синхронизации.

Генератор тестов (фиг.1) содержит генератор 1 псевдослучайных кодов, блок 2 синхронизации, счетчик 3 адреса, блок 4 памяти, регистр 5 сдвига, регистр 6 и триггер 7 с установочным входом.

Блок синхронизации (фиг.2) содержит синхрогенератор 8, элемент И9, элементы ИЛИ 10-12, адресный счетчик 13, суммирующий счетчик 14, кнопку

и блок 16 постоянной памяти.

Блок 4 памяти может быть реализован на элементе памяти Д565РУ2, блок

16постоянной памяти - на элементе К556РТ5, запрограммированном в соответствии с таблицей.

Генератор работает следующим образом.

При включении генератора тестов счетчики 3,13 и 14, триггер 7 и блок 4 памяти устанавливаются в случайное, заранее неопределенное состояние. Счетчик 14 блока 2 изменяет свое состояние после каждого импульса, поступающего с седьмого выхода блока 16 постоянной памяти, в сторону увеличения. Появление единицы на выходе ст.аршего разряда счетчика 14 запрещает прохождение импульсов с выхода .синхрогенератора 8 на вход счетчика 13 через элемент ИЛИ 10 и разрешает прохождение импульсов от синхронизатора 8 через элементы И 9 и ИЛИ П и 12. Одновременно единичный сигнал с выхода счетчика 14 устанавливает; триггер 7 в нулевое состояние на инверсном выходе. Уровень логического нуля присутствует на информационном входе блока 4 памяти, на вход записи которого поступают импульсы с выхода элемента ИЛИ 12.

15612

Импульсы с выхода элемента ИЛИ 11 синхронизации проходят на суммирующий вход счетчика 3, изменяя выходной код, поступающий на адресные входы блока 4 памяти. Таким образом, после включения генератора тестов и установки на выходе старшего разряда счетчика 14 уровня логической - еди 0 ницы происходит обнуление блока 4 памяти за счет циклического изменения адресов и записи по всем адресам нулевых значений.

Для работы генератора тестов в

15 режиме формирования испытательных сигналов необходимо на входах задания начального кода счетчика 14 установить начальный код. Разность макси- мального кода счетчика 14 и за20 данного начального кода определяет число выходных сигналов генератора тестов, формируемых в процессе работы. При кратковременном нажатии на кнопку Пуск сигнал нулевого уровня

25 сбрасывает в нулевое состояние счетчик 14 и обнуляет регистр 5 сдвига, регистр 6 и устанавливает в начальное состояние генератор 1 псевдослучайных кодов. При переходе из нулево30 го состояния в единичное на входе записи начального кода счетчика 14 происходит запись начального кода. Одновременно запрещается прохождение импульсов от синхрогенератора 8 на

тс выход элемента И 9 и разрешается прохождение импульсов на счетный вход счетчика 13 через элемент И 10. Выходной код счетчика 13 изменяется после каждого импульса и поступает

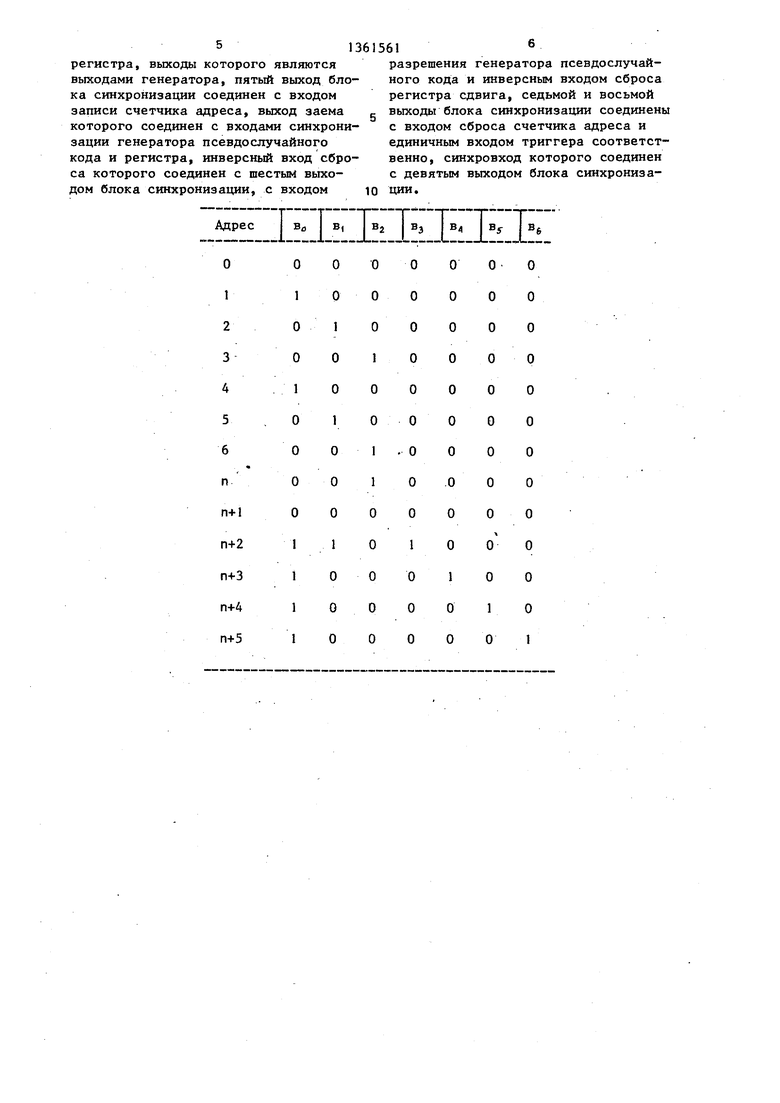

40 на адресные входы блока 16 постоянной памяти. В блоке 16 постоянной памяти записана информация таким образом, что по нулевому адресу содержится слово, содержащее нули во

45 всех разрядах, по первому - единицу в первом разряде и нули в остальных, по второму - единицу во втором разряде и нули в остальных, по третье- . му - единицу в третьем разряде и ну-50 ли в остальных, далее комбинации пов торяются, начиная с записанной по первому адресу, до адреса п, кратного трем. По п+ адресу записано слово, содержащее нули во всех разрядах,

55 по п+2 адресу записано слово, содержащее единицы и первом, втором и четвертом разрядах, по п+3 адресу - единицы в первом и пятом разрядах, по п+4 адресу - единицы в первом и

шестом разрядах, по п+5 (последнему) адресу записано слово, содержащее единшц, в первом и седьмом разрядах. В остальных разрядах слов по адресам с п+2 по п+5 записаны нули. Таким образом, в первом такте работы генератора тестов через элемент ИЛИ 11 с первого выхода блока 16 постоянной памяти поступает единичньй сигнал, проходящий на суммирующий вход счетчика 3 и изменяющий его выходной код. Во втором такте работы формируется сигнал на втором выходе блока 16 постоянной памяти, поступающий на вход выборки кристалла блока 4 памяти. Информация, записанная по устат новленному ранее счетчиком 3 адресу, появляется на вьгеоде блока 4 памяти и последовательном информационном входе регистра 5 сдвига. На синхро- вход регистра 5 сдвига в.следующем такте работы поступает сигнал, формируемый на третьем выходе блока 16 постоянной памяти, и сдвигает информацию с последовательного информационного входа регистра 5 сдвига в его младший разряд. За п тактов работы устройства содержимое блока 4 памяти полностью переписывается в регистр 5 сдвига. Импульс с выхода переполнения счетчика 3, формируемый в п+1 такте работы, поступает на входы синхронизации регистра 6 и генератора 1 псевдослучайных кодов И осуществляет запись содержимого регистра 5 сдвига в выходной регистр 6, одновременно изменяя на следующее состояние генератора 1 псевдослучайных кодов. В п+2 такте работы код генератора 1 псевдослучайных кодов записывается в адресный счетчик 3 импульсом, формируемым на четвертом выходе блока 16 постоянной памяти, и поступает на адресные входы блока 4 памяти, на вход разрешения выборки кристалла которого в этом же такте поступает сигнал, формируемый на втором выходе блока 16 постоянной памяти. Информация, записанная по адресу, заданному генератором 1 псевдослучайных кодов, появляется на выходе блока 4 памяти и поступает на информационный вход D-триггера. На синхровход D-триггера в п+3 такте работы поступает сигнал, формируемый на пятом выходе блока 16 постоянной памяти. Информация с выхода блока 4 памяти фиксируется Триггером. В следующем п+4 также работы на вход записи блока 4 памяти поступает сигнал, формируемый на шестом выходе блока

16 постоянной памяти. В блок 4 памяти по адресу, заданному генератором 1 псевдослучайных кодов, записьтает- ся информация с инверсного выхода D-триггера т.е. содержимое ячейки

памяти инвертируется. В гт+5 такте работы генератора тестов появляется сигнал, поступающий на вход сброса счетчика 3 и обнуляющий его. Сигнал сброса формируется на седьмом выходе

блока 16 постоянной памяти и одновременно поступает на вход сброса счетчика 13 и суммирующий вход счетчика 14. Счетчик 13 обнуляется. Содержимое счетчика 14 увеличивается на единицу.

Далее повторяется процесс выборки содержимого блока 4 в регистр 5 сдвига и записи в регистр 6.

Таким образом, предлагаемое устройство позволяет изменять длину формируемой последовательности в требуемых пределах. Выходная последовательность формируется так, что одновременно может изменяться сигнал только одного из разрядов выходной шины.

Формула изобретения I

Генератор тестов, содержащий генератор псевдослучайного кода, счетчик адреса, блок памяти, блок синхронизации, регистр сдвига, причем разрядные выходы счетчика адреса соединены с адресными входами блока памяти, о т- личающийся тем, что, с целью расширения области применения

за счет возможности изменения длины формируемой последовательности, генератор содержит триггер и регистр, причем выходы генератора псевдослучайного кода соединены с информационными входами счетчика адреса, суммирующий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с входом разрешения блока памяти, выход которого соединен с информационным входом регистра сдвига и D-BXO- дом триггера, инверсный выход которот го соединен с информационным входом блока памяти, синхровход которого

соединен с третьим выходом блока синхронизации, четвертый выход которого соединен с синхровходом регистра сдвига, разрядные выходы которого соединены с информационными входами

51361561

регистра, выходы которого являютсяразрешения генератора псевдослучай- выходами генератора, пятый выход бло-ного кода и инверсным входом сброса ка синхронизации соединен с входомрегистра сдвига, седьмой и восьмой записи счетчика адреса, выход заема выходы блока синхронизации соединены которого соединен с входами синхрони-с входом сброса счетчика адреса и зации генератора псевдослучайногоединичным входом триггера соответст- кода и регистра, инверсный вход сбро-венно, синхровход которого соединен са которого соединен с шестым выхо-с девятым выходом блока синхрониза- дом блока синхронизации, с входом юции.

f 2 4 f S Jff /ЛЧ/ (

с ЛШТЛ1ШППЛЛЛШШППЛППП.... ЛШ1ПЛЛГ1Ш1....Л-.

/ЛЧ/

...-плпплги.

-ruumnru

nL...-Т .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

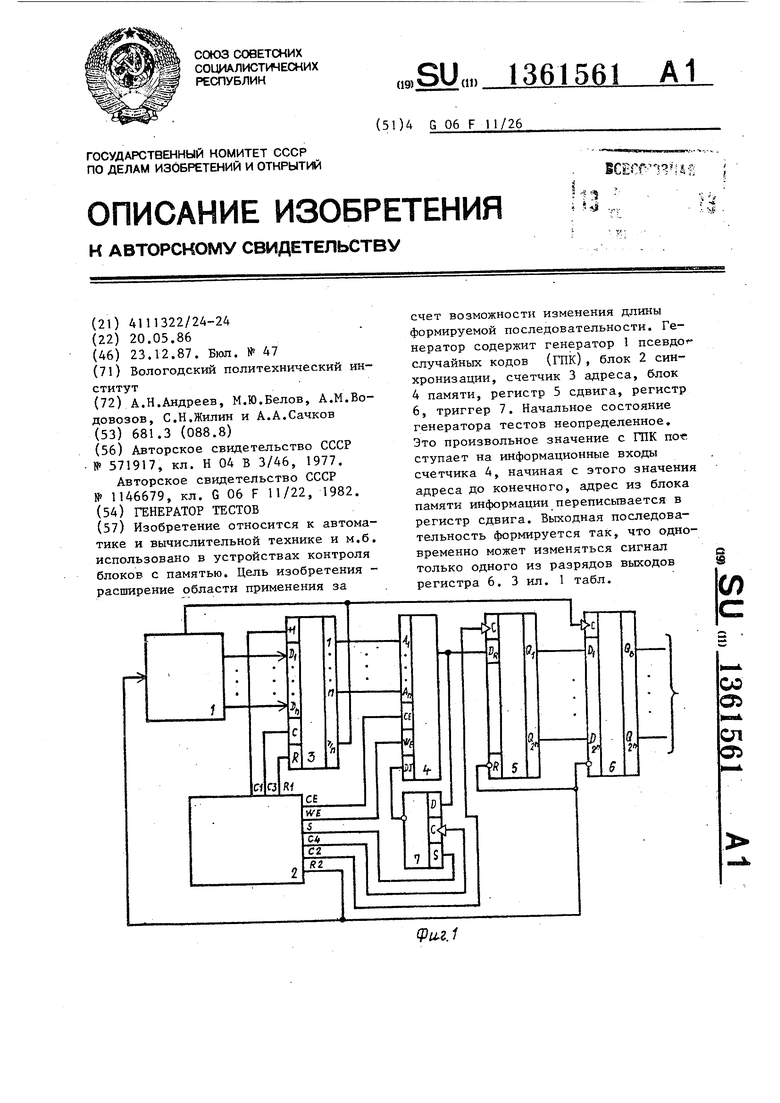

Изобретение относится к автоматике и вычислительной технике и м.б. использовано в устройствах контроля блоков с памятью. Цель изобретения - расширение области применения за счет возможности изменения длины формируемой последовательности. Генератор содержит генератор 1 псевдо - случайных кодов (ГПК), блок 2 синхронизации, счетчик 3 адреса, блок 4 памяти, регистр 5 сдвига, регистр 6, триггер 7. Начальное состояние генератора тестов неопределенное. Это произвольное значение с ГПК пое ступает на информационные входы счетчика 4, начиная с этого значения адреса до конечного, адрес из блока памяти информации переписьгеается в регистр сдвига. Выходная последовательность формируется так, что одновременно может изменяться сигнал только одного из разрядов выходов регистра 6. 3 ил. 1 табл. i (Л оо 05 ел О5 Фи-г./

Редактор В.Бугренкова Заказ 6292/49

Составитель Н.Сиротская Техред А.Кравчук

Тираж 671 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

9и.З

Корректор Н.Король Подписное

| Способ выделения ошибок из испытательного псевдослучайного сигнала в виде м-последовательности и устройство для его осуществления | 1975 |

|

SU571917A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР № 1146679, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-20—Подача