||1зобретение относится к радиотехнике и может быть использовано в качестве следящих измерителей и демодуляторов.

Цель изобретения - повышение точности при частых пропаданиях входного сигнала.:

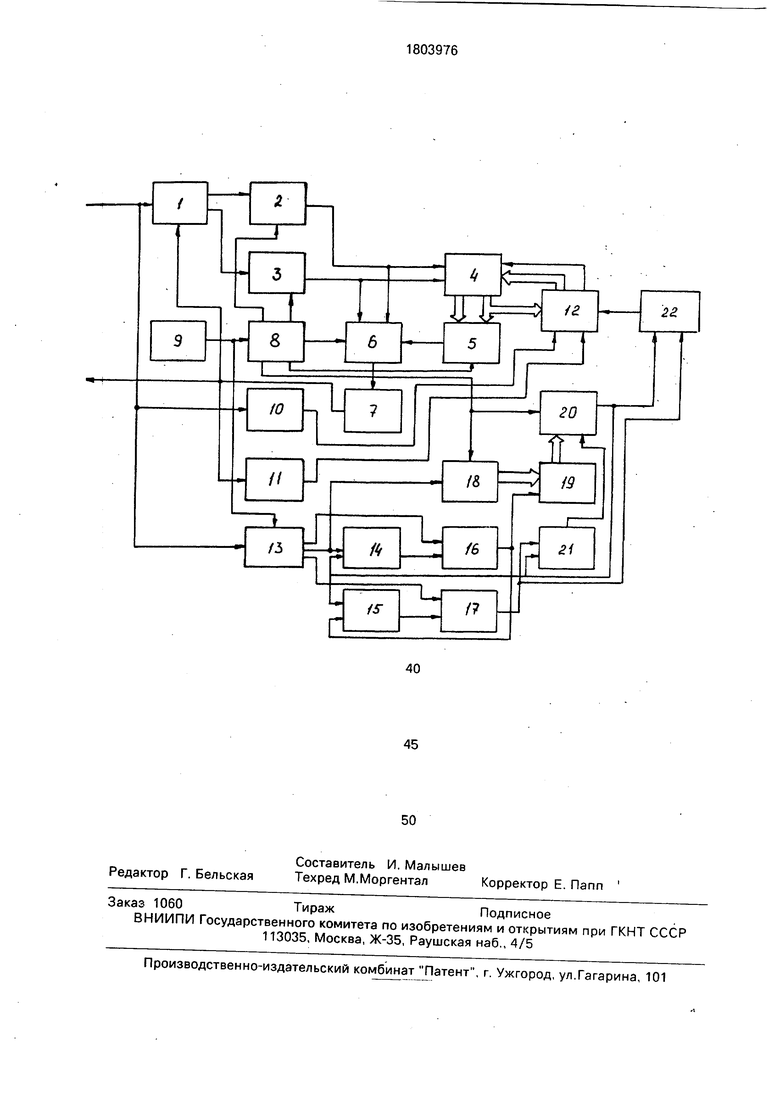

Йа чертеже приведена блок-схема устройства автоматической подстройки частоты.

Устройство автоматической подстройки частоты содержит: цифровой фазовый детектор 1, устройство усреднения канала до- бавле,ния 2, устройство усреднения канала вычитания 3, цифровой интегратор 4, преоб- разов|атель код-частота 5, устройство добав- ленияЬвычитания 6, основной делитель 7, распределитель импульсов 8, опорный генератор, первый выделитель фронта 10, второй выделитель фронта 11, блок частотной подстройки 12, дополнительный распределителе) импульсов 13, первый дополнительный РБ-триггер 14, второй дополнительный RS-Tpi/inep 15, первый элемент И 16, второй элемент И 17, первый счетчик 18, регистр 19, второй счетчик 20, элемент ИЛИ 21 и третий дополнительный RS-триггер 22. Первый

вход цифрового фазового детектора 1 объединен с входом первого выделителя фронта 11 и входом синхронизации дополнительного распределителя импульсов 13 и является входом устройства. Выход основного делителя 7 является выходом устройства и, кроме того, соединен с входом второго выделителя фронта 11 и вторым входом цифрового фазового детектора 1, первый выход которого соединен с первым входом устройства усреднения канала добавления 2, а второй выход цифрового фазового детектора 1 соединен с первым входом устройства усреднения канала вычитания 3, выход которого соединен с входом импульсов вычитания цифрового интегратора 4 и первым входом устройства добавления-вычитания 6. Выход устройства усреднения канала добавления 2 соединен с вторым входом устройства добавления-вычитания 6 и входом импульсов добавления цифрового интегратора 4, выходы которого соединены с информационными входами преобразователя код-частота 5, тактовым входом соединенного с первым выходом распределителя импульсов 8, а выход преобразователя

ел

с

00 О

СА

ю

Ј

ю

код-частота 5 соединен с третьим входом устройства добавления-вычитания 6, четвертый вход которого соединен с вторым выходом распределителя импульсов 8, соединенного с вторым выходом устройства ус- реднения канала вычитания 3. Четвертый выход распределителя импульсов 8 соединен с вторым входом устройства усреднения канала добавления 2, а вход распределителя импульсов 8 объединен с тактовым входом дополнительного распределителя импульсов 13 и соединен с выходом опорного генератора 9. Кроме того, выход устройства добавления-вычитания 6 соединен с входом основного делителя 7. Выходы первого выделителя фронта 10 и второго выделителя фронта 11 соединены соответственно с первым и вторым входами блока частотной подстройки 12. Информационные выходы блока частотной подстрой- ки 12 подключены к старшим входам цифрового интегратора 4, а информационные входы блока частотной постройки 12 подключены кЫ старшим выходам цифрового интегратора 4, Выход блока частотной подстройки 12 соединен с входом цифрового интегратора 4. Кроме того, один из входов первого элемента И 16 соединен с первым выходом дополнительного распределителя импульсов 13, а другой вход - с выходом первого дополнительного RS-триггера 14, S- вход которого объединен с входом сброса первого счетчика 18 и соединен с вторым выходом дополнительного распределителя импульсов 13, третий выход которого соеди- нен с одним из входов второго элемента И 17, а другой его вход соединен с выходом второго дополнительного RS-триггера 15, S- вход которого объединен с тактовым входом регистра 19 и подключен к выходу первого элемента И 16. Таковые входы счетчиков 18, 20 подключены к пятому дополнительному выходу распределителя импульсов 8, причем выход первого счетчика 18 соединен с информационным входом регистра 19, а его выход соединен с входом предварительной установки со сдвигом на один разряд вправо второго счетчика 20, вход управления предварительной записью которого подключен к выходу элемента ИЛИ 21, Вход сигнала переполнения второго счетчика 20 подключен к S-входу третьего, дополнительного триггера 22, к одному из входов элемента ИЛИ 21 и R-входам первого и второго дополнительных RS-триггеров 14, 15. Дру-

гой вход элемента ИЛИ 21 и R-вход третьего дополнительного RS-триггера подключены к выходу второго элемента И 17, а выход третьего дополнительного RS-триггера 22 подключен к входу блокировки блока частотной подстройки 12.

Формула изобретения Устройство автоматической подстройки частоты по авт. св. № 1698987, отличающееся тем, что, с целью повышения точности при частых пропаданиях входного сигнала, в него введены дополнительный распределитель импульсов, тактовый вход и вход синхронизации которого подключены соответственно к выходу опорного генератора и входу устройства, последовательно соединенные первый дополнительный RS- триггер и первый элемент И, последовательно соединенные второй дополнительный RS-триггер и второй элемент И, последовательно соединенные первый счетчик и регистр, а также второй счетчик, элемент ИЛИ и третий дополнительный RS-триггер, при этом распределитель импульсов снабжен пятым выходом, подключенным к тактовым входам первого и второго счетчиков, выход сигнала переполнения второго счетчика подключен к S-входу третьего дополнительного RS-триггера, к одному из входов элемента ИЛИ и R-входам первого и второго дополнительных RS-триггеров, другой вход элемента ИЛИ и R-вход третьего дополнительного RS-триггера подключены к выходу второго элемента И, первый выход дополнительного распределителя импульсов подключен к другому входу первого элемента И, второй выход - к S-входу первого дополнительного RS-триггера и входу сброса первого счетчика, а его третий выход - к другому входу второго элемента И, выход первого элемента И подключен к S-входу второго дополнительного RS-триггера и тактовому входу регистра, выход регистра подключен к входу предварительной установки со сдвигом на один разряд вправо второго счетчика, вход управления предварительной записью которого подключен к выходу элемента ИЛИ, а выход третьего дополнительного RS-триггера подключен к входу блокировки по меньше мере одного из блоков, включенных между выходами первого и второго выделителей фронтов и входам управления параллельной записью старших разрядов и информационными входами N старших разрядов цифрового интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Устройство для приема частотно-манипулированных сигналов | 1978 |

|

SU768000A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU803112A1 |

| Устройство определения перерывов цифрового сигнала в радиоканале | 1988 |

|

SU1538262A1 |

| Устройство для приема дискретных сигналов | 1990 |

|

SU1823146A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

Использование: радиотехника. Сущность изобретения: точность подстройки при частых пропаданиях сигнала повышается путем обеспечения режима памяти и отключения цепи автоподстройки частоты при частом пропадании входного сигнала. 1 ил.

| Самоостанов к кеттельной машине, действующий при пропуске ею кеттельного шва | 1954 |

|

SU98987A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-23—Публикация

1990-09-21—Подача