Изобретение относится к области цифровой вычислительной техники, в частности к устройствам специализированного назначения для реализации целого ряда вычислительных операций и может быть использовано в различных областях народного хозяйства, в системах автоматизированного управления.

Цель изобретения - расширение функциональных возможностей за C4ef дополнительного вычисления линейных функций и корня квадратного из линейных функций,

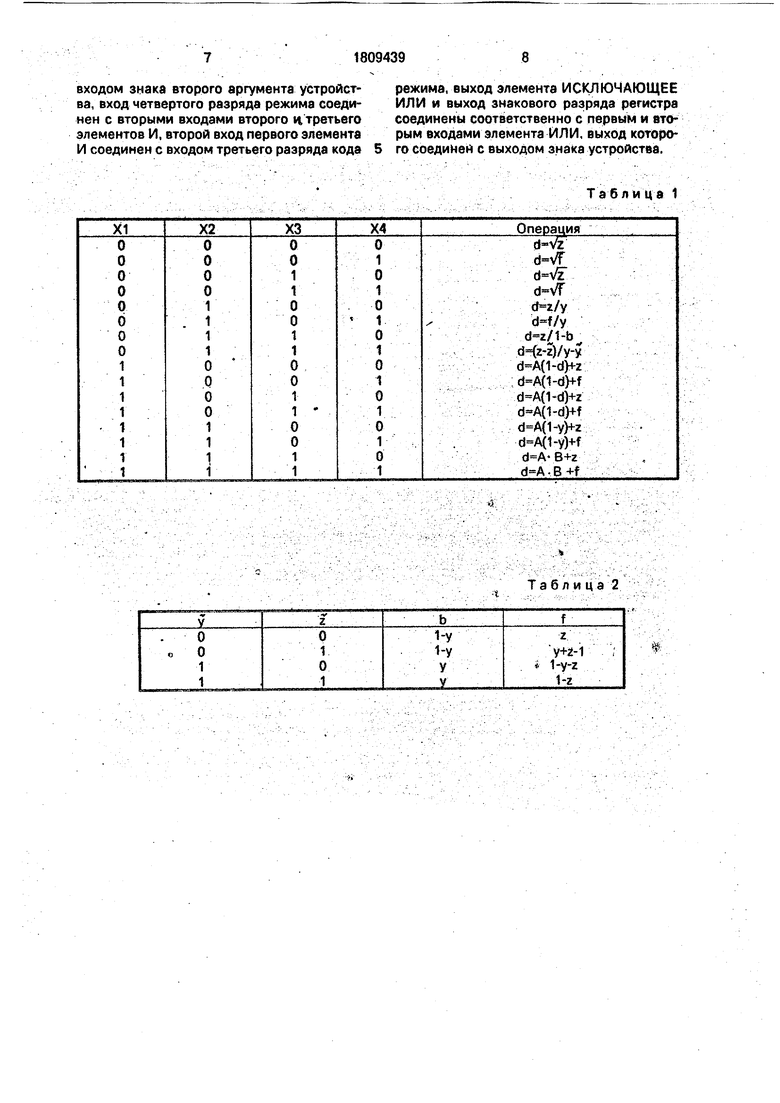

На чертеже представлена функциональная схема устройства. В табл.1 приведены операции.реализуемые в данном устройстве, в табл.2 приведены значения b и f.

Устройство содержит входы 1,3, 16, 19, являющиеся входами соответствующих разрядов кода режима (х-1 х2 хЗ х4), вход коэффициента устройства (А)2, мультиплексоры 4(1)-4(4), блоки преобразования прямого кода в дополнительный 5(1)-5(4), умножитель 6, сумматоры 7(1)-7(2), регистр - 8, формирователь импульса 9, элемент ИЛИ - 10, элементы И 11(1)-11(3), вход мантиссы первого аргумента (у) 12, выход мантиссы устройства (d),,- 13, выход знака устройства мантиссы (d) 14, вход знака первого аргумента (у) - 15, вход мантиссы второго аргумента)-17, элемент ИСКЛЮЧАЮЩЕЕ ИЛ И- 18, вход знака второго аргумента (z) - 20.

Изобретение иллюстрируется следующими примерами:

Рассмотрим операцию: d Vz. где z z z ... z. Примем n 4. На вход 17 подали мантиссу числа z: 0110, на вход 20 подали значение знакового разряда z 0. В соответствии с табл.1 на входы 1, 3, 16, 19 подали код х1 х2 хЗ х4 0000 соответственно. При этом открыты первые каналы мультиплексоров 4(1), 4(3), 4(4), На выходе умножителя 6 код нуля, на выходе сумматора 7(1) имеем: 0000 + 0110 0110. Следовательно, по окончании переходных процессов формирователь импульса 9 вырабатывает сигнал и значение кода 0110 записывается в регистр

СО

с

00

S

;со Ю

8. После чего на выходе умножителя 6 имеем: 0110 х 1010 00111100, старшие четыре разряда на первом сумматоре 7(1) складываются со значением мантиссы числа и получаем: 0011 + 0110 1001. Этот код записывается в регистр 8. На выходе умножителя б имеем: 1001 х0111 00111111, на выходе сумматора 7(1): 0011 +0110 1001, это значение записывается в регистр 8. Итак на выходе мантиссы устройств 13 имеем d 1001, на знаковом, выходе 14 имеем d 0. Результат операции d V0.0110 0.1001.

Рассмотрим операцию d -, определяемую кодом режима 0100 (табл. 1) при следующих исходных данных: z 0.0100, у 0.1100. Для этого на вход 17 поступает код мантиссы числа z 0100, на вход 12 поступает.код мантиссы числа у .1100, на вход 20 поступает значение знакового разряда г- 0, на BxoflJS поступает значение знакового разряда у 0. В соответствии с таблицей 1 на входы 1, 3, 16, 19 код х1 х2 хЗ х4 0100 соответственно. При этом открыты первый канал мультиплексора 4(3), второй канал Мультиплексора 4(4), первый канал мультиплексора 4(1), т.к. на его адресном входе находится код 00, снимаемый с элементов И 11(2), 11(3). На выходе элемента И 11(1) - О (при этом открыт второй канал мультиплексора 4(2), на выходе преобразователя прямого кода в дополнительный 5(1) : 0100, который через мультиплексор 4(2) поступает. на вход второго канала мультиплексора 4(4), на выходе мультиплексора 4(1) имеем код: 0-110, котырый на сумматоре 7(1) складывается со значением старших разрядов выхо-. да умножителя 6. Т.к. на выходе умножителя б находится код нуля, то на выходе сумматора 7(1) имеем: 0000 + 0100 0100. Следовательно, по окончанию переходных процессов формирователь импульса 9 вырабатывает сигнал и значение кода 0100 запи- сывается в регистр 8. На выходе умножителя 6 имеем: 0100 х 0100 00010000, на выходе сумматора 7(1) получаем 0001 + 0100 0101. Этот код записывается в регистр 8. На выходе умножителя б имеем :0101 х 0100 00010100. Итерационные процессы закончены, т.к. код 0101 на выхо- де регистра 8 не вызывает изменения кодов на выходах умножителя б и сумматора 7(1). Следовательно, найден результат. На выходе элемента ИЛИ 10 находится значение знакового разряда результата 3 0. На выходе регистра 8 код мантиссы d 0101.

Рассмотрим операцию d - , определяемую кодом режима: 0101 (табл.1) при следующих исходных данных , г 1.1100, yj

1.0100. Следовательно, на входе 17 находится код г - 1100, на входе 20 z-- 1, на входе 12 код у 0100, на в ходе 15 у 1.

В соответствии с таблицей 1 на входы 1,

3, 16, 19 поступает код х1 х2 хЗ х4 0101 соответственно. При этом открыты первый канал мультиплексора 4(3), второй канал мультиплексора 4(4), четвертый канал мультиплексора 4(1), т.к. на его адресном входе

0 находится код 11, снимаемый с выхода элементов И 11(2),. 11(3), на выходе элемента И 11(1)- О, на выходе преобразователя прямого кода в дополнительный 5(1) код: 1100, который через второй канал мультиплексо5 ра 4(2) поступает на вход второго канала мультиплексора 4(4), на выходе преобразователя прямого кода в дополнительный 5(3) имеем код: 0100, который через четвертый канал мультиплексора 4(1) поступает на вто0 рой вход сумматора 7(1). Следовательно, на этом входе имеем значение функции f 1 - z в соответствии с таблицей 2 исходя из значений знаковых разрядов у z 1. На выходе регистра 8 код нуля, следовательно,

5 на выходе умножителя 6 ноль, на выходе сумматора 7(1) имеем: 0000 + 0100 0100. По окончанию переходных, процессов формирователь импульса 9 вырабатывает сигнал и значение кода 0100 записывается в регистр

0 8. На выходе умножителя 6 получаем: 0100 х 1100 00110000, на выходе сумматора 7(1): 0011 + 0100 0111, формирователь импульса 9 записывает код: 0111 в регистр 8. На выходе .умножителя 6 имеем: 0111 х 1100

5 01010100, на выходе сумматора 7(1): 0101 + 0100 1001. Формирователь импульса 9 записывает код 1001 в регистр 8. На выходе умножителя 6: 10Q1 х 1100 01101100, на выходе сумматора 7(1): 0110 + 0100 1010.

0 формирователь импульса 9 записывает код 1010 в регистр 8. На выходе умножителя 6: 1010 х 1100 01111000, на выходе сумматора 7(1): 0111 + 0100 1011. Формирователь импульса 9 записывает код 1011 в регистре.

5 На выходе умножителя 6: 1011 х 1100 10000100. на выходе сумматора 7(1): 1000+ + 0100 1100. Формирователь импульса 9 записывает код 1100 в регистр 8. На выходе умножителя 6: 1100 х 1100 10010000, на

0 выходе сумматора 7(1): 1001 + 0100 1101. Формирователь импульса 9 записывает код 1101 в регистр 8. На выходе умножителя 6: 110V.X 1100 10011100, На выходе сумматора 7(1): 1001 + 0100 1101. Итерационные

5 процессы закончены, т.к. код: 1101 на выходе регистра 8 не вызывает изменения кодов, на выходах умножителя 6 и сумматора 7(1). Следовательно, найден результат. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 находится О, на выходе знакового разряда

регистра 8 - О, следовательно, на выходе элемента ИЛИ 10 имеем значение знакового разряда в 0, а на выходе регистра 8 имеем значение мантиссы результата d 1101.

Рассмотрим операцию d A -(1 - d) + z, 5 определяемую кодом режима: 1000 (табл.1) при следующих исходных данных А - 1010, z 0.1100. На вход 2 подали код мантиссы числа А 1010, на вход 17 поступает код мантиссы числа z -1100 на вход 20 значение 10 z 0. В соответствии с таблицей 1 на входы 1, 3, 16, 19 поступает код х1 х2 хЗ х4 1000 соответственно. При этом открыты второй канал 4(3), первый канал мультиплексора 4(4), первый канал мультиплексора 4(1), т.к. 15

на. его адресном входе находится код 00, снимаемый с выхода элементов И 11(2), 11(3). На выходе регистра 8 код нуля, следовательно, на выходе умножителя б код нуля, на выходе сумматора 7(1) имеем: 0000 + 1100 20 . 1100. Формирователь импульса 9 записывает код 1100 в регистр 8. Поэтому на выходе преобразователя прямого кода в дополнительный 5(4) имеем: 0100, на выхо- деумножителя 6:1010x0100 00101000. На 25 выходе сумматора 7(1):-0010+1100 1110. Формирователь импульса 9 записывает код 1110 в регистр 8. На выходе прямого кода в . дополнительный 5(4): 0010, на выходе умножителя 6:1010x0010 00010100, на выходе 30

сумматора 7(1): 0001 + 1100 1101. Формирователь импульса 9 записывает код 1101 в регистр 8. На выходе преобразователя прямого кода в дополнительный 5(4): 0011, на выходе умножителя 6:1010x0011 00011110, 35 на выходе сумматора 7(1): 0001 + 1100 1101. Итерационные процессы закончены, т.к. код 1101 на выходе регистра 8 не вызывает изменения кодов на выходах умножителя б и сумматора 7(1). Следовательно, 40 ; найден результат. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 - О на выходе элемента ИЛИ 10 - О, следовательно, d 0, а на выходе регистра 8 имеем значение мантиссы результата d 1101.45

Формула изобретения

Устройство для вычисления элементарных функций, содержащее первый и второй 50 коммутаторы, с первого по третий блоки преобразования прямого кода в дополнительный, умножитель, первый и второй сумматоры, формирователь импульсов, регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, 55 первый и второй входы которого соединены «с соответствующими управляющими входами первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, выход которого соеДинен с информационным входом регистра и входом формирователя импульса, выход которого соединен с входом записи регистра, выход которого соединен с выходом мантиссы устройства, вход мантиссы первого аргумента которого соединен с первым информационным входом второго коммутатора и через первый блок преобразования прямого кода в дополнительный с вторым информационным входом второго коммутатора, вход мантиссы второго аргумента устройства соединен с входом первого слагаемого второго сумматора, входом второго преобразователя прямого кода в дополнительный и первым информационным входом первого коммутатора, выход второго сумматора соединен через третий преобразователь прямого кода в дополнительный с вторым информационным входом первого коммутатора, третий информационный вход которого соединен с выходом второго сумматора, вход второго слагаемого которого соединен с входом мантиссы первого аргумента устройства, четвертый информационный вход первого коммутатора соединен с выходом второго преобразователя прямого кода в дополнительный, выход умножителя соединен с входом второго слагаемого первого сумматора, отличающееся тем, что, с целью расширения функциональных возможностей за счет дополнительного вычисления линейных функций и корня квадратного из линейных функций, в него введены третий и четвертый коммутаторы, четвертый преобразователь прямого кода в дополнительный, три элемента И и элемент ИЛИ, причем входы первого и второго сомножителей умножителя соединены с выходами соответственно третьего и четвертого коммутаторов, управляющие входы которых соединены с входами соответственно первого и второго разрядов кода режима устройства, выход мантиссы регистра соединен с первым информационным входом третьего коммутатора и через четвертый преобразователь прямого кода в дополнительный с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с выходом второго коммутатора, второй информационный вход третьего коммутатора соединен с входом коэффициента, вход знака первого аргумента которого соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с управляющим входом второго коммутатора и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с

входом знака второго аргумента устройства, вход четвертого разряда режима соединен с вторыми входами второго и, третьего элементов И, второй вход первого элемента И соединен с входом третьего разряда кода

режима, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход знакового разряда регистра соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с выходом знака устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1988 |

|

SU1509880A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления корня квадратного из суммы квадратов | 1989 |

|

SU1695295A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2013 |

|

RU2513915C1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1575177A1 |

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для выполнения вычислительных операций. Известные устройства, решающие указанную задачу, имеют ограниченные функциональные возможности. Цель изобретения - расширение функциональных возможностей за счет линейных функций и корня квадратного из линейных функций. Поставленная цель достигается за счет введения дополнительных двух мультиплексоров, элемента ИЛИ. трех элементов И и установления новых связей. Использование указанных элементов устройства и новых связей позволяет расширить функциональные возможности устройства. 1 ил., 2 табл.

Таблица 1

, :.-. ..у :.vv -. Та бл и ц а 2

| Устройство для решения алгебраических уравнений | 1984 |

|

SU1259286A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1993-04-15—Публикация

1990-04-16—Подача