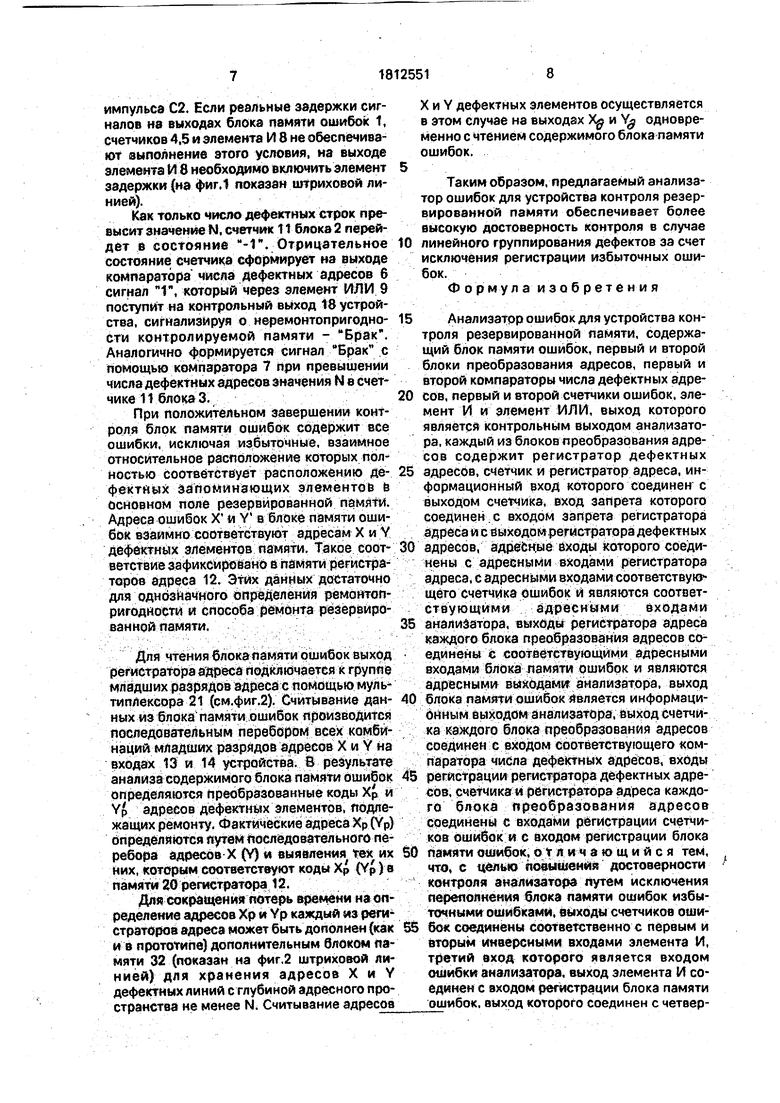

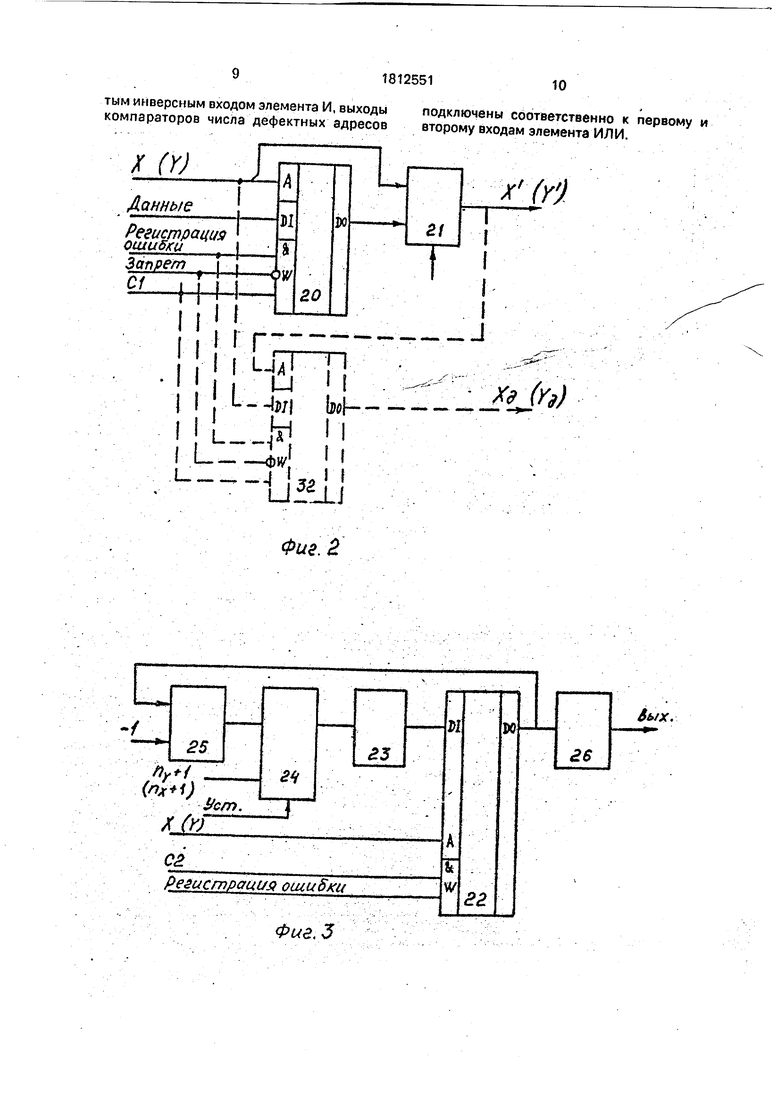

ресного пространства памяти 22 должна совпадать с емкостью соответствующего регистратора дефектных адресов. Регистр 23 служит для фиксации данных на входе памяти на время записи. Вычитатель 25 осуществляет вычитание единицы из содержимого памяти, обеспечивая работу каждой ячейки памяти в режиме вычитающего счетчика. Мультиплексор 24 служит для записи в регистр 23 и далее в каждую ячейку памяти 22 начального кода счетчика. Дешифратор 26 формирует на выходе сигнал 1, если адресуется ячейка памяти 25 с нулевым состоянием.

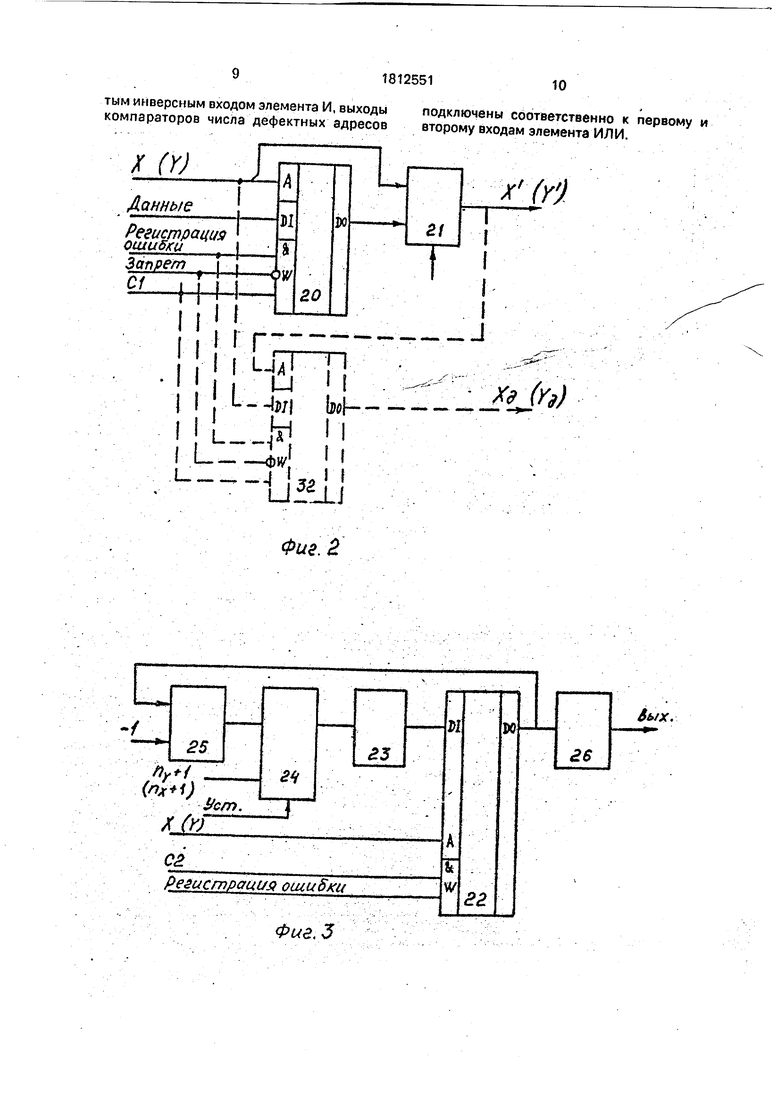

Для пояснения работы устройства рассмотрим структуру испытуемой резервной памяти (см.фиг.4). Испытуемая память.содержит основное поле 27 запоминающих элементов, пх резервных строк 28 и пу ре-. зервныхстолбцов 29. Координаты элементов основного поля задаются адресами X и У. Каждая строка X или столбец Y основного поля, в которых имеются дефектные элементы памяти, могут быть замещены соответствующей резервной строкой или. столбцом. Еси в строке X основного поля имеется один дефектный элемент 30, то дефект может быть устранен покрытием дефектного элемента одной резервной строкой 28 или столбцом 29. При двух дефектах в строке X потребуются два резервных столбца 29 или одна резервная строка 28. Если количество дефектных элементов в строке X превышает количество резервных столбцов пу, дефект может быть устранен только резервной строкой 28, Таким образом, регистрировать более пу+1 ошибок в строке X не имеет смысла, аналогично, не имеет смысла регистрировать более пх+1 ошибок 31 в столбце Y, т.к . все последующие ошибки не влияют на способ ремонта, т.е. являются избыточными. Если не прини- .мать в расчет йзбыточные:ошибки, то максимальное количество ошибок, которые могут быть покрыты резервными элемента- Ми, равно

. . D (nx+ 1) ny + (ny + 1)пх, а максимальное допустимое количество дефектных адресов равно

NX пх + пу(пх +1) пх + пу + пх пу;

NX - пу пх (nv + 1) NX N. Таким образом, при любом соотношении числа резервных элементов 28 и 29 определяющими для ремонта памяти являются ошибки, которые могут быть зафиксированы в памяти емкостью N2 элементов. .

Анализатор работает следующим образом. Перед началом контроля резервированной памяти выполняется процедура начальной установки, при этом обнуляется

каждая ячейка блока памяти ошибок 1, каждая ячейка регистратора дефектных адресов 10 и регистратора адреса 12 блоков 2 и 3.

В каждую ячейку первого счетчика оши-. бок 4 заносится число пу+1. а в каждую ячейку второго счетчика ошибок 5 - число пх + 1. В счетчики 11 блоков 2 и 3 заносится число N. Цепи, обеспечивающие начальную установку анализатора, на фиг.1 не показа0 мы,

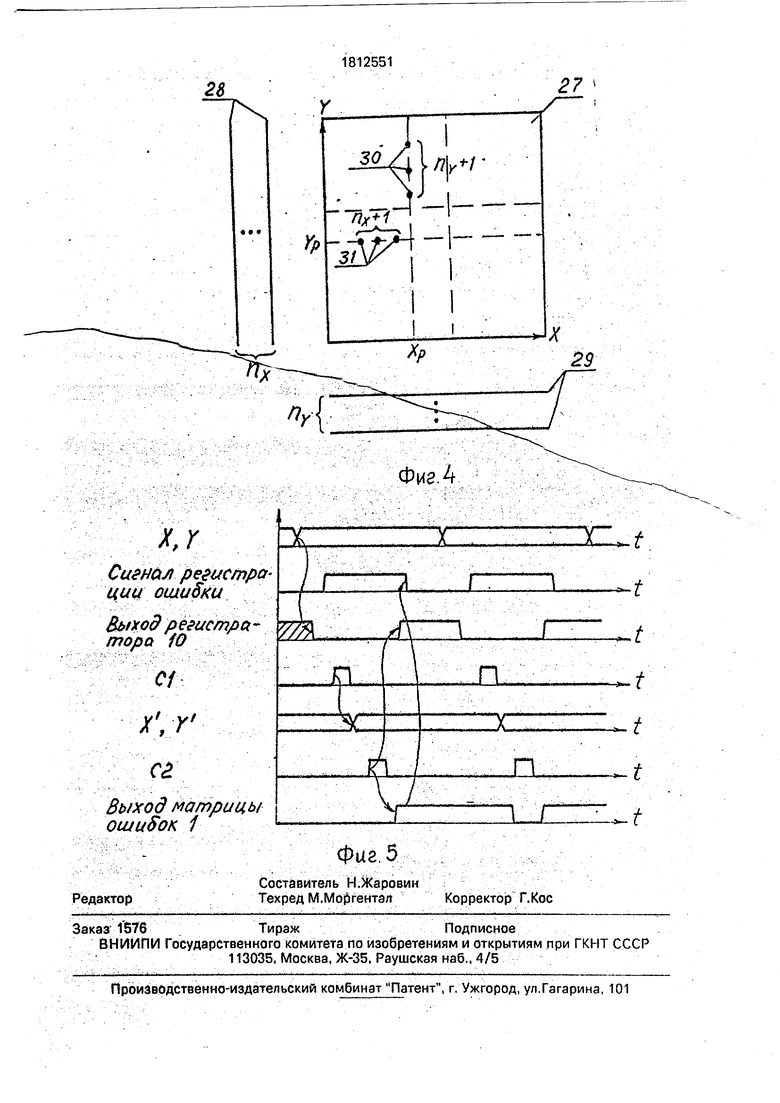

В процессе испытания резервированной памяти каждая обнаруженная ошибка в виде логической единицы поступает на вход ошибки 19 устройства, на входы 13 и 14

5 которого одновременно поступают адресах и Y дефектного элемента.

Первая ошибка формирует на выходе элемента И 8 сигнал регистрации ошибки (см.фиг.5), по которому состояние счетчике

0 11 записывается импульсом С1 в регистратор адреса 12 в обоих блоках 2 и 3. После появления данных на выходах регистраторов 12, импульсом С2 производится регистрация ошибки в блоке памяти ошибок 1 и в

5 регистраторах 10, вычитается единица из содержимого счетчиков 11 блоков 2 . и .3 и счетчиков 4,5. Цепи подачи импульсов С1 и С2 на фиг.1 не показаны. В дальнейшем при поступлении ошибки, адрес X которой сов0 падает с адресом X ранее зарегистрированной ошибки, регистратор дефектных адресов 10 блока 2 сформирует сигнал 1 на своём выходе, запрещающ-иГгзапись новых данных в регистратор адреса 12 и вычи5 тание единицы в счетчике 11. Такая ошибка запишется в блоке памяти ошибок 1 с тем же адресом X, что и ранее зарегистрированная ошибка. Аналогично происходит в блоке 3 при совпадении адреса Y ошибки.

0 Если в строке зарегистрировано пу-И ошибок, то при каждом последующем появлении ошибки с таким же адресом X на выходе счетчика 4 будет формироваться единица, запрещающая прохождение .сиг5 нала ошибки на выход элемента И 8. Этим исключаете регистрация избыточных ошибок Б строке. Аналогично исключаются избыточные ошибки в столбце сигналом счётчика 5. ; .

0 Повторное появление ошибки с тем же адресом (X, Y) не должно изменять состояние счетчиков 4 и 5. Это достигается блокировкой сигнала-ошибки на входе элемента И 8 сигналом ч 1, поступающим с выхода

5 блока памяти ошибок 1.

Для обеспечения надежности регистрации ошибок сигнал на входах регистрации блока памяти ошибок 1, счетчиков 4,5, регистраторов 10 и счетчиков 11 должен сохранять постоянство до окончания действия

импульса С2. Если реальные задержки сигналов на выходах блока памяти ошибок 1, счетчиков 4,5 и элемента И 8 не обеспечивают выполнение этого условия, на выходе элемента И 8 необходимо включить элемент задержки (на фиг.1 показан штриховой линией).

Как только число дефектных строк превысит значение N, счетчик 11 блока 2 перейдет в состояние -1V Отрицательное состояние счетчика сформирует на выходе компаратора числа дефектных адресов 6 сигнал Г, который через элемент ИЛИ 9 поступит на контрольный выход 18 устройства, сигнализируя о неремонтопригодности контролируемой памяти - Брак. Аналогично формируется сигнал Брак с помощью компаратора 7 при превышении числа дефектных адресов значения N в счетчике 11 блокаЗ.

При положительном завершении контроля блок памяти ошибок содержит все ошибки, исключая избыточные, взаимное относительное расположение которых пол- ностью соответствует расположению дефектных запоминающих элементов 6 основном поле резервированной памяти. Адреса ошибок X ti Y в блоке памяти ошибок взаимно . соответствуют адресам X и Y дефектных элементов памяти. Такое соответствие зафиксировано в памяти регистраторов адреса 12. Этих данных достаточно для однозначного определения ремонтоп- ригодносш и способа ремонта резервированной памяти,

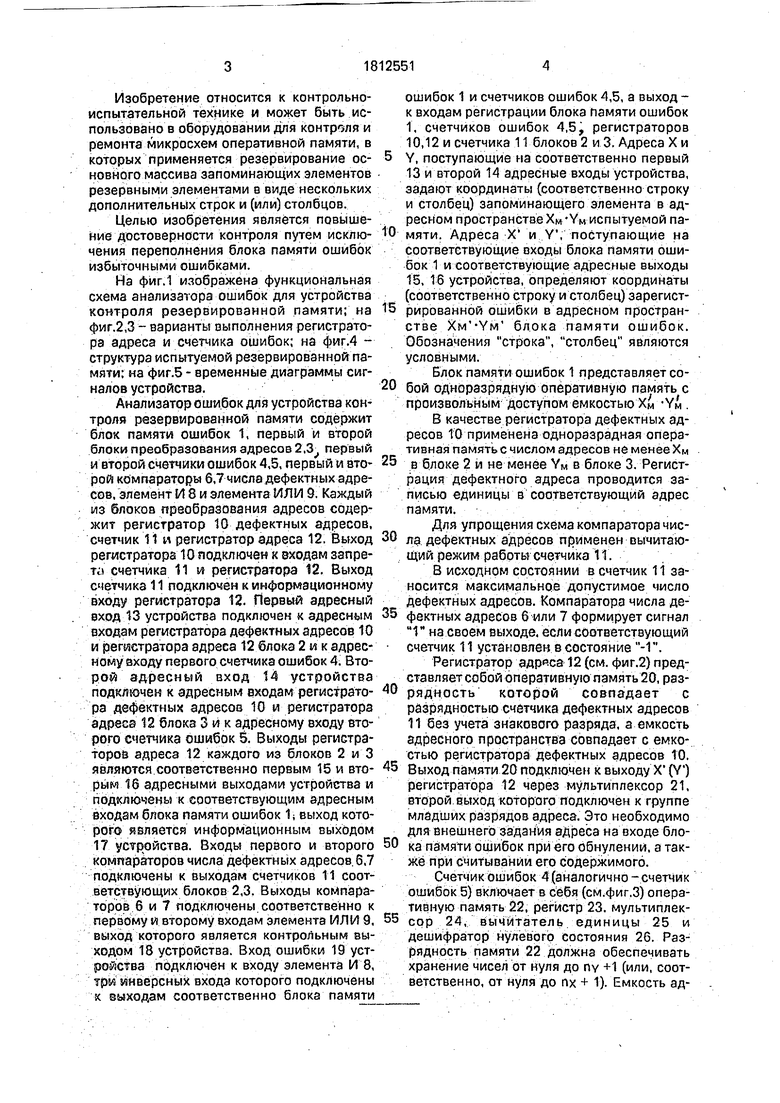

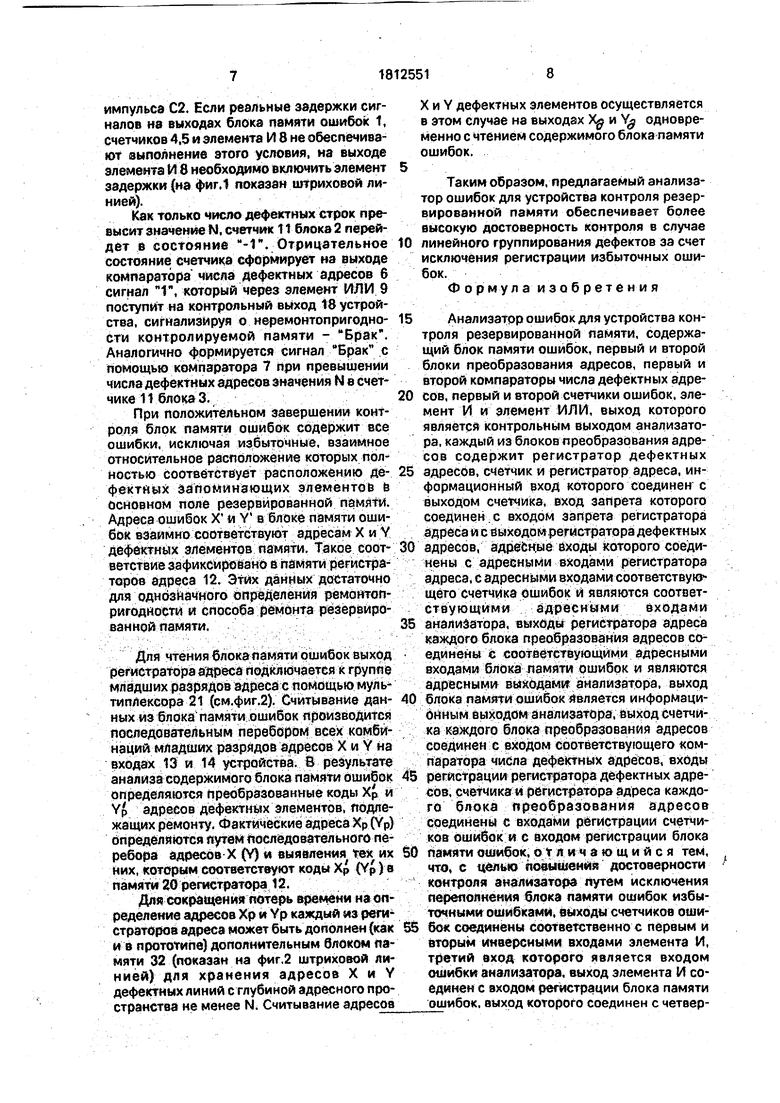

Для чтения блока памяти ошибок выход регистратора адреса подкякзчйетея к группе младших разрядов адреса с помощью мультиплексора 21 (см.фиг.2). Считывание данных из блока памяти ошибок производится последовательным перебором всех комбинаций младших разрядов адресов X и Y на входах 13 и 14 устройства;JS результате анализа содержимого блока памяти ошибок определяются преобразованные коды Хр и Yp адресов дефектных элементов, подлежащих ремонту. Фактические адреса Хр (Yp) определяются путем последовательного перебора адресов X (Y) и выявления тех их них, которым соответствуют коды Хр (Yp) в памяти 20 регистратора 12.

Для сокращения потерь времени на определение адресов Хр и Yp каждый из реги страторов адреса может быть дополнен (как ив прототипе) дополнительным блоком памяти 32 (показан на фиг.2 штриховой линией) для хранения адресов X и Y дефектных линий с глубиной адресного пространства не менее N. Считывание адресов

X и Y дефектных элементов осуществляется в этом случае на выходах Xg. и Y одновременно с чтением содержимого блока памяти ошибок.

. ...

Таким образом, предлагаемый анализатор ошибок для устройства контроля резервированной памяти обеспечивает более высокую достоверность контроля в случае

линейного группирования дефектов за счет исключения регистрации избыточных ошибок.

Формула изобретения

Анализатор ошибок для устройства контроля резервированной памяти, содержащий блок памяти ошибок, первый и второй блоки преобразования адресов, первый и второй компараторы числа дефектных адресов, первый и второй счетчики ошибок, элемент И и элемент ИЛИ, выход которого является контрольным выходом анализатора, каждый из блоков преобразования адресов содержит регистратор дефектных

адресов, счетчик и регистратор адреса, информационный вход которого соединен с выходом счетчика, вход запрета которого соединен с входом запрета регистратора адреса и с быходомрегистратора дефектных

адресов, адреьные входы которого соединены с адресными входами регистратора адреса, с адресными входами соответствую щёто счетчика ошибок и являются соответствующими адресными входами

анализатора, выходы регистратора адреса каждого блока преобразования адресов соединены с соответствующими адресными входами блока памяти ошибок и являются адресными выходами1 анализатора, выход

блока памяти ошибок является информационным выходом анализатора, выход счетчика каждого блокапреобразования адресов соединен с входом соответствующего компаратора числа дефектных адресов, входы

регистрации регистратора дефектных адресов, счетчика и регистратора адреса каждого блока преобразования адресов соединены с входами регистрации счетчиков Ошибок и с входом регистрации блока

памяти ошибок, о т л и ч а ю щ и и с я тем, что, с целью повышения достоверности контроля анализатора путем исключения переполнения блока памяти ошибок избыточными ошибками, выходы счетчиков ошибок соединены соответственно с первым и вторым инверсными входами элемента И, третий вход которого является входом ошибки анализатора, выход элемента И соединен с входом регистрации блока памяти ошибок, выход которого соединен с четвертым инверсным входом элемента И, выходы компараторов числа дефектных адресов

подключены соответственно к первому и второму входам элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1985 |

|

SU1370668A1 |

| Устройство для измерения координатных искажений фокусирующе-отклоняющей системы и передающей электронно-лучевой трубки | 1989 |

|

SU1660212A1 |

| Запоминающее устройство с резервированием | 1989 |

|

SU1674252A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Устройство для формирования плана проходимости местности перед транспортным средством | 1988 |

|

SU1562933A1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для выбора адреса в резервированном блоке памяти | 1985 |

|

SU1317478A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

Фиг.З

2в

27

Фиг Л

Авторы

Даты

1993-04-30—Публикация

1990-02-09—Подача