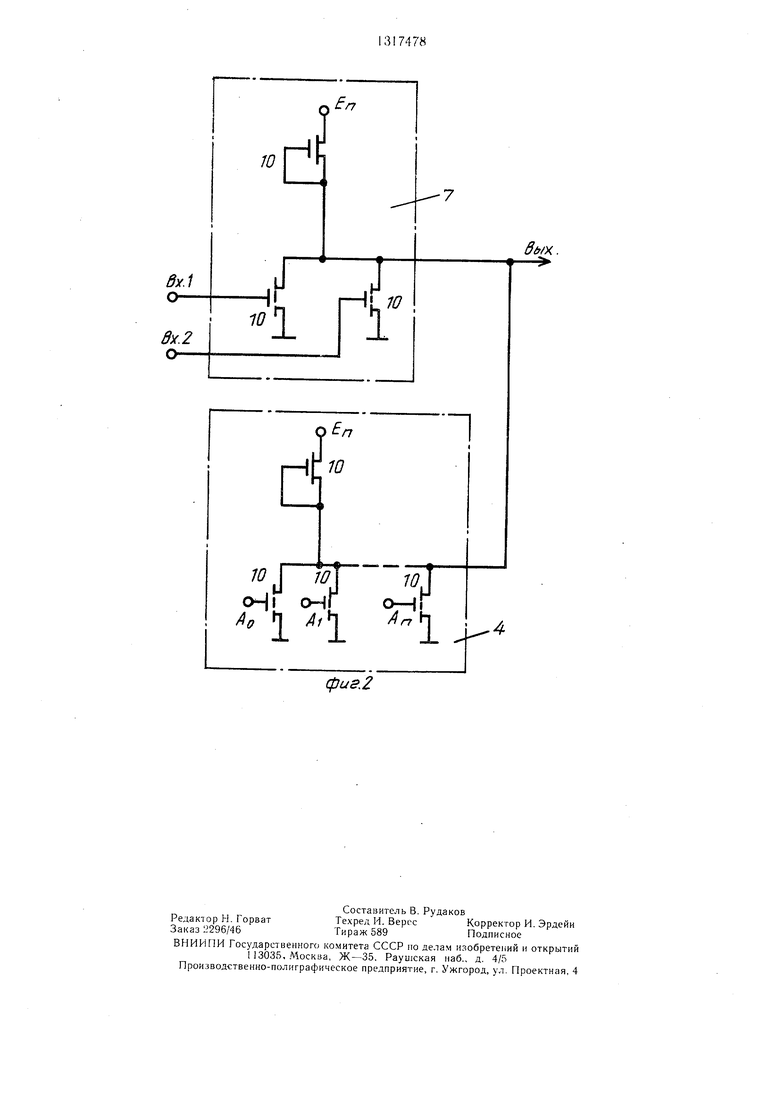

Физ. 1

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств с резервированием.

Цель изобретения - повь шение быстродействия устройства.

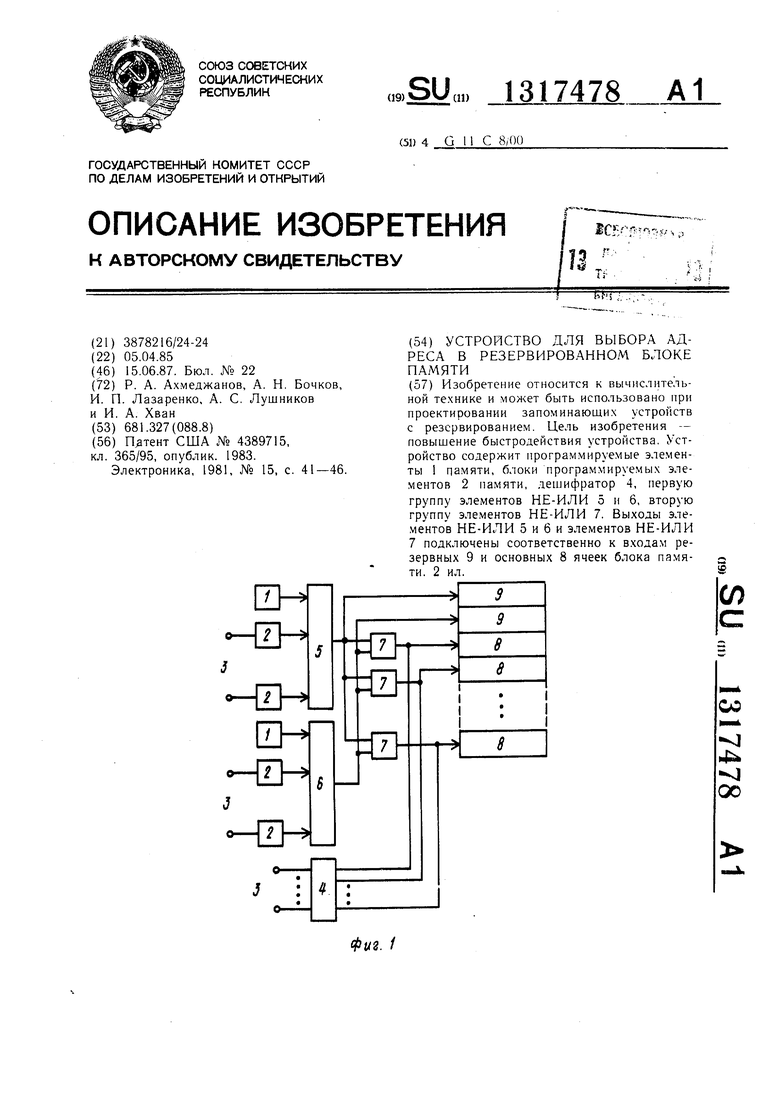

На фиг. 1 изображена структурная схема устройства для выбора адреса в резервированном блоке памяти; на фиг. 2 - принципиальная схема, показывающая соединение выходов элементов НЕ-ИЛИ и выходных элементов дещифратора.

Устройство содержит (фиг. 1) программируемые элементы 1 памяти, блоки программируемых элементов 2 памяти, имеющие входы 3, дещифратор 4, первую группу элементов НЕ-ИЛИ 5 и 6, вторую группу элементов НЕ-ИЛИ 7. На фиг. 1 также изображен резервированный блок памяти, состоящий .из основных 8 и резервных 9 ячеек памяти, образующих строки блока памяти. Основные и резервные выходы устройства для выбора адреса подключаются к адресным входам ячеек 8 и 9 соответственно.

Элементы НЕ-ИЛИ 7 и дещифратор 4 выполнены на МДП-транзисторах 10 со встроенным и с индуцированным каналами (фиг. 2).

Параметры транзисторов 10, входящих в состав элементов НЕ-ИЛИ 7 и дещифратора 4, подобраны таким образом, чтобы обеспечить получение нормальных величин логичнских уровней на выходе. Если на выходе хотя бы одного из указанных блоков 4 и 7 устанавливается логический ноль, то на выходе другого блока также принудительно устанавливается логический нуль.

Устройство работает следующим образом.

В исходном состоянии программируемые элементы 1 и 2 памяти не запрограммированы, на выходе програм.мируемых элементов 1 - логическая единица, элементы НЕ- ИЛИ 5 и 6 заблокированы, на их выходе - логический нуль. При обращении к блоку памяти состояние на выходе программируемых элементов 2 памяти соответствует состоянию на их адресном входе А. Поскольку элементы НЕ-ИЛЙ 5 и 6 заблокированы, осуществляется выборка основной ячейки 8 в соответствии с адресом на входе устройства. Логическая единица поступает на выход дещифратора 4, соответствующий комбинации входных адресных сигналов, а на все остальные выходы дешифратора 4 поступают логические нули. При контроле блока памяти

возможно обнаружение неисправных ячеек памяти. Дефектные ячейки памяти могут быть заменены годными резервными ячейками с помощью программирования программируемых элементов 1 и 2 памяти. При этом на выходе программируемого элемента 1 устанавливается логический нуль.

Программируются также те программируемые эле.менты 2 памяти, которые при выбранном адресе дефектной ячейки памяти имеют на адресном входе, логическую единицу. У данных элементов в результате нрограм.мирования состояние на выходе соответствует инверсному входному адресу. Программируемые элементы 2, у которых

5 на адресном входе лог ический нуль при выбранном адресе дефектной ячейки, своего состояния не изменяют. Таким образом, при обращении по адресу дефектной ячейки у запрограммированного блока памяти на выходах программируемых элементов 2 -

логический нуль, а на вы.чоде соответствующего эле.мента 5 или 6 - логическая единица, которая возбуждает резервную ячейку 9 и поступает на входы всех элементов НЕ-ИЛИ 7. В результате на все основные

5 ячейки 8 поступает логический нуль.

Формула изобретения

Устройство для выбора адреса в резервированном блоке памяти, содержащее нер- 0 зую группу элементов , дешифратор, программируемые э. 1еме 1ты па.мяти, блоки программируемых элементов памяти, выходы которых подключены к одним из входов соответствующих элементов HEi-ИЛИ первой группы, другие входы которых соединены с выходами соответствующих программируемых элементов памяти, входы дещифратора и блоков ф01 раммируе.мых элементов памяти являются входами устройства, выходы дешифратора и элементов НЕ0 ИЛИ первой группы являются соответственно основными и резервными выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введена вторая группа эле.ментов НЕ., ИЛИ, первые входы которых объединены и подключены к выходу одного элемента НЕ-ИЛИ первой группы, вторые входы элементов НЕ-ИЛИ вто.)ой грушп, объединены и подключены к выходу дру| ого э.чемеп- та НЕ-ИЛИ первой группы, выходы элемен0 тов НЕ-ИЛИ второй группы соединены с соответствующими вь: хода ми деп1ифратора.

(pus.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор для запоминающего устройства с резервированием | 1986 |

|

SU1429166A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Формирователь адреса | 1984 |

|

SU1265853A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| Запоминающее устройство с резервированием | 1989 |

|

SU1674252A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

Изобретение относится к вычислительной те.хнике и может быть использовано ири проектировании запоминающих устройств с резервированием. Цель изобретения - повышение быстродействия устройства. Устройство содержит программируемые элементы 1 памяти, блоки программируемых элементов 2 памяти, дешифратор 4, первую группу элементов НЕ-ИЛИ 5 и 6, вторую группу элементов НЕ-ИЛИ 7. Выходы элементов НЕ-ИЛИ 5 и 6 и элементов НЕ-ИЛИ 7 подключены соответственно к в.ходам резервных 9 и основных 8 ячеек блока памяти. 2 ил. ел С 6 - со 4 00

| П атент США № 4389715, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Электроника, 1981, № 15, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-15—Публикация

1985-04-05—Подача