Изобретение относится к вычислительной технике и может быть использовано как средство автоматизации при ограниченном энергопотреблении в случаях, не требующих высокого быстродействия запросов на обслуживание.

Цель изобретения - снижение энергопотребления микроЭВМ за счет использования векторных прерываний для включения и выключения питания микро- ЭВМ, что позволяет создать такие условия эксплуатации микроЭВМ, при которых она потребляет энергию лишь в течение времени, необходимого для выполнения задачи.

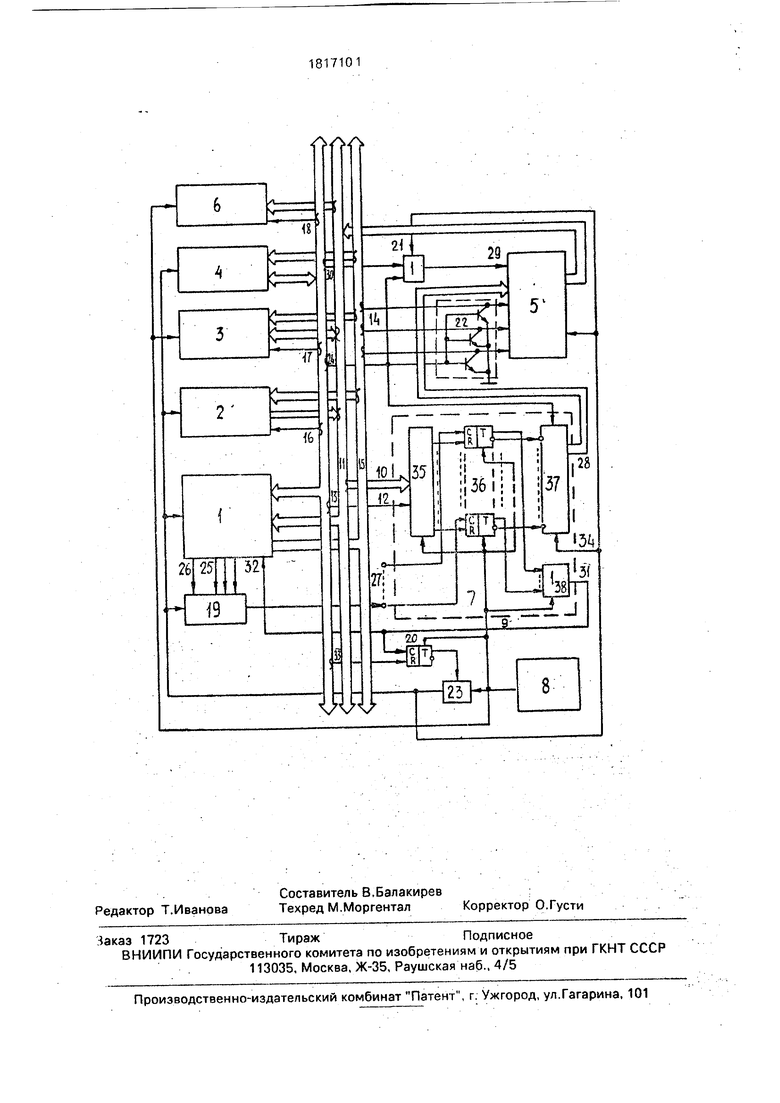

На чертеже представлена функциональная схема микроЭВМ.

МикроЭВМ содержит процессор 1, блок 2-постоянной памяти, блок 3 оперативной

памяти, контроллер 4 шины, порты 5 ввода, порты 6 вывода, контроллер 7 прерываний, источник 8 питающего напряжения, выход которого подключен к входам питающего напряжения блока 3 оперативной памяти, портов 6 вывода и к первому входу 9 питающего напряжения контроллера 7 прерываний. При этом входы 10 данных контроллера 7 прерываний подключены к шине 11 данных, вход 12 разрешения сброса запросов контроллера 7 прерываний соединен с первым выходом 13 контроллера 4 шины, входы адреса портов 5 ввода подключены к младшим разрядам 14 шины 15 адреса, входы адреса блока 2 постоянной памяти соединены с шиной 15 адреса, выходы данных блока 2 постоянной памяти соединены с шиной 11 данных, вход выборки блока 2 постоянной

00

о

памяти соединен с вторым выходом 16 контроллера 4 шины, входы адреса блока 3 оперативной памяти соединены с шиной 15 адреса, входы-выходы данных блока 3 оперативной памяти соединены с шиной 11 данных, вход 17 выборки блока 3 оперативной памяти подключен к третьему выходу контроллера 4 шины, входы адреса которого подключены к шине адреса, входы данных портов вывода соединены с шиной 11 данных, входы 18 выборки портов 6 вывода подключены к четвертому выходу контроллера 4 шины. МикроЭВМ содержит также схему 19 совпадения, триггер 20, элемент 21 ИЛИ, первый и второй ключи 22, 23 соответственно. Управляющий вход первого ключа 22 подключен к выходу 24 разрешения прерывания процессора 1, выходы первого ключа 22 подключены к входам адреса портов 5 ввода, информационный вход первого ключа 22 подключен к шине нулевого потенциала. Первый, второй, третий входы схемы 19 совпадения подключены соответственно к выходам25 состояния процессора 1 .четвертый вход схемы 19 совпадения подключен к выходу 26 тактовой частоты процессора 1. Выход схемы 19 совпадения подключен к входу 27 запроса прерывания контроллера 7 прерываний, выход 28 адреса вектора прерывания контроллера 7 прерываний подключен к входам адреса вектора прерывания портов 5 ввода. Вход 29 разрешения ввода портов 5 ввода подключен к выходу элемента 21 ИЛИ, первый вход элемента 21 ИЛИ подключен к пятому выходу

30 контроллера 4 шины, второй вход элемента 21 ИЛИ подключен к выходу 24 разрешения прерывания процессора 1. Выход

31 запроса прерываний контроллера 7 прерываний подключен к входу синхронизации триггера 20 и входу 32 запроса прерываний процессора 1. Вход сброса триггера 20 подключен к шестому выходу 33 контроллера 4 шины, прямой выход триггера 20 подключен к управляющему входу второго ключа 23, информационный вход которого подключен к выходу источника 8 питающего напряжения, а выход - к входам питающего напряжения процессора 1, схемы 19 совпадения, блока 2 постоянной памяти, контроллера 4 шины, портов 5 ввода, элемента 21 ИЛИ и второму входу 34 питающего напряжения контроллера 7 прерываний. Выход источника 8 питающего напряжения подключен к входу питающего напряжения триггера 20. Контроллер 7 прерываний содержит мультиплексор 35, группу из п триггеров 36, где п - число зарезервированных аппаратных прерываний процессора 1, шифратор 37 и элемент 38 ИЛИ. Управляющий вход

мультиплексора 35 подключен к входу 12 разрешения сброса запросов прерываний контроллера 7 прерываний. Входы данных мультиплексора 35 подключены к входам

данных контроллера 7 прерываний, выходы данных мультиплексора 35 подключены соответственно к входам сброса гг триггеров 36, прямые выходы которых подключены соответственно к входам элемента 38 ИЛИ,

выход которого является выходом 31 запроса прерывания контроллера 7 прерываний. Инверсные выходы п триггеров 36 подключены к инверсным входам шифратора 37, выход шифратора 37 является выходом 28

адреса вектрра прерывания контроллера 7 прерываний, Входы питающего напряжения элемента 38 ИЛИ, п триггеров 36, мультиплексора 36 подключены к первому входу 9 питающего напряжения контроллера 7

прерываний. Вход питающего напряжения шифратора 37 подключен к второму входу 34 питающего напряжения контроллера 7 прерываний.

МикроЭВМ работает следующим образом. ,:.; ;/ .

При включении источника 8 питающего напряжения под его действием оказываются блок 3 оперативной памяти, порты 6 вывода, триггер 20 и некоторые схемы контроллера 7 прерываний: мультиплексор 35, группа из п триггеров 36 и элемент 38 ИЛИ. Перечисленные элементы контроллера 7 прерываний поддерживают дежурный

режим работы микроЭВМ, при котором потребляется от источника 8 питающего напряжения минимум энергии; При воздействии сигнала на один из входов 27 запроса прерывания (например, с клавиатуры консоли) соответствующий триггер из группы п триггеров 36 устанавливается в единичное состояние. Состояние каждого триггера 36 фиксируется входами элемента 38 или контроллера 7 прерываний, на выходе 31 которого появляется положительный сигнал, включающий триггер 20 и воздействующий на вход 32 запроса прерывания процессора 1. На выходе триггера 20 устанавливается положительный сигнал, по которому замыкается второй ключ 23, коммутирующий временное питающее напряжение. На выходе ключа 23 появляется питающее напряжение, которое подается на процессор 1, блок 2 постоянной памяти,

контроллер 4 шины, порты 5 ввода, схему 19 совпадения и шифратор 37 контроллера 7 прерываний. Процессор 1, последовательно выбирая команды из блока 2 постоянной памяти, проходит процесс инициализации MJ достигая выполнения команды разрешения прерывания, начинает реагировать на прерывание, пришедшее с выхода 31 элемента 38 ИЛИ контроллера 7 прерываний. Сигнал с выхода 24 разрешения прерывания процессора 1 приходит на первый ключ 22, который открывается и замыкает на земляной потенциал входы адреса портов 5 ввода, тем самым устанавливая порт с адре- сомФфФ Н, Сигналы с инверсных выходов триггеров 36 контроллера 7 прерываний поступают на инверсные входы шифратора 37 контроллера 7 прерываний, на выходе 28 которого появляется преобразованный из десятичного в двоичный код, поступающий на вход порта 5 ввода, отведенный для прерываний с адресом Н. Этот код представляет собой адрес вектора прерываний, который с приходом с выхода 24 сигнала разрешения прерывания через элемент 21 ИЛИ на вход 29 разрешения ввода портов 5 ввода передается по шине 11 данных в процессор 1. Таким образом, получив информацию о прерывании, процессор 1 уходит на выполнение программы, соответствующей вызванному прерыванию, которая в нужное время через мультиплексор 35 контроллера 7 прерываний сбрасывает ненужные ей триггеры 36 контроллера 7 прерываний. Для этого на шине 11 данных устанавливается соответствующий код, и с приходом сигнала по линии 13 разрешения сброса запросов на прерывание этот код с выходом мультиплексора 35 контроллера 7 прерываний поступает на входы сброса группы п триггеров 36. Окончив выполнение программы обслуживания прерывания, процессор 1 выполняет команду, останова, которая распознается схемой 19 совпадения по трем выходам 25 состояния процессора 1 и выходе 26 тактовой частоты процессора 1. При этом на выходе схемы 19 совпадения возникает положительный импульс, который устанавливает по соответствующей линии запроса прерывания соответствующий триггер из п триггеров 36 контроллера 7 прерываний, на выходе 31 элемента 38 ИЛИ контроллера 7 прерываний возникает сигнал прерывания, на который опять должен реагировать процессор 1. Процесс ввода адреса прерывания повторяется аналогичным образом, Отрабатывая прерывание по команде останова, процессор 1 формирует в блоке 3 оперативной памяти таблицу значений текущего состояния своих внутренних регистров, которые были в момент останова процессора 1, чтобы при следующей инициализации восстановить их, опять сбрасывает уже рассмотренным способом триггеры 36 контроллера 7 прерываний и по выходному сигналу 33 управления разрешения сброса триггера 20 устанавливает триггер 20 а нулевое состояние. Нз выходе триггера 20 появляегся сигнал нуля, «торой ключ 23 размыкается, и с его выхода снимается времен- 5 ное питающее напряжение, обесточивая тем самым устройства, которые не являются энергозависимыми (процессор 1, блок 2 оперативной памяти, контроллер 4 шины. схема 19 совпадения, порты 5 ввода, эле- 0 мент 21 ИЛИ. шифратор 37 контроллера 7 прерываний).

Для реализации Функционирования аппаратных средств, позволяющих выполнять режим понижения энергопотребления мик5 роЭВМ, необходимо соответственное программное обеспечение, которое бы своим алгоритмом поддерживало этот способ экономии энергопотребления.

Введение таких аппаратных средств в

0 микроЭВМ, как схема .19 совпадения, которая может быть выполнена вызывающей прерывание по команде останова, позволяет применять существующее программное обеспечение, не прибегая к его адаптации

5 под архитектуру микроЭВМ, что является преимуществом изобретения, поскольку большинство программ в точке ожидания внешних событий использует именно команду останова.

0Ф о р м у л а и з о б р е т е н и я

1. МикроЭВМ, содержащая процессор, блок постоянной памяти, блок оперативной памяти, контроллер шины, порты ввода, порты вывода, контроллер прерываний, ис5 точник питающего напряжения, выход которого подключен к входам питающего напряжения блока оперативной памяти, портов вывода и к первому входу питающего напряжения контроллера прерываний,

0 входы данных контроллера прерываний подключены к шине данных, вход разрешения сброса запросов контроллера прерываний соединен с первым выходом контроллера шины, входы адреса портов

5 ввода подключены к младшим разрядам шины адреса, входы адреса блока постоянной памяти соединены с шиной адреса, выходы данных блока постоянной памяти соединены с шиной данных, вход выборки блока

0 постоянной памяти соединен с вторым выходом контроллера шины, входы адреса блока оперативной памяти соединены с шиной адреса, входы-выходы данных блока оперативной памяти соединены с шиной

5 данных, вход выборки блока оперативной памяти подключен к третьему выходу контроллера шины, входы адреса которого подключены к шине адреса, входы данных портов вывода соединены с шиной данных, входы выборки портов вывода подключены

к четвертому выходу контроллера шины, о т- л и ч а ю щ а я с я тем, что, с целью снижения энергопотребления, в нее введены схема совпадения, триггер, элемент ИЛИ, первый и второй ключи, управляющий вход первого ключа подключен к выходу разрешения прерывания процессора, выходы первого ключа подключены к входам адреса портов ввода, информационный вход первого ключа подключен к шине нулевого потенциала, первый, второй, третий входы схемы совпадения подключены соответственно к выходам состояния процессора, четвертый вход схемы совпадения подключен к выходу тактовой частоты процессора, выход схемы совпадения подключен к входу запроса прерывания контроллера прерываний, выход адреса вектора прерываний контроллера прерываний подключен к входам адреса вектора прерывания портов ввода, входы разрешения ввода портов ввода подключены к выходу элемента ИЛИ, первый вход элемента ИЛИ подключен к пятому выходу контроллера шины, второй вход элемента ИЛИ подключен к выходу разрешения ripeрывания процессора, выход запроса прерываний контроллера прерываний подключён к входу синхронизации триггера и к входу запроса прерываний процессора, вход сброса триггера подключен к шестому выхо- ду контроллера шины, прямой выход триггера подключен к управляющему входу второго ключа, информационный вход которого подключен к выходу источника питающего напряжения, а выход - к входам

питающего напряжения процессора, схемы совпадения, блока постоянной памяти, контроллера шины, портов ввода, элемента ИЛИ и к второму входу питающего напряжения контроллера прерываний, выход источника питающего напряжения подключен к входу питающего напряжения триггера.

2. МикроЭВМ по п.1, о т л и ч а ю щ а я- с я тем, что контроллер прерываний содер жит мультиплексор, группу из п триггеров, где п - число зарезервированных апиарат- ных прерываний процессора, шифратор и элемент ИЛИ, при-этом, управляющий вход мультиплексора подключен к входу разрешения сброса запросов прерываний контроллера прерываний, входы данных мультиплексора подключены к входам данных контроллера прерываний, выходы данных мультиплексора подключены соответственно, к входам сброса п триггеров, прямые выходы которых подключены, соответственно к входам элемента ИЛИ, выход которого является выходом запроса прерываний контроллера прерываний, инверсные выходы п триггеров подключены к инверсным входам шифратора, выход шифратора является выходом адреса вектора прерывания контроллера прерываний, входы питающего напряжения элемента ИЛИ, п дополнительных триггеров, мультиплексор подключены к первому входу питающего напряжения контроллера прерываний, вход питающего напряжения шифратора подключен к второму входу питающего напряжения контроллера прерываний.

-ЛЛ/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

Изобретение относится к вычислительной технике и может быть использовано как средство автоматизации при ограниченном энергопотреблении в случаях, не требующих высокого быстродействия запросов на обслуживание. Целью изобретения является снижение энергопотребления микро- ЭВМ за счет использования векторных прерываний для включения и выключения питания микроЭВМ, что позволяет создать такие условия эксплуатации микроЭВМ, при которых она потребляет энергию лишь в течение времени, необходимого для выполнения задачи. Для этого микроЭВМ содержит процессор, блок постоянной памяти, блок оперативной памяти, контроллер шины, порты ввода, порты вывода, контроллер прерываний, источник питающего напряжения, схему совпадения, триггер, элемент ИЛИ и два ключа. 1 з.п. ф-лы, 1 ил, Ё

| Щелкунов Н.Н., Дианов А.А | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| - Микропроцессорные средства и системы, 1987, № I, с.77-83 | |||

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| М.: Радио и связь, 1986, с.171. | |||

Авторы

Даты

1993-05-23—Публикация

1990-02-22—Подача