Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Цель изобретения - повышение быстродействия устройства.

Новыми существенными признаками заявляемого устройства являются введение группы сумматоров по модулю 2 и связей, отражающих новую организацию взаимодействия между элементами устройства.

Новая организация известных элементов позволяет вести поиск свободных зон как по возрастанию значений кодов их адресов, так и по их убыванию, что позволяет ускорить процесс загрузки памяти максимум в 16 раз.

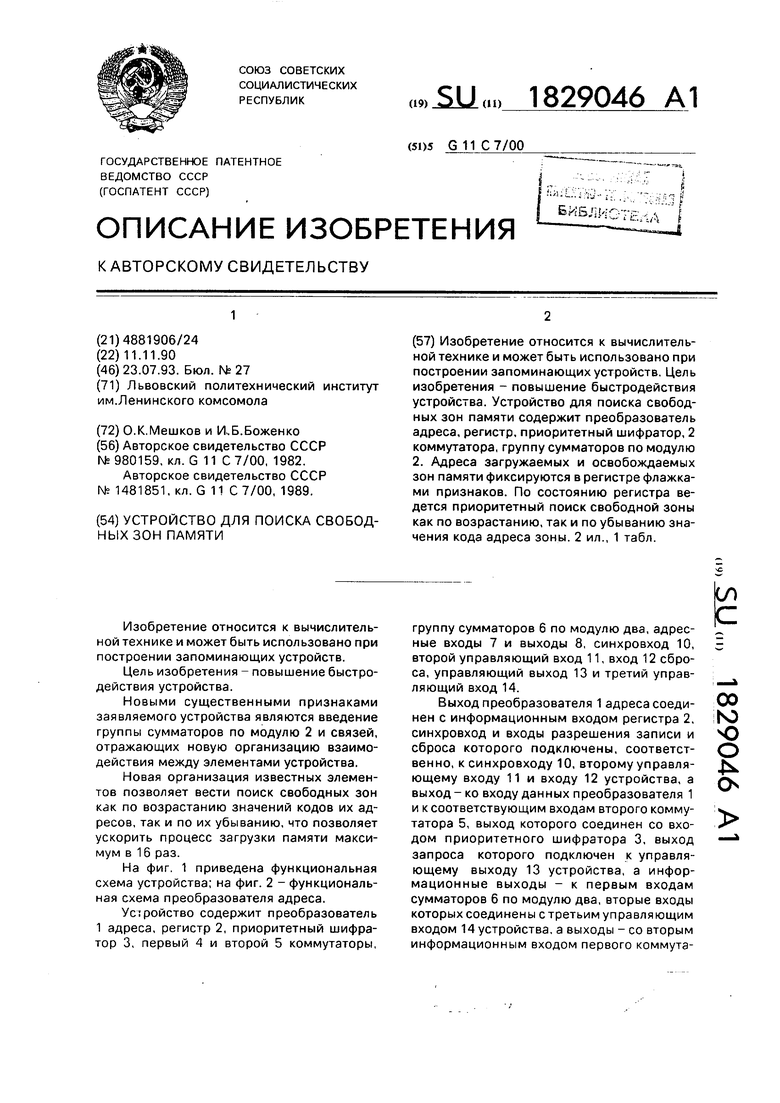

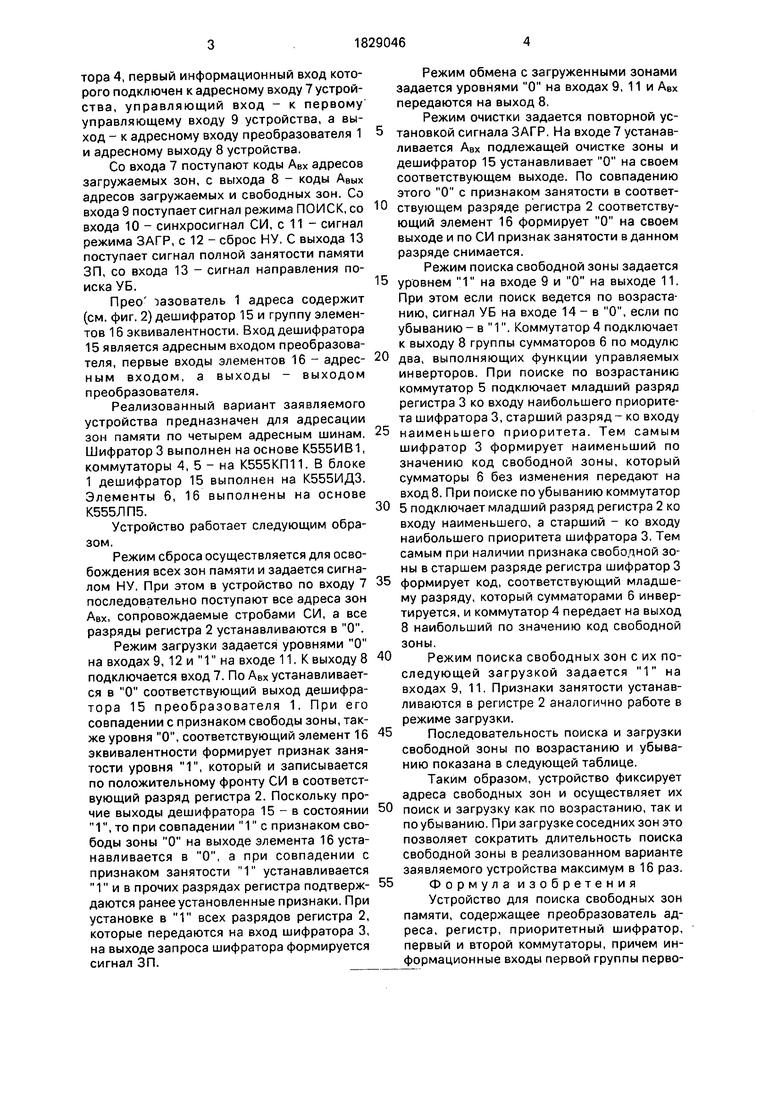

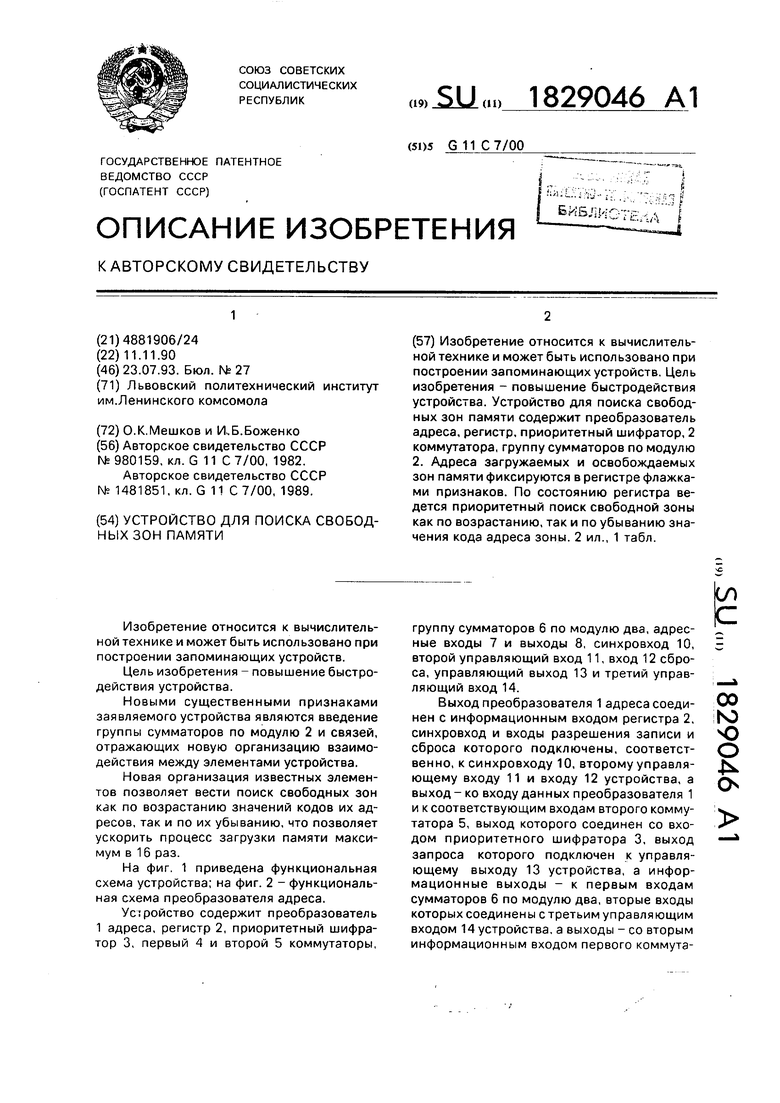

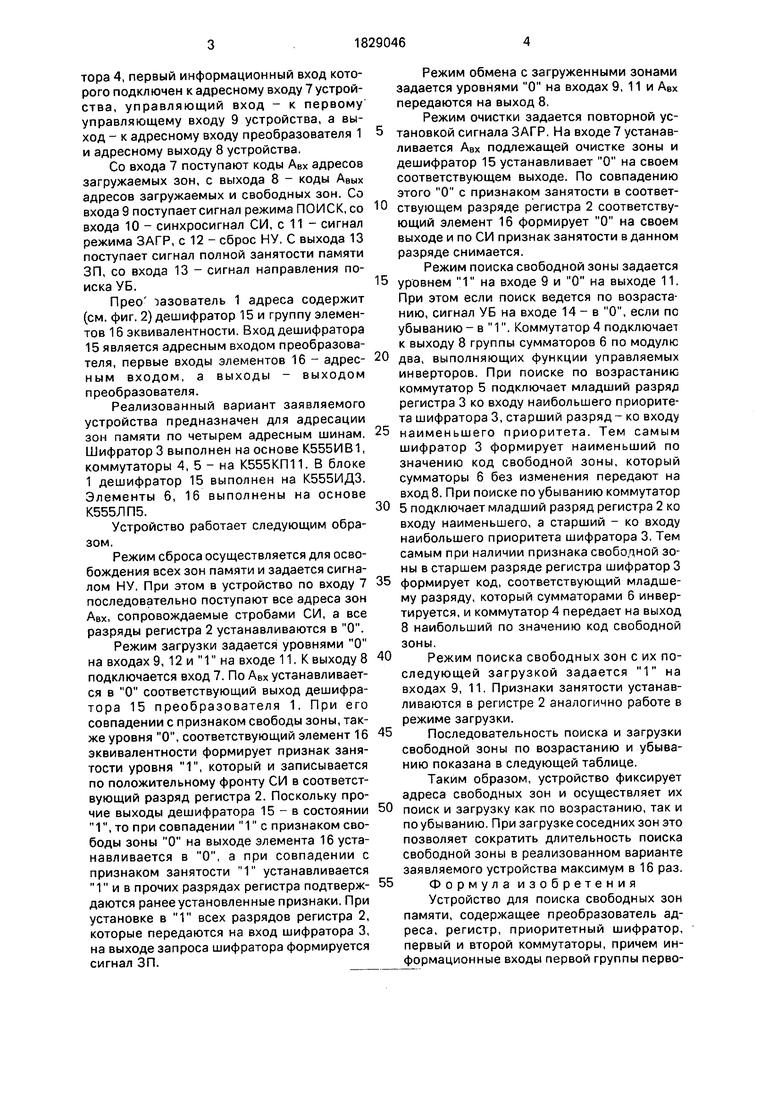

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема преобразователя адреса.

Устройство содержит преобразователь 1 адреса, регистр 2, приоритетный шифратор 3, первый 4 и второй 5 коммутаторы,

группу сумматоров 6 по модулю два, адресные входы 7 и выходы 8, синхровход 10, второй управляющий вход 11, вход 12 сброса, управляющий выход 13 и третий управляющий вход 14.

Выход преобразователя 1 адреса соединен с информационным входом регистра 2, синхровход и входы разрешения записи и сброса которого подключены, соответственно, к синхровходу 10, второму управляющему входу 11 и входу 12 устройства, а выход - ко входу данных преобразователя 1 и к соответствующим входам второго коммутатора 5, выход которого соединен со входом приоритетного шифратора 3, выход запроса которого подключен к управляющему выходу 13 устройства, а информационные выходы - к первым входам сумматоров 6 по модулю два, вторые входы которых соединены с третьим управляющим входом 14 устройства, а выходы - со вторым информационным входом первого коммутаСО

С

00

ю

О О

N О

тора 4, первый информационный вход которого подключен к адресному входу 7 устройства, управляющий вход - к первому управляющему входу 9 устройства, а выход - к адресному входу преобразователя 1 и адресному выходу 8 устройства,

Со входа 7 поступают коды АВх адресов загружаемых зон, с выхода 8 - коды Авых адресов загружаемых и свободных зон. Со входа 9 поступает сигнал режима ПОИСК, со входа 10 - синхросигнал СИ, с 11 - сигнал режима ЗАГР, с 12 - сброс НУ. С выхода 13 поступает сигнал полной занятости памяти ЗП, со входа 13 - сигнал направления поиска УБ.

Прео азователь 1 адреса содержит (см. фиг. 2) дешифратор 15 и группу элементов 16 эквивалентности. Вход дешифратора 15 является адресным входом преобразователя, первые входы элементов 16 - адресным входом, а выходы - выходом преобразователя.

Реализованный вариант заявляемого устройства предназначен для адресации зон памяти по четырем адресным шинам. Шифратор 3 выполнен на основе К555ИВ1, коммутаторы 4, 5 - на К555КП11. В блоке 1 дешифратор 15 выполнен на К555ИДЗ. Элементы 6, 16 выполнены на основе К555ЛП5.

Устройство работает следующим образом.

Режим сброса осуществляется для освобождения всех зон памяти и задается сигналом НУ. При этом в устройство по входу 7 последовательно поступают все адреса зон АВХ, сопровождаемые стробами СИ, а все разряды регистра 2 устанавливаются в О.

Режим загрузки задается уровнями О на входах 9, 12 и 1 на входе 11. К выходу 8 подключается вход 7. По АВх устанавливается в О соответствующий выход дешифратора 15 преобразователя 1. При его совпадении с признаком свободы зоны, также уровня О, соответствующий элемент 16 эквивалентности формирует признак занятости уровня 1, который и записывается по положительному фронту СИ в соответствующий разряд регистра 2. Поскольку прочие выходы дешифратора 15 - в состоянии 1,то при совпадении 1 с признаком свободы зоны О на выходе элемента 16 устанавливается в О, а при совпадении с признаком занятости 1 устанавливается 1 и в прочих разрядах регистра подтверждаются ранее установленные признаки. При установке в 1 всех разрядов регистра 2, которые передаются на вход шифратора 3, на выходе запроса шифратора формируется сигнал ЗП.

Режим обмена с загруженными зонами задается уровнями О на входах 9, 11 и АВх передаются на выход 8,

Режим очистки задается повторной установкой сигнала ЗАГР. На входе 7 устанавливается АВХ подлежащей очистке зоны и дешифратор 15 устанавливает О на своем соответствующем выходе. По совпадению этого О с признаком занятости в соответствующем разряде регистра 2 соответствующий элемент 16 формирует О на своем выходе и по СИ признак занятости в данном разряде снимается.

Режим поиска свободной зоны задается

5 уровнем 1 на входе 9 и О на выходе 11. При этом если поиск ведется по возрастанию, сигнал УБ на входе 14 - в О, если по убыванию - в 1. Коммутатор 4 подключает к выходу 8 группы сумматоров 6 по модулю

0 два, выполняющих функции управляемых инверторов. При поиске по возрастанию коммутатор 5 подключает младший разряд регистра 3 ко входу наибольшего приоритета шифратора 3, старший разряд - ко входу

5 наименьшего приоритета. Тем самым шифратор 3 формирует наименьший по значению код свободной зоны, который сумматоры 6 без изменения передают на вход 8. При поиске по убыванию коммутатор

0 5 подключает младший разряд регистра 2 ко входу наименьшего, а старший - ко входу наибольшего приоритета шифратора 3. Тем самым при наличии признака свободной зоны в старшем разряде регистра шифратор 3

5 формирует код, соответствующий младшему разряду, который сумматорами 6 инвертируется, и коммутатор 4 передает на выход 8 наибольший по значению код свободной зоны.

0 Режим поиска свободных зон с их последующей загрузкой задается 1 на входах 9, 11. Признаки занятости устанавливаются в регистре 2 аналогично работе в режиме загрузки.

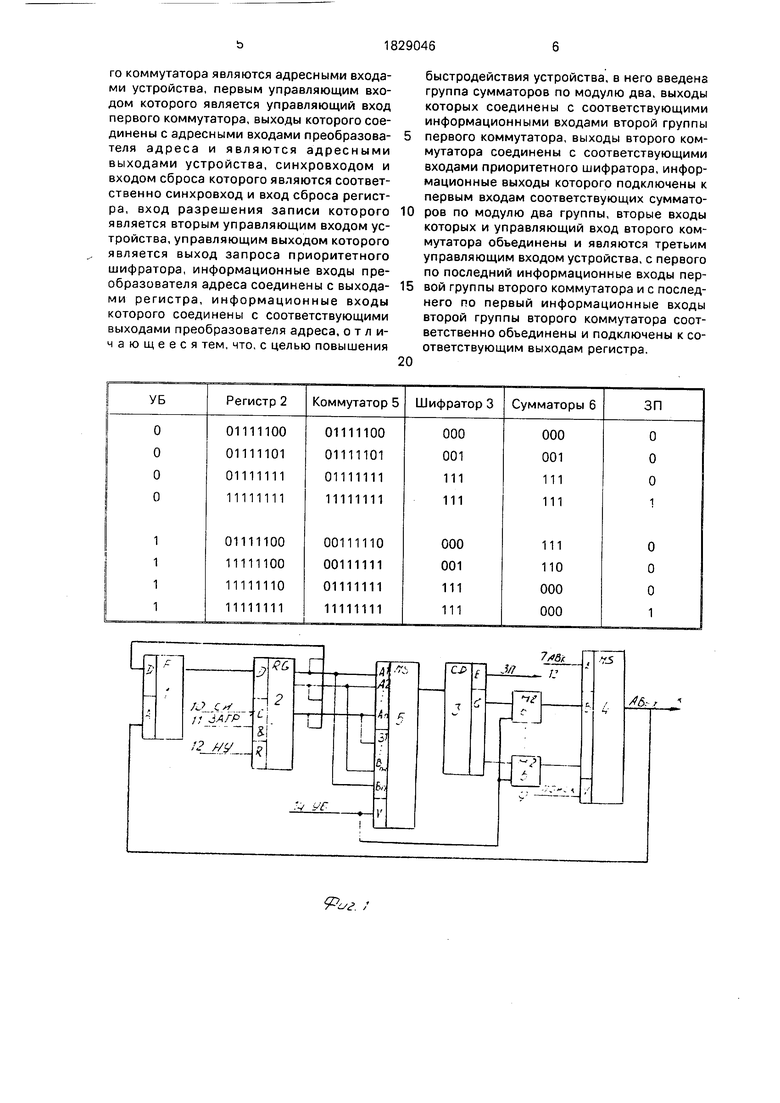

5Последовательность поиска и загрузки

свободной зоны по возрастанию и убыванию показана в следующей таблице.

Таким образом, устройство фиксирует адреса свободных зон и осуществляет их

0 поиск и загрузку как по возрастанию, так и по убыванию. При загрузке соседних зон это позволяет сократить длительность поиска свободной зоны в реализованном варианте заявляемого устройства максимум в 16 раз.

5 Формула изобретения

Устройство для поиска свободных зон памяти, содержащее преобразователь адреса, регистр, приоритетный шифратор, первый и второй коммутаторы, причем информационные входы первой группы первого коммутатора являются адресными входами устройства, первым управляющим входом которого является управляющий вход первого коммутатора, выходы которого соединены с адресными входами преобразователя адреса и являются адресными выходами устройства, синхровходом и входом сброса которого являются соответственно синхровход и вход сброса регистра, вход разрешения записи которого является вторым управляющим входом устройства, управляющим выходом которого является выход запроса приоритетного шифратора, информационные входы преобразователя адреса соединены с выходами регистра, информационные входы которого соединены с соответствующими выходами преобразователя адреса, отличающееся тем, что, с целью повышения

быстродействия устройства, в него введена группа сумматоров по модулю два, выходы которых соединены с соответствующими информационными входами второй группы

первого коммутатора, выходы второго коммутатора соединены с соответствующими входами приоритетного шифратора, информационные выходы которого подключены к первым входам соответствующих сумматоров по модулю два группы, вторые входы которых и управляющий вход второго коммутатора объединены и являются третьим управляющим входом устройства, с первого по последний информационные входы первой группы второго коммутатора и с последнего по первый информационные входы второй группы второго коммутатора соответственно объединены и подключены к соответствующим выходам регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1990 |

|

SU1805472A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для поиска свободных зон памяти | 1987 |

|

SU1481851A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для ввода информации | 1990 |

|

SU1756877A1 |

| Устройство для сортировки данных | 1989 |

|

SU1695290A1 |

| Устройство для сортировки данных | 1990 |

|

SU1784967A1 |

| Устройство для управления обменом | 1988 |

|

SU1667086A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Устройство для поиска свободных зон памяти содержит преобразователь адреса, регистр, приоритетный шифратор, 2 коммутатора, группу сумматоров по модулю 2. Адреса загружаемых и освобождаемых зон памяти фиксируются в регистре флажками признаков. По состоянию регистра ведется приоритетный поиск свободной зоны как по возрастанию, так и по убыванию значения кода адреса зоны. 2 ил., 1 табл.

Фиг. ;

/с- 2

| Устройство для выбора свободных зон в памяти | 1981 |

|

SU980159A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для поиска свободных зон памяти | 1987 |

|

SU1481851A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-07-23—Публикация

1990-11-11—Подача